## **1** General description

The ASL5xxxyHz family is a fully featured and flexible Matrix LED Controller (MLC). It provides a cost effective design solution, specifically targeting advanced automotive exterior lighting applications. The family consists of part numbers with different maximum currents and different driving modes, Smart and direct PWM.

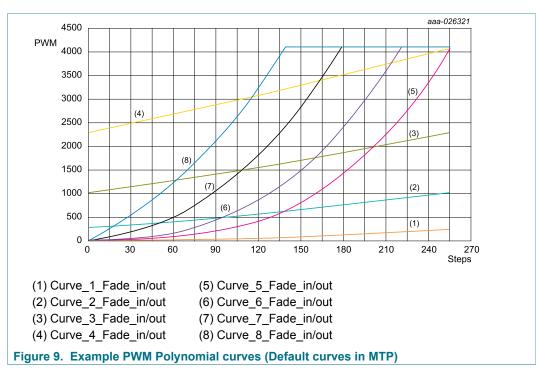

Smart PWM part numbers determine PWM dimming duty cycle from information stored inside the MLC in the form of dimming polynomial curve coefficients. These coefficients are programmable by the customer according to the dimming profile they would like to see. The MLC uses these polynomial coefficients to calculate the PWM duty cycle to 12-bit resolution. The MLC also provides the capability to increase the speed of the PWM dimming curve dynamically or sequence several PWM dimming curves together.

It is possible to store polynomials for up to eight PWM dimming curves. By storing these polynomial coefficients internally, it is not necessary for the microcontroller to send updated PWM dimming information to each LED switch continuously. Instead, the microcontroller selects the PWM curve and LED to which it must be applied. Therefore, the PWM dimming information from the microcontroller is reduced, which reduces the volume of data transfer from the microcontroller to the MLC.

The MLC also provides the functionality to correct for LED brightness variations. This feature is especially useful to ensure a homogenous light output from LEDs that have luminance variations with the same LED current.

The MLC has many diagnostic features, including:

- Direct NTC feedback for monitoring the LED temperature

- Direct identification resistor input for PCB characterization

- · Single LED open/short detection and protection

- Internal IC junction temperature monitoring

- Power-on-Reset (POR) monitoring; mandatory for off-board configuration and following safety requirements

- Power OK bit (POK) to ensure that the complete MLC is working as expected

- External components (NTC, ID resistor, charge pump capacitor) monitoring and fail detection

- · Full communication diagnosis, including flagging illegal actions

- Possibility to clear Open Circuit (OC) and Short Circuit (SC) flags and reset the internal mosfets dynamically and without a need of a power-on-reset

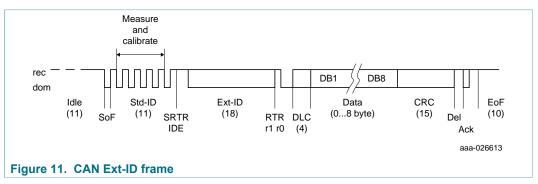

All this diagnostic information is available to the microcontroller via the MLC interface. A microcontroller controls the MLC through a high-speed serial CAN interface. Through this interface, the microcontroller can control up to 32 MLCs, enabling control of up to 384 LEDs or segments.

The MLC has an internal 200 MHz oscillator that avoids the need of an external quartz (reducing system cost and providing better EMC behavior) for synchronization and clock

generation. All the internal clocks are synchronized with the internal oscillator and the trimming is done via the CAN message (CAN-ID). This process allows for a very accurate clock (accuracy < 0.25 %).

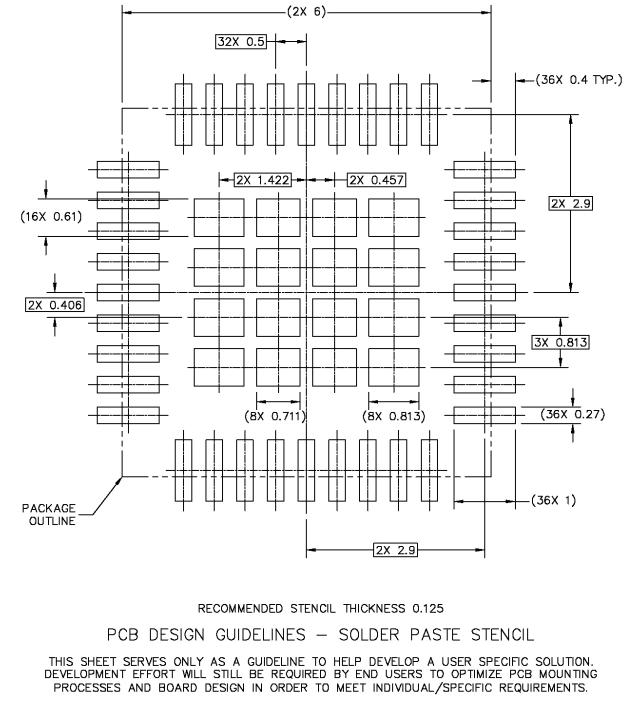

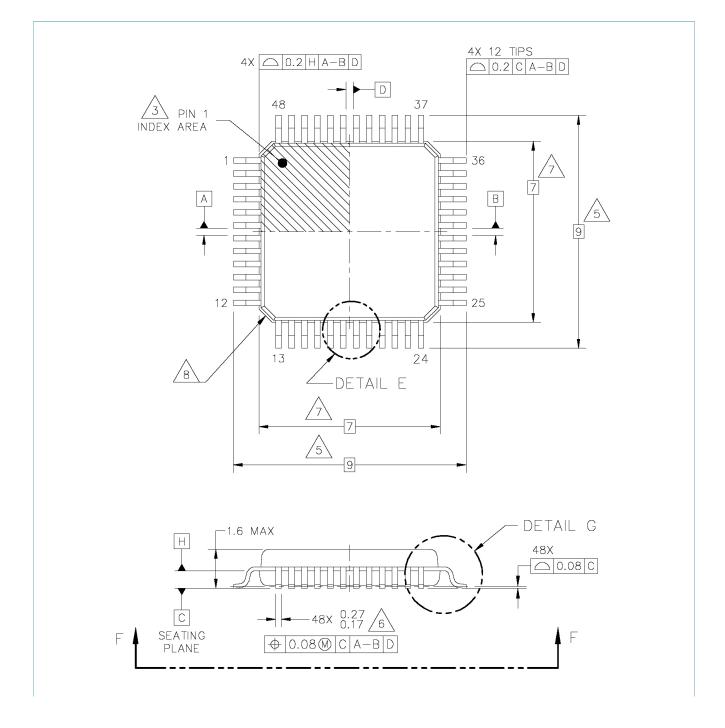

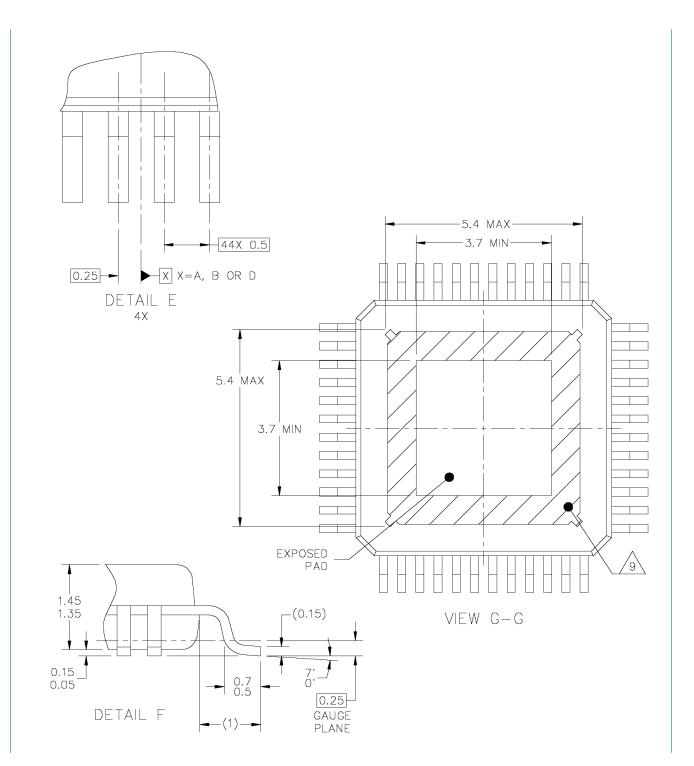

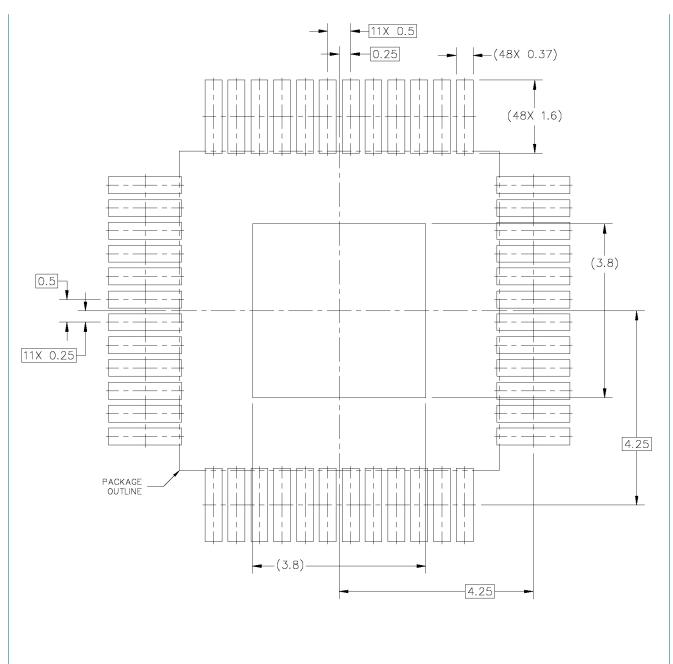

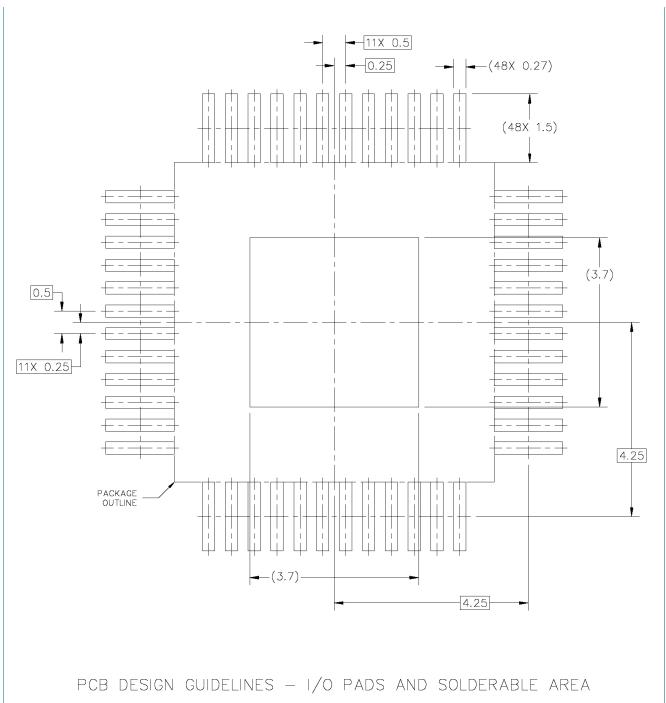

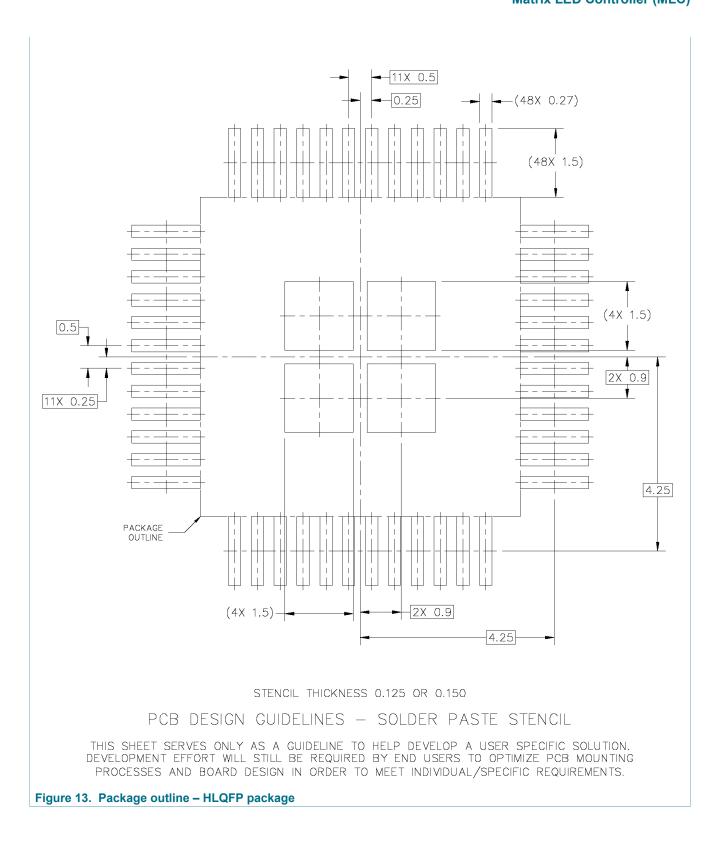

The MLC can be mounted close to the LEDs on an IMS PCB. Because the pinning has been optimized to avoid any crossing tracks, a single-layer PCB can be used. The ASL5xxxyHz family is available in automotive-qualified, thermally enhanced, 36-pin HVQFN and 48-pin HLQFP packages.

The device is designed to meet the stringent requirements of automotive applications, being fully AEC Q100 grade 1 and AEC Q006 qualified. It operates over the -40 °C to +125 °C ambient temperature range.

The Matrix LED Controller (MLC) also offers the possibility to be driven in direct PWM mode. In this mode, the microcontroller needs to update the PWM value in every channel with a certain cycle, determined by the system specifications. These part numbers, ASL5115yHz and ASL5108yHz, also offer 12-bit resolution to ensure a smooth dimming performance to avoid glitches in the output light.

The MLC family also offers two different maximum currents per switch. Part numbers ASL5008yHz and ASL5108yHz offer a maximum current per switch of 0.8 A. Part numbers ASL5015yHz and ASL5115yHz offer a maximum current per switch of 1.5 A.

All part numbers are pin-to-pin compatible, which offers a completely scalable and flexible system solution that can be adapted to any system requirements.

## 2 Features

- Automotive grade product that is AEC-Q100 grade 1 and AEC-Q006 qualified

- Operating ambient temperature range of -40 °C to +125 °C

- Maximum junction temperature of 175 °C

- Operating input voltage 5 V ± 0.5 V. Vcc pin.

- Able to drive up to 12 LEDs / segments, with a string voltage range up to 57 V

- Able to drive multiple LEDs per switch (MTP configurable)

- 12 channels, arranged in 4 configurable blocks of 3 switches per block

- Each block of three can fully float up to 60 V with respect to ground and can be paralleled with any other block

- Each switch can control up to 1.5 A LED current in the ASL5x15yHz family and up to 0.8 A in the ASL5x08yHz family

- + 100 m $\Omega$  (Rdson) switches for 1.5 A part numbers and 200 m $\Omega$  for 0.8 A part numbers

- · PWM dimming with 12-bit resolution and built-in phase shifting for minimum losses

- Internal PWM duty cycle generator with incremental calculation for glitch-free operation in the ASL50xxyHz family—Smart

- On-chip storage of preprogrammed PWM curves to reduce data traffic in ASL50xxyHz family—Smart

- LED brightness variation correction functionality

- On-chip 200 MHz oscillator, avoiding need for external quartz

- · CAN-based serial interface with optional external CAN physical layer

- Broadcast messages to reduce system latency and bus load

- Low Electromagnetic Emission (EME) and high Electromagnetic Immunity (EMI)

- Individual LED open and LED short-fault monitoring, with bypass feature on open condition

- NTC input with 6-bit resolution for LED temperature monitoring; directly connected to MLC

- Identification resistor input

- MLC can be used in a configuration of up to 32 ICs in a single CAN network

- Small package outline, leadless HVQFN package with improved Automated Optical Inspection (AOI) capability and leaded HLQFP package

- Low operational current consumption

- Sleep and wake-up modes available

- Standby current consumption < 1.35 mA

- Input under voltage protection

- 9-bit resolution IC junction temperature feedback via CAN interface

- Internally programmed Limp Home Mode (LHM) in case of communication failure

- Built-in charge pump failure operation mode (CPFSO)

## 3 Applications

- Automotive lighting

- Matrix/pixel high beam (ADB / Glare-Free High Beam GFHB)

- Matrix/pixel low beam (ADB)

- Dynamic turning indicator

- Welcoming scenarios

- Dynamic rear lights

ASL5xxxyHz Matrix LED Controller (MLC)

- Dynamic cornering lights

## 4 Orderable parts

| Type number | Package |                                                                             |           |  |  |  |  |  |

|-------------|---------|-----------------------------------------------------------------------------|-----------|--|--|--|--|--|

|             | Name    | Description                                                                 |           |  |  |  |  |  |

| ASL5015SHN  | HVQFN36 | Smart internal PWM generator with prestored curves (Smart – 1.5 A) – CAN    | SOT1092-4 |  |  |  |  |  |

| ASL5115SHN  | HVQFN36 | Direct PWM data for every channel (Direct – 1.5 A) – CAN                    | SOT1092-4 |  |  |  |  |  |

| ASL5008SHN  | HVQFN36 | Smart internal PWM generator with prestored curves (Smart – 0.8 A) – CAN    | SOT1092-4 |  |  |  |  |  |

| ASL5108SHN  | HVQFN36 | Direct PWM data for every channel (Direct – 0.8 A) – CAN                    | SOT1092-4 |  |  |  |  |  |

| ASL5015FHN  | HVQFN36 | Smart internal PWM generator with prestored curves (Smart – 1.5 A) – CAN-FD | SOT1092-4 |  |  |  |  |  |

| ASL5115FHN  | HVQFN36 | Direct PWM data for every channel (Direct – 1.5 A) – CAN-FD                 | SOT1092-4 |  |  |  |  |  |

| ASL5008FHN  | HVQFN36 | Smart internal PWM generator with prestored curves (Smart – 0.8 A) – CAN-FD | SOT1092-4 |  |  |  |  |  |

| ASL5108FHN  | HVQFN36 | Direct PWM data for every channel (Direct – 0.8 A) – CAN-FD                 | SOT1092-4 |  |  |  |  |  |

| ASL5015SHV  | HLQFP48 | Smart internal PWM generator with prestored curves (Smart – 1.5 A) – CAN    | SOT1571-1 |  |  |  |  |  |

| ASL5115SHV  | HLQFP48 | Direct PWM data for every channel (Direct – 1.5 A) – CAN                    | SOT1571-1 |  |  |  |  |  |

| ASL5008SHV  | HLQFP48 | Smart internal PWM generator with prestored curves (Smart – 0.8 A) – CAN    | SOT1571-1 |  |  |  |  |  |

| ASL5108SHV  | HLQFP48 | Direct PWM data for every channel (Direct – 0.8 A) – CAN                    | SOT1571-1 |  |  |  |  |  |

| ASL5015FHV  | HLQFP48 | Smart internal PWM generator with prestored curves (Smart – 1.5 A) – CAN-FD | SOT1571-1 |  |  |  |  |  |

| ASL5115FHV  | HLQFP48 | Direct PWM data for every channel (Direct – 1.5 A) – CAN-FD                 | SOT1571-1 |  |  |  |  |  |

| ASL5008FHV  | HLQFP48 | Smart internal PWM generator with prestored curves (Smart – 0.8 A) – CAN-FD | SOT1571-1 |  |  |  |  |  |

| ASL5108FHV  | HLQFP48 | Direct PWM data for every channel (Direct – 0.8 A) – CAN-FD                 | SOT1571-1 |  |  |  |  |  |

ASL5xxxyHz Matrix LED Controller (MLC)

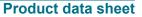

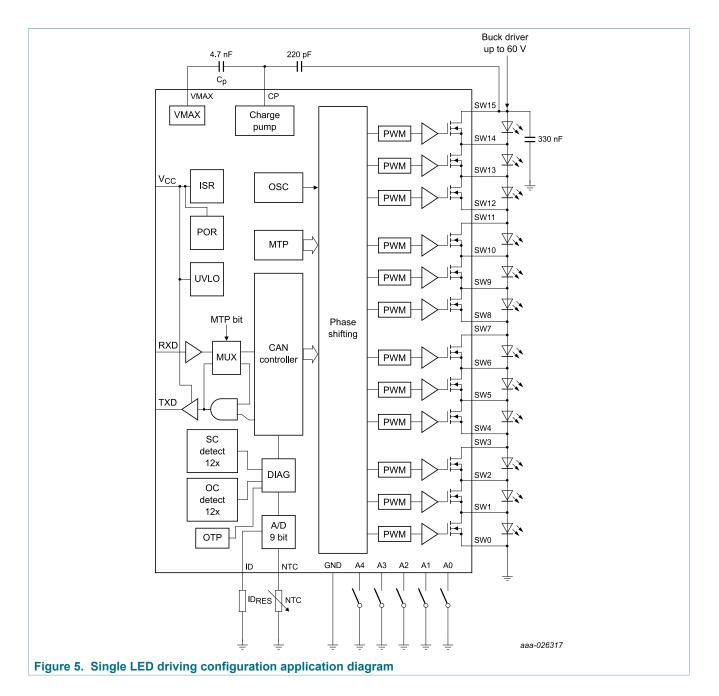

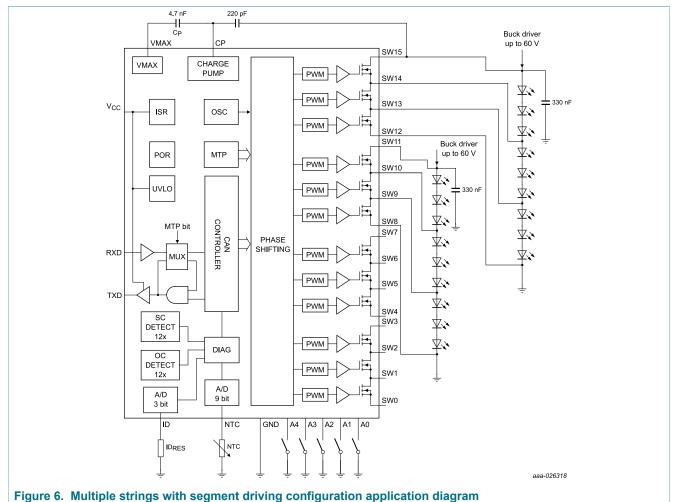

## 5 Application diagram

ASL5xxxyHz Matrix LED Controller (MLC)

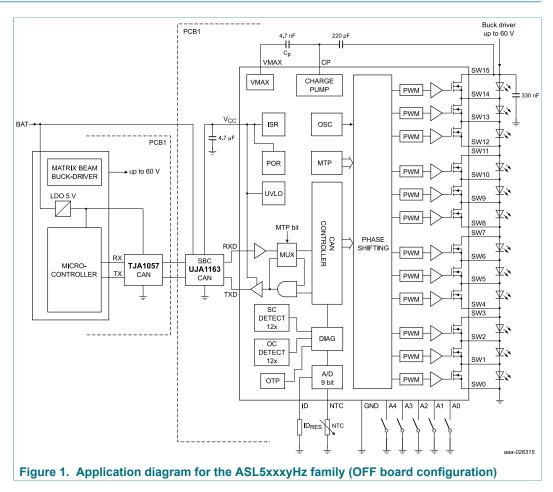

## 6 Block diagram

ASL5xxxyHz Product data sheet

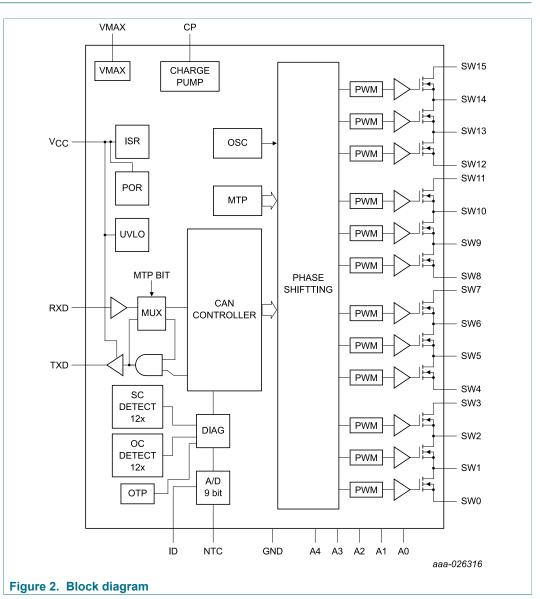

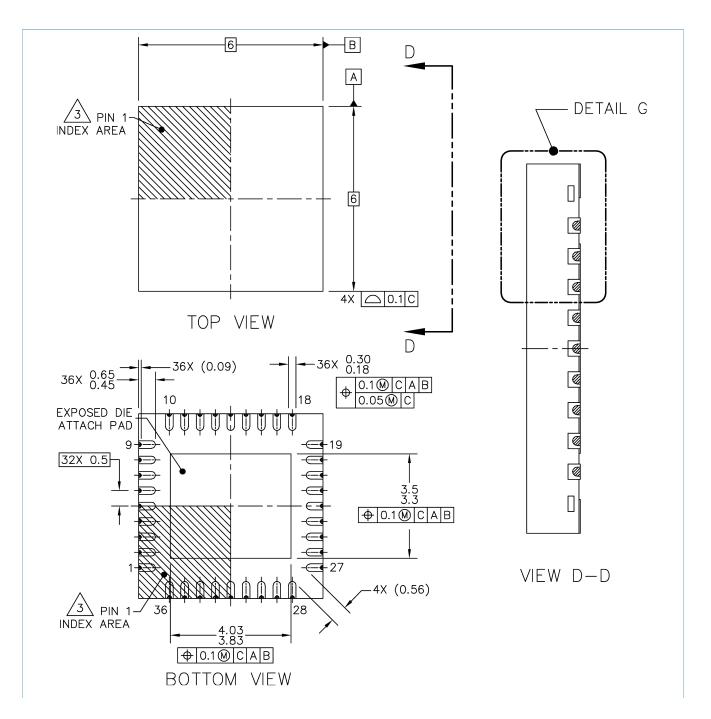

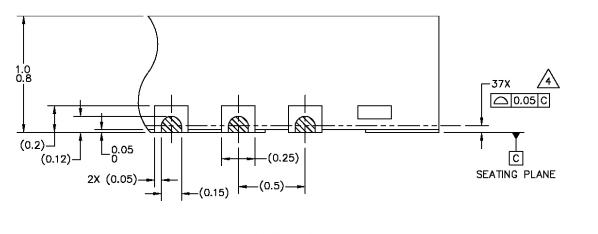

## 7 Pinning information

## 7.1 Pinning – HVQFN36 package

## 7.2 Pin description – HVQFN36 package

| Symbol          | Pin | Description                                    |

|-----------------|-----|------------------------------------------------|

| GND             | 1   | Ground                                         |

| TXD             | 2   | Bus data OUT                                   |

| RXD             | 3   | Bus data IN                                    |

| V <sub>CC</sub> | 4   | External supply (5 V)                          |

| RXD             | 5   | Bus data IN (Internally connected with pin 3)  |

| TXD             | 6   | Bus data OUT (Internally connected with pin 2) |

| NC              | 7   | Not connected                                  |

| VMAX            | 8   | Voltage reference for the charge pump          |

| СР              | 9   | External charge pump input                     |

| SW15            | 10  | Drain of switch 12                             |

| SW14            | 11  | Source of switch 12 and drain of switch 11     |

| SW13            | 12  | Source of switch 11 and drain of switch 10     |

| SW12            | 13  | Source of switch 10                            |

| NC              | 14  | Not Connected                                  |

| SW11            | 15  | Drain of switch 9                              |

| SW10            | 16  | Source of switch 9 and drain of switch 8       |

| SW9             | 17  | Source of switch 8 and drain of switch 7       |

| SW8             | 18  | Source of switch 7                             |

#### Table 2. Pin description

ASL5xxxyHz Product data sheet All information provided in this document is subject to legal disclaimers. Rev. 2.1 — 5 February 2019 © NXP B.V. 2019. All rights reserved.

ASL5xxxyHz

Matrix LED Controller (MLC)

| Symbol               | Pin | Description                                        |

|----------------------|-----|----------------------------------------------------|

| A0                   | 19  | Address bit 0                                      |

| A1                   | 20  | Address bit 1                                      |

| A2                   | 21  | Address bit 2                                      |

| A3                   | 22  | Address bit 3                                      |

| A4                   | 23  | Address bit 4                                      |

| ID                   | 24  | Connection for the identification resistor         |

| GND                  | 25  | Ground                                             |

| NTC                  | 26  | Connection to the NTC                              |

| Internally connected | 27  | ICP (Internally Connected Pin) – Connect to ground |

| SW7                  | 28  | Drain of switch 6                                  |

| SW6                  | 29  | Source of switch 6 and drain of switch 5           |

| SW5                  | 30  | Source of switch 5 and drain of switch 4           |

| SW4                  | 31  | Source of switch 4                                 |

| NC                   | 32  | Not Connected                                      |

| SW3                  | 33  | Drain of switch 3                                  |

| SW2                  | 34  | Source of switch 3 and drain of switch 2           |

| SW1                  | 35  | Source of switch 2 and drain of switch 1           |

| SW0                  | 36  | Source of switch 1                                 |

| EXP                  | 37  | Exposed pad – Connect it to ground                 |

NC pins are inserted between two blocks of switches to prevent high voltages between two adjacent pins. An NC pin is also inserted between VMAX and TXD pins. NC pins must float.

The exposed center pad of the package is internally connected to ground. For enhanced thermal and electrical performance, it is highly recommended to connect the exposed center pad the the board's ground.

Both RXD pins and both TXD pins are internally connected to facilitate single-layer PCB layout without jumpers.

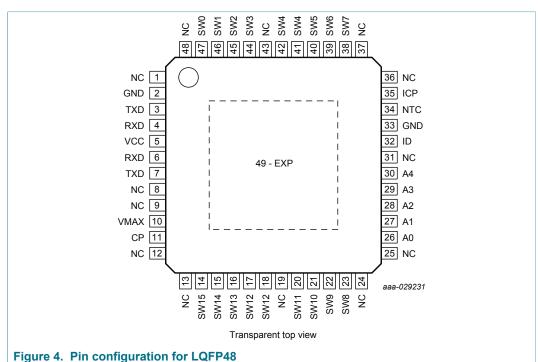

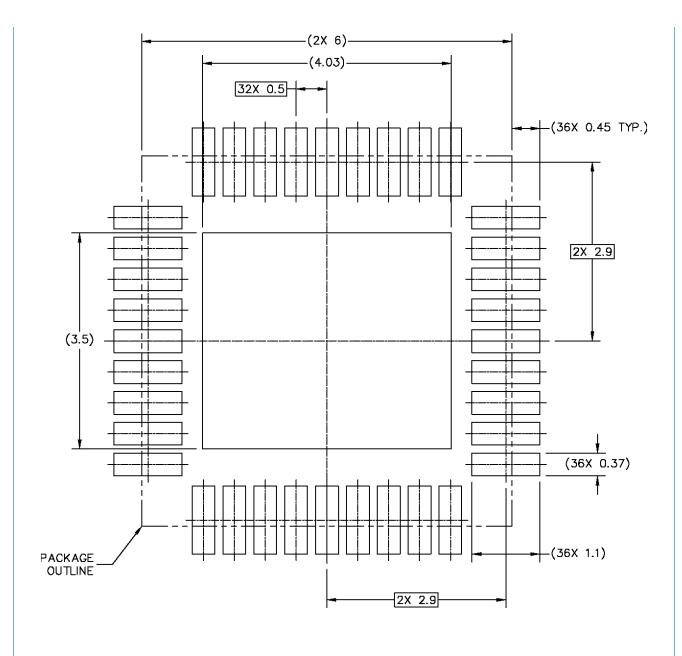

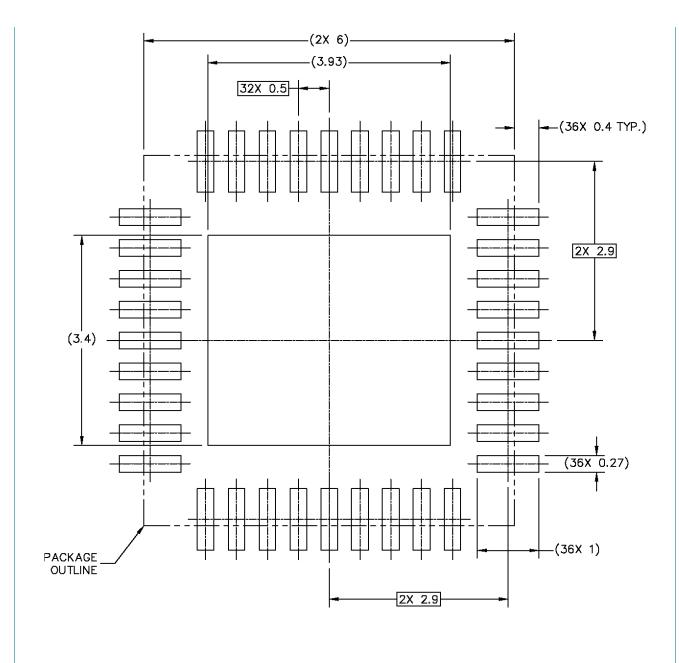

## 7.3 Pinning – HLQFP48 package

### 7.4 Pin description – HLQFP48 package

| Table 3. Pin descrip | Pin | Description                                    |

|----------------------|-----|------------------------------------------------|

| NC                   | 1   | Not connected                                  |

| GND                  | 2   | Ground                                         |

| TXD                  | 3   | Bus data OUT                                   |

| RXD                  | 4   | Bus data IN                                    |

| VCC                  | 5   | External supply ±10 % (5 V)                    |

| RXD                  | 6   | Bus data IN                                    |

| TXD                  | 7   | Bus data OUT                                   |

| NC                   | 8   | Not connected (can be used for ground routing) |

| NC                   | 9   | Not connected                                  |

| VMAX                 | 10  | Max. voltage reference for the charge pump     |

| СР                   | 11  | External charge pump input                     |

| NC                   | 12  | Not connected                                  |

| NC                   | 13  | Not connected                                  |

| SW15                 | 14  | Drain of switch 12                             |

| SW14                 | 15  | Source of switch 12 and drain of switch 11     |

| SW13                 | 16  | Source of switch 11 and drain of switch 10     |

| SW12                 | 17  | Source of switch 10                            |

## Table 3. Pin description

## ASL5xxxyHz

Matrix LED Controller (MLC)

| SW1218Source of switch 10NC19Not connectedSW1120Drain of switch 9SW1021Source of switch 9 and drain of switch 8SW922Source of switch 8 and drain of switch 7SW823Source of switch 7NC24Not connectedNC25Not connectedA026Address bit 0A127Address bit 2A329Address bit 3A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC37Not connectedNTC38Drain of switch 6SW738Drain of switch 6SW639Source of switch 6 and Drain of switch 1SW644Source of switch 3 and Drain of switch 4SW441Source of switch 4SW444Drain of switch 3SW444Drain of switch 3SW444Source of switch 3 and Drain of switch 1SW444Source of switch 1 and Drain of switch 1 <th>Symbol</th> <th>Pin</th> <th>Description</th> | Symbol | Pin | Description                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------------------------------------------------|

| SW1120Drain of switch 9SW1021Source of switch 9 and drain of switch 8SW922Source of switch 8 and drain of switch 7SW823Source of switch 7NC24Not connectedNC25Not connectedA026Address bit 0A127Address bit 1A228Address bit 2A329Address bit 3A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedSW639Source of switch 6 and Drain of switch 5SW5400Source of switch 6 and Drain of switch 4SW441Source of switch 4SW442Source of switch 4SW443Not connectedSW444Source of switch 4SW441Source of switch 4SW442Source of switch 4SW444Drain of switch 3SW245Source of switch 3 and Drain of switch 1SW047Source of switch 1SW048Not connected                                                                                                                                                                                                                       | SW12   | 18  | Source of switch 10                                   |

| SW1021Source of switch 9 and drain of switch 8SW922Source of switch 7 and drain of switch 7SW823Source of switch 7NC24Not connectedNC25Not connectedA026Address bit 0A127Address bit 1A228Address bit 2A329Address bit 3A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedSW738Drain of switch 6SW639Source of switch 6 and Drain of switch 4SW641Source of switch 5 and Drain of switch 4SW442Source of switch 3 and Drain of switch 4SW443Not connectedSW344Drain of switch 3SW442Source of switch 4SW443Not connectedSW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 3 and Drain of switch 1SW044Source of switch 3 and Drain of switch 1SW146Source of switch 3 and Drain of switch 1SW245Source of switch 3 and Drain of switch 1SW048Not connected <td>NC</td> <td>19</td> <td>Not connected</td>                    | NC     | 19  | Not connected                                         |

| SW922Source of switch 8 and drain of switch 7SW823Source of switch 7NC24Not connectedNC25Not connectedA026Address bit 0A127Address bit 1A228Address bit 2A329Address bit 3A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedSW738Drain of switch 6SW639Source of switch 6 and Drain of switch 4SW441Source of switch 7SW442Source of switch 5 and Drain of switch 4SW444Drain of switch 3SW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 3 and Drain of switch 1SW047Source of switch 3 and Drain of switch 1SW048Not connected                                                                                                                                                                                                                                                                                            | SW11   | 20  | Drain of switch 9                                     |

| SW823Source of switch 7NC24Not connectedNC25Not connectedA026Address bit 0A127Address bit 1A228Address bit 2A329Address bit 3A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC38Drain of switch 6SW738Drain of switch 6SW639Source of switch 5 and Drain of switch 1SW444Source of switch 3 and Drain of switch 4SW444Source of switch 3 and Drain of switch 2SW344Drain of switch 3 and Drain of switch 2SW344Source of switch 3 and Drain of switch 1SW245Source of switch 3 and Drain of switch 2SW146Source of switch 3 and Drain of switch 1SW047Source of switch 2 and Drain of switch 1SW044Source of switch 3 and Drain of switch 1SW044Source of switch 2 and Drain of switch 1SW044Source of switch 2 and Drain of switch 1SW044Source of switch 1SW044Source of switch 1SW044Source of switch 1SW044Source of switch 1SW044<                                           | SW10   | 21  | Source of switch 9 and drain of switch 8              |

| NC24Not connectedNC25Not connectedA026Address bit 0A127Address bit 1A228Address bit 2A329Address bit 3A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC37Not connectedSW738Drain of switch 6SW639Source of switch 5 and Drain of switch 5SW441Source of switch 3SW442Source of switch 3SW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW344Source of switch 3 and Drain of switch 2SW446Source of switch 3 and Drain of switch 1SW245Source of switch 3 and Drain of switch 1SW446Source of switch 2 and Drain of switch 1SW446Source of switch 2 and Drain of switch 1SW446Source of switch 2 and Drain of switch 1SW446Source of switch 1SW446Source of switch 1SW446S                                               | SW9    | 22  | Source of switch 8 and drain of switch 7              |

| NC25Not connectedA026Address bit 0A127Address bit 1A228Address bit 2A329Address bit 3A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedSW738Drain of switch 6SW639Source of switch 6 and Drain of switch 5SW540Source of switch 4SW441Source of switch 4SW442Source of switch 3SW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW344Source of switch 3 and Drain of switch 1SW245Source of switch 3 and Drain of switch 1SW245Source of switch 2 and Drain of switch 1SW047Source of switch 2 and Drain of switch 1SW048Not connected                                                                                                                                                                                                                                                                                                            | SW8    | 23  | Source of switch 7                                    |

| A026Address bit 0A127Address bit 1A228Address bit 2A329Address bit 3A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedSW738Drain of switch 6SW639Source of switch 5 and Drain of switch 4SW441Source of switch 4SW443Not connectedSW3444Drain of switch 3SW4435Source of switch 4SW2445Source of switch 3 and Drain of switch 2SW1466Source of switch 3 and Drain of switch 1SW047Source of switch 2 and Drain of switch 1SW048Not connected                                                                                                                                                                                                                                                                                                                                                                                                                        | NC     | 24  | Not connected                                         |

| A127Address bit 1A228Address bit 2A329Address bit 3A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedSW738Drain of switch 6SW639Source of switch 6 and Drain of switch 5SW441Source of switch 4SW442Source of switch 4SW3444Drain of switch 3SW2455Source of switch 3 and Drain of switch 2SW3446Source of switch 3 and Drain of switch 2SW3446Source of switch 3SW2455Source of switch 3 and Drain of switch 2SW1468Source of switch 1SW047Source of switch 1NC488Not connected                                                                                                                                                                                                                                                                                                                                                                                    | NC     | 25  | Not connected                                         |

| A228Address bit 2A329Address bit 3A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedNC37Not connectedSW738Drain of switch 6SW639Source of switch 5 and Drain of switch 5SW441Source of switch 4SW442Source of switch 4SW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW344Source of switch 3 and Drain of switch 2SW445Source of switch 3 and Drain of switch 2SW3446Source of switch 3 and Drain of switch 1SW245Source of switch 2 and Drain of switch 1SW047Source of switch 2 and Drain of switch 1SW048Not connected                                                                                                                                                                                                                                                                                                                       | A0     | 26  | Address bit 0                                         |

| A329Address bit 3A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedNC37Not connectedSW738Drain of switch 6SW639Source of switch 5 and Drain of switch 5SW540Source of switch 4SW441Source of switch 4SW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 2 and Drain of switch 1SW048Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A1     | 27  | Address bit 1                                         |

| A430Address bit 4NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedNC37Not connectedSW738Drain of switch 6SW639Source of switch 6 and Drain of switch 5SW441Source of switch 4SW442Source of switch 4SW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 3 and Drain of switch 1SW047Source of switch 3 and Drain of switch 1SW244Drain of switch 3SW245Source of switch 3 and Drain of switch 1SW047Source of switch 1SW048Not connected                                                                                                                                                                                                                                                                                                                                                                                                       | A2     | 28  | Address bit 2                                         |

| NC31Not connectedBIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedNC37Not connectedSW738Drain of switch 6SW639Source of switch 5 and Drain of switch 4SW441Source of switch 4SW442Source of switch 4SW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 3 and Drain of switch 1SW047Source of switch 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A3     | 29  | Address bit 3                                         |

| BIN32Connection for the identification resistorGND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedNC37Not connectedSW738Drain of switch 6SW639Source of switch 6 and Drain of switch 5SW540Source of switch 5 and Drain of switch 4SW441Source of switch 4SW442Source of switch 4SW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW044Not connectedSW146Source of switch 3 and Drain of switch 2SW146Source of switch 3 and Drain of switch 1SW047Source of switch 1SW048Not connected                                                                                                                                                                                                                                                                                                                                                                                                | A4     | 30  | Address bit 4                                         |

| GND33GroundNTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedNC37Not connectedSW738Drain of switch 6SW639Source of switch 6 and Drain of switch 5SW5400Source of switch 5 and Drain of switch 4SW441Source of switch 4SW442Source of switch 4SW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW048Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NC     | 31  | Not connected                                         |

| NTC34Connection to the NTCICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedNC37Not connectedSW738Drain of switch 6SW639Source of switch 6 and Drain of switch 5SW540Source of switch 5 and Drain of switch 4SW441Source of switch 4SW442Source of switch 4NC43Not connectedSW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BIN    | 32  | Connection for the identification resistor            |

| ICP35ICP (Internally Connected Pin) – Connect it to groundNC36Not connectedNC37Not connectedSW738Drain of switch 6SW639Source of switch 6 and Drain of switch 5SW540Source of switch 5 and Drain of switch 4SW441Source of switch 4SW442Source of switch 4NC43Not connectedSW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GND    | 33  | Ground                                                |

| NC36Not connectedNC37Not connectedSW738Drain of switch 6SW639Source of switch 6 and Drain of switch 5SW540Source of switch 5 and Drain of switch 4SW441Source of switch 4SW442Source of switch 4NC43Not connectedSW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NTC    | 34  | Connection to the NTC                                 |

| NC37Not connectedSW738Drain of switch 6SW639Source of switch 6 and Drain of switch 5SW540Source of switch 5 and Drain of switch 4SW441Source of switch 4SW442Source of switch 4NC43Not connectedSW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ICP    | 35  | ICP (Internally Connected Pin) – Connect it to ground |

| SW738Drain of switch 6SW639Source of switch 6 and Drain of switch 5SW540Source of switch 5 and Drain of switch 4SW441Source of switch 4SW442Source of switch 4NC43Not connectedSW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NC     | 36  | Not connected                                         |

| SW639Source of switch 6 and Drain of switch 5SW540Source of switch 5 and Drain of switch 4SW441Source of switch 4SW442Source of switch 4NC43Not connectedSW344Drain of switch 3SW245Source of switch 2 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NC     | 37  | Not connected                                         |

| SW540Source of switch 5 and Drain of switch 4SW441Source of switch 4SW442Source of switch 4NC43Not connectedSW344Drain of switch 3SW245Source of switch 2 and Drain of switch 2SW146Source of switch 1SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SW7    | 38  | Drain of switch 6                                     |

| SW441Source of switch 4SW442Source of switch 4SW442Source of switch 4NC43Not connectedSW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SW6    | 39  | Source of switch 6 and Drain of switch 5              |

| SW442Source of switch 4NC43Not connectedSW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SW5    | 40  | Source of switch 5 and Drain of switch 4              |

| NC43Not connectedSW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SW4    | 41  | Source of switch 4                                    |

| SW344Drain of switch 3SW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SW4    | 42  | Source of switch 4                                    |

| SW245Source of switch 3 and Drain of switch 2SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NC     | 43  | Not connected                                         |

| SW146Source of switch 2 and Drain of switch 1SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SW3    | 44  | Drain of switch 3                                     |

| SW047Source of switch 1NC48Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SW2    | 45  | Source of switch 3 and Drain of switch 2              |

| NC 48 Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SW1    | 46  | Source of switch 2 and Drain of switch 1              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SW0    | 47  | Source of switch 1                                    |

| EXP 49 Exposed pad - Connect it to ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NC     | 48  | Not connected                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EXP    | 49  | Exposed pad - Connect it to ground                    |

NC pins are inserted between two blocks of switches to prevent high voltages between two adjacent pins. Two NC pins are also inserted between VMAX and TXD pins. The NC pins must float, only pin 8 can be used for ground routing, since pin 9 (NC) still keep the isolation between ground and high voltage.

#### The exposed center pad must be connected to ground during layout routing.

Both RXD pins and both TXD pins are internally connected to facilitate single-layer PCB layout without jumpers.

## 8 Functional description

### 8.1 Integrated switches for single or multiple LEDs dimming

The floating blocks make it possible for the ASL5xxxyHz family (Matrix LED Controller, MLC) to drive 12 single LEDs or multiple LEDs per switch and multiple strings with different currents and string voltages. The 12 independent switches are separated in 4 floating blocks of 3 switches each. Every block can float at 60 V with respect to ground and can be driven separately or as a unique system.

Figure 5 and Figure 6 show possible configurations.

## **NXP Semiconductors**

# ASL5xxxyHz

## Matrix LED Controller (MLC)

## **NXP Semiconductors**

Matrix LED Controller (MLC)

Polarity must be respected in the internal MOSFET.

## 8.2 LED current capability and power dissipation

The LED string current is provided by a separate buck or boost converter. The specifications of the matrix controller are matched to the multichannel buck converter ASLx41xSHN. The MLC can also be driven by other buck driver or constant current suppliers. One buck converter output supplies the current for one LED string. For the MLC, the maximum LED string voltage is 57 V, maximum LED string current is 1.5 A in serial configuration, and up to 6 A in parallel configuration for ASL5x15yHzpart numbers. For part numbers ASL5x08yHz, the maximum LED string current is 0.8 A, in serial configuration, and up to 3.2 A when paralleling all switches' blocks.

The internal power dissipation depends on the number of LEDs that are bypassed. The maximum dissipation in the Matrix LED Controller occurs when all switches are closed with 1.5 A LED current through them, the dissipation is estimated to be 5 W at 120  $^{\circ}$ C junction temperature.

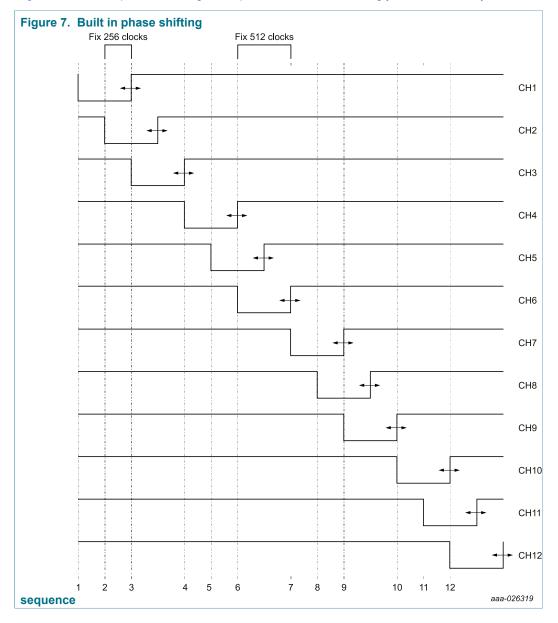

## 8.3 Internal PWM dimming generator and phase shifting

The ASL5015yHz and ASL5008yHz part numbers have an internal PWM generator module for each channel. The PWM has 12-bit resolution, which means a time accuracy

of 4.1 ms/4096 = 1  $\mu$ s , at 244 Hz or 0.5  $\mu$ s, at 488 Hz. The resolution in terms of PWM percentage is 0.024 %. This resolution ensures very smooth LED dimming to very low light levels.

When a PWM switch turns on, the forward voltage of the whole string decreases with the  $V_f$  of one LED. During the negative slope, there could be a high discharge current from the string capacitor that also flows through the entire LED string. If more than one LED is bypassed at the same time, then this injected current is higher when additional LEDs are bypassed. Therefore, it is desired to close only one switch at a time. For that reason, the MLC incorporates an internal phase-shifting module that ensures closing switches one at a time.

**Note:** Automated phase shifting feature is applicable to all Matrix LED controllers part numbers.

Figure 7 shows a phase-shifting example in an MLC IC, during just one PWM cycle.

© NXP B.V. 2019. All rights reserved.

Each block of switches can be assigned to a block of channels and phases; each block can be paralleled with any other block. For paralleling switches, it is necessary that they turn on at the same instant and use the same PWM information.

The shiting between two consecutive switches of the same block is 256 clocks. The shifting between two consecutive switches of different blocks is 512 clocks.

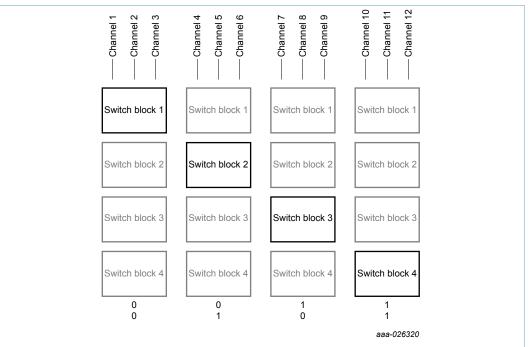

Two bits per block are required in the MTP to define which group of channels are assigned to a phase sequence. In Figure 8, there is an example of all blocks assigned to different phase shifting sequences.

#### Figure 8. Blocks of switches can be assigned to phase shifting sequences

The MTP configuration bits (2 bits) are showed in the bottom side of the blocks. Depending on the selected configuration, a different block may be highlighted in the graph. These two bits are used to select the phase shifting sequence of the associated channels/switches. When blocks are in series, the two bits should be different in each block. For parallel configuration, the blocks that work together should have the same phase shifting sequence (same 2 bits value).

This way of defining the PWM periods guarantees that two or more switches are never closed at the same moment, unless they are in parallel. It makes programming easier and reduces the voltage ripple on the LED string.

The sequence for each individual block can be programmed in the MTP. See <u>Section 14</u> <u>"Nonvolatile Multitime Programmable Memory (MTP)"</u>.

### 8.4 Programming and execution of PWM dimming – ASL50xxyHz

In order to reduce data traffic over the serial interface, a polynomial curve defines the PWM dimming profile. Coefficients for the PWM dimming polynomial curves can be stored in an internal nonvolatile MTP (Multiple Time Programmable) memory. This programming is done once at the end of the customer production line.

| ASLOXXXYIIZ |      |       |

|-------------|------|-------|

| Product     | data | sheet |

© NXP B.V. 2019. All rights reserved.

## ASL5xxxyHz Matrix LED Controller (MLC)

The equation to determine the curve is up to a third-grade polynomial:

$Ax^3 + Bx^2 + Cx + D$

The system makes an absolute calculation with the first x (step) value and then uses an incremental calculation to ensure no glitch between consecutive PWM Duty Cycle values, even when the shift value is changed to modify the curve speed. Absolute calculation is applied only when START command is used, for NOW or AUTO bits, the incremental calculation is used.

#### Note: A system emulation tool is available and can reproduce any possible scenario.

The implementation of a differential calculation ensures a glitch-free system. This method allows a very smooth LED dimming without any undesirable light glitch.

The information to be stored in the MTP are only the polynomial coefficient values A, B, C and D. Then, the system calculates the resulting PWM duty cycle on the fly with an internal PWM generator (in the Smart version, ASL50xxyHz).

Several curves can be sequenced in case of long fade-in or fade-out scenarios. This feature is only available in the Smart versions, ASL50xxyHz.

The ASL5015yHz and ASL5008yHz allow the storage of eight-polynomial curves. The curves can be followed in both directions, depending on whether the stop position is greater or lower than the start position; and the number of fade-in scenarios do not have to be the same as the fade-out ones.

It may be necessary to speed up or slow down a curve or interrupt a fade-in curve to set the PWM duty cycle to 100 % immediately, such as in the case of high-beam flashing. This adjustment is possible by changing the shift value.

The programmed coefficients in the internal MTP can also be negative, for that reason there are 13 bits reserved per coefficient. That gives the possibility to make smoother curves and shapes that are not possible with just positive coefficients. The available

simulation tool supports both signed coefficients and shows the system behavior in any possible condition.

### 8.4.1 Channel programming registers map

| ddress | Register  | D7 | D6                                   | D5 | D4     | D3                      | D2 | D1        | <b>D0</b> | Default |

|--------|-----------|----|--------------------------------------|----|--------|-------------------------|----|-----------|-----------|---------|

| 00h    | CURVID1   | S  | HIFT1[2:0]                           |    | AUTO1  | NOW1                    | CU | RVEID1[2  | 2:0]      | 0000000 |

| 01h    | STARTPOS1 |    |                                      |    | STARTP | OS1[7:0]                |    |           |           | 0000000 |

| 02h    | STOPPOS1  |    |                                      |    | STOPPO | OS1[7:0]                |    |           |           | 1111111 |

| 03h    | DELAY1    |    | DELAY1[7:0]                          |    |        |                         |    |           |           |         |

| 04h    | CURVID2   | S  | SHIFT2[2:0] AUTO2 NOW2 CURVEID2[2:0] |    |        |                         |    |           |           |         |

| 05h    | STARTPOS2 |    |                                      |    | STARTP | OS2[7:0]                |    |           |           | 0000000 |

| 06h    | STOPPOS2  |    |                                      |    | STOPPO | OS2[7:0]                |    |           |           | 1111111 |

| 07h    | DELAY2    |    |                                      |    | DELA   | Y2[7:0]                 |    |           |           | 0000000 |

| 08h    | CURVID3   | S  | HIFT3[2:0]                           |    | AUTO3  | NOW3                    | CU | IRVEID3[2 | 2:0]      | 0000000 |

| 09h    | STARTPOS3 |    |                                      |    | STARTP | OS3[7:0]                |    |           |           | 0000000 |

| 0Ah    | STOPPOS3  |    |                                      |    | STOPPO | DS3[7:0]                |    |           |           | 1111111 |

| 0Bh    | DELAY3    |    |                                      |    | DELA   | Y3[7:0]                 |    |           |           | 0000000 |

| 0Ch    | CURVID4   | S  | SHIFT4[2:0] AUTO4 NOW4 CURVEID4[2:0] |    |        |                         |    |           | 0000000   |         |

| 0Dh    | STARTPOS4 |    | STARTPOS4[7:0]                       |    |        |                         |    |           |           | 0000000 |

| 0Eh    | STOPPOS4  |    | STOPPOS4[7:0]                        |    |        |                         |    |           |           | 1111111 |

| 0Fh    | DELAY4    |    | DELAY4[7:0]                          |    |        |                         |    |           |           | 0000000 |

| 10h    | CURVID5   | S  | SHIFT5[2:0] AUTO5 NOW5 CURVEID5[2:0] |    |        |                         |    | 0000000   |           |         |

| 11h    | STARTPOS5 |    | STARTPOS5[7:0]                       |    |        |                         |    |           |           | 0000000 |

| 12h    | STOPPOS5  |    |                                      |    | STOPPO | DS5[7:0]                |    |           |           | 1111111 |

| 13h    | DELAY5    |    |                                      |    | DELA   | Y5[7:0]                 |    |           |           | 0000000 |

| 14h    | CURVID6   | S  | HIFT6[2:0]                           |    | AUTO6  | NOW6                    | CU | RVEID6[2  | 2:0]      | 0000000 |

| 15h    | STARTPOS6 |    |                                      |    | STARTP | OS6[7:0]                |    |           |           | 0000000 |

| 16h    | STOPPOS6  |    |                                      |    | STOPPO | DS6[7:0]                |    |           |           | 1111111 |

| 17h    | DELAY6    |    |                                      |    | DELA   | Y6[7:0]                 |    |           |           | 0000000 |

| 18h    | CURVID7   | S  | HIFT7[2:0]                           |    | AUTO7  | NOW7                    | CU | IRVEID7[2 | 2:0]      | 0000000 |

| 19h    | STARTPOS7 |    |                                      |    | STARTP | OS7[7:0]                |    |           |           | 0000000 |

| 1Ah    | STOPPOS7  |    |                                      |    | STOPPO | OS7[7:0]                |    |           |           | 1111111 |

| 1Bh    | DELAY7    |    |                                      |    | DELA   | Y7[7:0]                 |    |           |           | 0000000 |

| 1Ch    | CURVID8   | S  | HIFT8[2:0]                           |    | AUTO8  | JTO8 NOW8 CURVEID8[2:0] |    |           | 2:0]      | 0000000 |

| 1Dh    | STARTPOS8 |    |                                      |    | STARTP | OS8[7:0]                |    |           |           | 0000000 |

| 1Eh    | STOPPOS8  |    |                                      |    | STOPPO | DS8[7:0]                |    |           |           | 1111111 |

| 1Fh    | DELAY8    |    |                                      |    | DELA   | Y8[7:0]                 |    |           |           | 0000000 |

| 20h    | CURVID9   | S  | HIFT9[2:0]                           |    | AUTO9  | NOW9                    | CU | RVEID9[2  | 2:01      | 0000000 |

## ASL5xxxyHz

#### Matrix LED Controller (MLC)

| Address | Register   | D7 | <b>D6</b>       | D5  | D4      | D3        | D2 | D1      | D0    | Default  |  |  |

|---------|------------|----|-----------------|-----|---------|-----------|----|---------|-------|----------|--|--|

| 21h     | STARTPOS9  |    | STARTPOS9[7:0]  |     |         |           |    |         |       |          |  |  |

| 22h     | STOPPOS9   |    | STOPPOS9[7:0]   |     |         |           |    |         |       |          |  |  |

| 23h     | DELAY9     |    | DELAY9[7:0]     |     |         |           |    |         |       |          |  |  |

| 24h     | CURVID10   | Sł | HIFT10[2        | :0] | AUTO10  | NOW10     | CU | RVEID10 | [2:0] | 00000000 |  |  |

| 25h     | STARTPOS10 |    |                 |     | STARTPO | OS10[7:0] |    |         |       | 00000000 |  |  |

| 26h     | STOPPOS10  |    | STOPPOS10[7:0]  |     |         |           |    |         |       |          |  |  |

| 27h     | DELAY10    |    | DELAY10[7:0]    |     |         |           |    |         |       |          |  |  |

| 28h     | CURVID11   | Sł | HIFT11[2        | :0] | AUTO11  | NOW11     | CU | RVEID11 | [2:0] | 00000000 |  |  |

| 29h     | STARTPOS11 |    |                 |     | STARTPO | OS11[7:0] |    |         |       | 00000000 |  |  |

| 2Ah     | STOPPOS11  |    |                 |     | STOPPC  | )S11[7:0] |    |         |       | 11111111 |  |  |

| 2Bh     | DELAY11    |    |                 |     | DELAY   | ′11[7:0]  |    |         |       | 00000000 |  |  |

| 2Ch     | CURVID12   | Sł | HIFT12[2        | :0] | AUTO12  | NOW12     | CU | RVEID12 | [2:0] | 00000000 |  |  |

| 2Dh     | STARTPOS12 |    | STARTPOS12[7:0] |     |         |           |    |         |       |          |  |  |

| 2Eh     | STOPPOS12  |    | STOPPOS12[7:0]  |     |         |           |    |         |       | 11111111 |  |  |

| 2Fh     | DELAY12    |    | DELAY12[7:0]    |     |         |           |    |         |       |          |  |  |

**SHIFTx:** These three bits determine the shift value used in the internal PWM generator. The speed of the curve depends on the shift value. When the lowest shift value is selected (2), the fastest curve is performed. <u>Table 5</u> shows the different possible values.

#### Table 5. SHIFT values

| SHIFT[2:0] | 111 | 110 | 101 | 100 | 011 | 010 | 001 | 000 |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Value      | 2   | 4   | 8   | 16  | 32  | 64  | 128 | 256 |

**AUTOx:** Set this bit to 1 when the channel is already following another curve, so that this new configuration can be followed at the end of the current sequence.

**NOWx:** To implement changes immediately, set this bit to 1. The system will implement the new SHIFT, AUTO and CURVEID to the specific channel/switch immediately and automatically proceed with the PWM calculation. If this bit is set to 0, then all the other values (SHIFT, AUTO and CURVEID) are stored in the shadow register until the current sequence is done and another trigger is set (START command or AUTO bit).

**CURVEIDx:** These three bits are used to identify the curve the channel follows during the fade sequence. With three bits, eight curves can be selected.

**STARTPOSx:** In this register, the start position must be set. The value is referred to as a step from 0 to 255 (8 bits resolution).

**STOPPOSx:** In this register, the stop position must be set. The value is referred to as a step from 0 to 255 (8 bits resolution).

**Note:** Because any curve can be followed in both directions, a fade-in sequence occurs when the start value is smaller than the stop value. As soon as the start value is greater than the stop value, then the sequence is a fade-out one. When using negative coefficients, the curve behavior could change depending on the coefficient values.

**DELAYx:** This 8-bit register is used to add a delay to the sequence start. Because it is an 8-bit register and this delay is related to steps, the delay value is from 0 to 255. The delay

time depends on the PWM frequency. For example, if the PWM frequency is 244 Hz, then the delay value has a resolution of 4 ms. If the PWM frequency is 488 Hz, then the delay time resolution is 2 ms. This factor is a great help in simplifying dynamic turning-indicator sequences.

The microcontroller has the possibility of reading back the current PWM values in every cycle. These values are accessible from the register 42h to 59h, as shown in <u>Table 6</u>. This accessibility ensures maximum control of the system and LED board feedback.

| Address | Register    | D7        | <b>D6</b>         | D5  | D4       | D3         | D2     | D1   | D0 |  |  |

|---------|-------------|-----------|-------------------|-----|----------|------------|--------|------|----|--|--|

| 42h     | ReadCH1-LB  |           | PWM [7:0]         |     |          |            |        |      |    |  |  |

| 43h     | ReadCH1-MB  |           | unused PWM [11:8] |     |          |            |        |      |    |  |  |

| 44h     | ReadCH2-LB  |           | PWM [7:0]         |     |          |            |        |      |    |  |  |

| 45h     | ReadCH2-MB  |           | unu               | sed |          |            | PWM [1 | 1:8] |    |  |  |

| 46h     | ReadCH3-LB  |           |                   |     | PV       | /M [7:0]   |        |      |    |  |  |

| 47h     | ReadCH3-MB  |           | unu               | sed |          |            | PWM [1 | 1:8] |    |  |  |

| 48h     | ReadCH4-LB  |           |                   |     | PV       | /M [7:0]   |        |      |    |  |  |

| 49h     | ReadCH4-MB  |           | unu               | sed |          |            | PWM [1 | 1:8] | -  |  |  |

| 4Ah     | ReadCH5-LB  |           |                   |     | /M [7:0] |            |        | -    |    |  |  |

| 4Bh     | ReadCH5-MB  |           | unu               | sed |          |            | PWM [1 | 1:8] |    |  |  |

| 4Ch     | ReadCH6-LB  | PWM [7:0] |                   |     |          |            |        |      |    |  |  |

| 4Dh     | ReadCH6-MB  |           | unu               | sed |          | PWM [11:8] |        |      |    |  |  |

| 4Eh     | ReadCH7-LB  |           |                   |     | PV       | /M [7:0]   |        |      |    |  |  |

| 4Fh     | ReadCH7-MB  |           | unu               | sed |          | PWM [11:8] |        |      |    |  |  |

| 50h     | ReadCH8-LB  |           |                   |     | PV       | /M [7:0]   |        |      | -  |  |  |

| 51h     | ReadCH8-MB  |           | unu               | sed |          |            | PWM [1 | 1:8] |    |  |  |

| 52h     | ReadCH9-LB  |           |                   |     | PV       | /M [7:0]   |        |      |    |  |  |

| 53h     | ReadCH9-MB  |           | unu               | sed |          |            | PWM [1 | 1:8] | -  |  |  |

| 54h     | ReadCH10-LB |           |                   |     | PV       | /M [7:0]   |        |      | -  |  |  |

| 55h     | ReadCH10-MB |           | unu               | sed |          |            | PWM [1 | 1:8] |    |  |  |

| 56h     | ReadCH11-LB |           |                   |     | PV       | /M [7:0]   |        |      |    |  |  |

| 57h     | ReadCH11-MB |           | unu               | sed |          |            | PWM [1 | 1:8] |    |  |  |

| 58h     | ReadCH12-LB |           |                   |     | PV       | /M [7:0]   |        |      |    |  |  |

| 59h     | ReadCH12-MB |           | unu               | sed |          |            | PWM [1 | 1:8] |    |  |  |

#### Table 6. PWM-Feedback registers (only Read registers)

#### Table 7. Immediate OFF commands. Set duty cycle to zero (Read/Write)

| Address | Register   | D7  | D6  | D5  | D4  | D3   | D2   | D1   | D0  |

|---------|------------|-----|-----|-----|-----|------|------|------|-----|

| 30h     | IMMOFFREG1 | CH8 | CH7 | CH6 | CH5 | CH4  | CH3  | CH2  | CH1 |

| 31h     | IMMOFFREG2 |     | unu | sed |     | CH12 | CH11 | CH10 | CH9 |

ASL5xxxyHz

Product data sheet

Registers IMMOFFREG1 and IMMOFFREG2 are used to turn all the channels OFF immediately. That means 100 % duty cycle in the internal FET gate (switch in low ohmic state and bypassing the LEDs) and 0 % PWM duty cycle in the LED or LEDs associated to this channel. These registers can be sent to a selected IC or as a broadcast message, depending on the frame ID only (command bits). The microcontroller can control every channel individually.

#### Table 8. Start commands for each channel (Read/Write)

| Address | Register | D7  | D6  | D5  | D4  | D3   | D2   | D1   | D0  |

|---------|----------|-----|-----|-----|-----|------|------|------|-----|

| 32h     | START1   | CH8 | CH7 | CH6 | CH5 | CH4  | CH3  | CH2  | CH1 |

| 33h     | START2   |     | unu | sed |     | CH12 | CH11 | CH10 | CH9 |

Registers START1 and START2, are used to start the sequences. These commands should be sent after all the channels have been programmed with the desired values. The microcontroller can control every channel individually. Other way of starting a channel is programing the CURVEIDx resgister with NOW bit =1, but at least one previous START command must be performed from the moment the MLC startup.

#### 8.5 Delay coefficient – ASL50xxyHz

The delay coefficient can be set in the DELAYx register. See <u>Section 8.4.1 "Channel</u> programming registers map". This setting is individual for each channel and has a resolution of 8 bits. After the delay coefficient is set, a delay for a PWM curve can be programmed and the channel starts following the PWM dimming curve after the programmed step delay.

This feature on the ASL50xxyHz saves many software lines in the MCU and reduces the load on the communication bus. The combination of the delay and the fade-in/fade-out curves can be used in applications such as dynamic turn indicator or welcome scenarios.

The delay resolution is 4.09 ms in case the PWM frequency is set to 244 Hz or 2 ms if it is set to 488 Hz.

#### 8.6 Diagnostics

#### 8.6.1 Direct NTC input

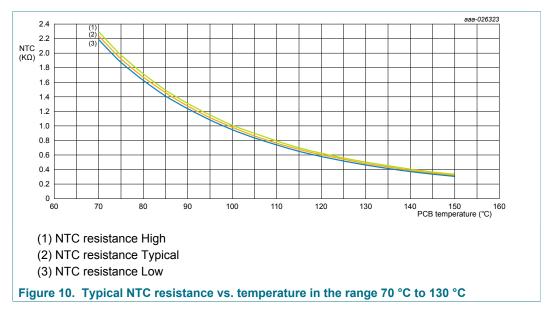

The MLC is able to read the voltage drop in an attached NTC from 0 V to 1.1 V. This analog voltage drop is converted to a digital value with an internal ADC. The customer can read the 6-bit digital value of this voltage drop in register 39h.

The MLC uses a continuos current of 25  $\mu$ A to check the NTC status. This check is to determine if an open or short condition is present. The MLC uses a current of 440  $\mu$ A to measure the voltage drop in the NTC and provide the digital value (only when CAN command 13 or 46 are sent). Figure 10 shows the measurement process. The microcontroller triggers the NTC read with command 13 for selective MLC or command 46 for broadcast trigger.

ASL5xxxyHz Matrix LED Controller (MLC)

### 8.6.2 Direct Identification resistor input

Eight resistors with 1 % precision can be connected to the ID pin to read the identification / characterization information. The current on the ID pin is fixed to 25  $\mu$ A ±10 %. The value of the resistor is determined at the MLC start-up and is available to the microcontroller in register 3Ah. The ID value is only read during device startup. To get the identification value, the microcontroller can read this register directly or ask for the IC diagnosis, the register 3Ah is included in the 8 bytes of diagnosis answer.

The voltage drop in the ID pin is read and converted to a digital value via an internal ADC. The ID resistors' values are not overlapping in ranges in <u>Table 9</u>.

| Resistor | 4.75 | 8.06 | 11.3 | 14.3 | 17.4 | 21.5 | 26.7 | 32.4 | [kΩ]   |

|----------|------|------|------|------|------|------|------|------|--------|

| Value    | 000  | 001  | 010  | 011  | 100  | 101  | 110  | 111  | binary |

Table 9. Possible identification resistors for nonoverlapping

#### 8.6.3 LED fault detection

Each PWM switch has an Open Circuit and a Short Circuit comparator, even when the system is in Limp Home mode.

**Open Circuit detection (OC):** The OC detection threshold can be set to 6 V ±1 V (default value) or 17 V ±1.5 V, see <u>Section 10 "ASL50xxyHz Register map"</u>. In case of an OC detection event, the PWM switch is closed and an error bit set. This process allows the IC to bypass this LED and the other LEDs to continue to operate. The bit flag can be reset by removing the supply voltage (V<sub>CC</sub>) or by a bus command writing a 1 in the register 34h, bit 1. In case of clearing the flags (writing in register 34h), the action is done dynamically and a power-on-reset is not necessary. If the open circuit was just a lapse, then the system recovers automatically when clearing the flags. The open circuit is immediately detected when the switch passes from low ohmic to high ohmic state.

**Short Circuit detection (SC):** The SC detection limit is set to  $1 \vee \pm 0.5 \vee$ . The system can use a blanking time of 16 µs (default) or 32 µs, depending on the driving current and the string capacitor. The blanking time can be selected in the internal MTP bit 4, register

60h. The blancking time is applicable from the moment the internal switch passes from a low ohmic to a high ohmic state.

When there is a detection of an SC, the error bit is set and the microcontroller is aware of the fail. The microcontroller can then decide whether to close the switch associated to the shorted LED or not. If the microcontroller decides to close the switch, the rest of the LED string can continue working and just the affected LED is bypassed.

Restore the fail bit flag by a bus command writing a 1 in the register 34h, bit 0 or removing the supply voltage. If the flag is restored with a CAN message (write a 1 in the CLEAR\_SC bit of register 34h), then the MLC does not need a power-on-reset. In addition, an automatic recheck action is executed by the IC to confirm whether the fail is still present or not. If the fail is still present, then the MLC will flag it again.

#### 8.6.4 Internal junction temperature warnings