# 1/4-Inch CMOS Image Sensor and Signal Processor

#### **General Description**

The ON Semiconductor AS0140AT is a 1.0 MP format digital image sensor and image sensor processor for automotive viewing applications. The device includes full auto-functions support (AWB and AE) and ALTM (Adaptive Local Tone Mapping) to enhance HDR video. The AS0140AT implements a high-sensitivity 3.0  $\mu m$  pixel with DR-Pix  $^{\text{TM}}$  technology, and advanced noise reduction, to enable excellent low-light performance. It can be operated in interlaced (NTSC or PAL) or progressive modes, and captures images in either linear or high dynamic range modes. The AS0140AT may be operated in video (master) mode or in single frame trigger mode, providing flexibility for multi-camera systems.

**Table 1. KEY PERFORMANCE PARAMETERS**

| Parameter                         | Typical Value                                                                      |  |  |  |  |

|-----------------------------------|------------------------------------------------------------------------------------|--|--|--|--|

| Optical Format                    | 1/4"                                                                               |  |  |  |  |

| Pixel Size and Type               | 3.0 μm × 3.0 μm                                                                    |  |  |  |  |

| Active Pixels                     | 1280 (H) × 800 (V) (Entire Array)                                                  |  |  |  |  |

| NTSC Output                       | 720 (H) × 487 (V)                                                                  |  |  |  |  |

| PAL Output                        | 720 (H) × 576 (V)                                                                  |  |  |  |  |

| Input Clock Range                 | 6–30 MHz                                                                           |  |  |  |  |

| Frame Rate (Note 1)               | 60 fps at 720p                                                                     |  |  |  |  |

| Color Filter Array                | RGB Bayer                                                                          |  |  |  |  |

| Shutter Type                      | Electronic Rolling Shutter                                                         |  |  |  |  |

| Output Interface                  | Analog Composite, up to 16-bit Parallel Digital Output                             |  |  |  |  |

| Output Data Formats               | YUV422 8-bit,10-bit, and 10 to 12-bit<br>Tone-mapped Bayer                         |  |  |  |  |

| Maximum Output<br>Clock Frequency | Parallel clock up to 84 MHz                                                        |  |  |  |  |

| Supply Voltage                    | VDDIO: 2.8 V Nominal VDD: 1.8 V Nominal VAA: 2.8 V Nominal VDDA_DAC: 3.3 V Nominal |  |  |  |  |

| Power Consumption (Typical)       | 506 mW (Linear Mode NTSC)<br>527 mW (HDR Mode NTSC)                                |  |  |  |  |

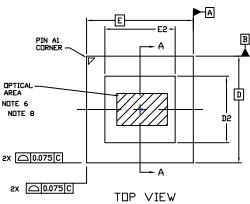

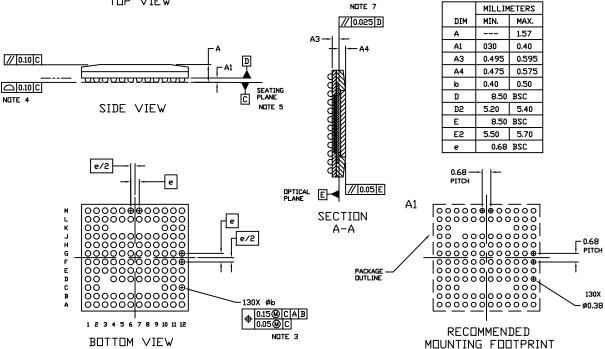

| Package                           | 8.5 mm × 8.5 mm 130-pin BGA                                                        |  |  |  |  |

| Temperature                       | Operating Temperature –40°C to 105°C                                               |  |  |  |  |

Maximum frame rates depend on output interface and data format configuration used.

#### ON Semiconductor®

#### www.onsemi.com

#### **Features**

- 3.0 µm Pixel with ON Semiconductor DR-Pix Technology

- Superior Low-light Performance

- 45 fps at 1.0 MP, 60 fps at 720p

- Linear or High Dynamic Range Video

- Color Processing Optimized for HDR Video Operation

- Color and Gamma Correction

- Auto Exposure, Auto White Balance, 50/60 Hz Auto Flicker Detection and Avoidance

- Adaptive Local Tone Mapping (ALTM)

- Programmable Spatial Transform Engine (STE)

- Pre-rendered Graphical Overlay

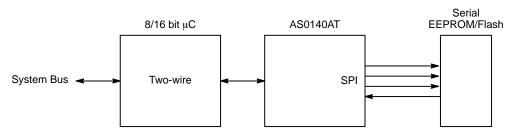

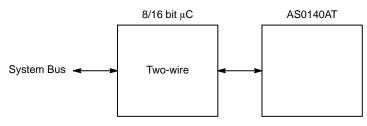

- Two-wire Serial Programming Interface (CCIS)

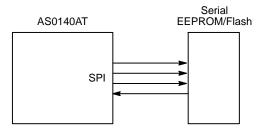

- Interface to Low-cost Flash or EEPROM through SPI Bus (to Configure and Load Patches, etc.)

- High-level Host Command Interface

- Standalone Operation Supported

- Up to 5 GPIO

- Support for External LED or Xenon Flash

- Fail-safe IO

- Multi-camera Synchronization Support

- Integrated Video Encoder for NTSC/PAL with Overlay Capability and 10-bit I-DAC

- Temperature Sensor

#### **Applications**

- Surround, Rear and Front View Cameras

- Blind Spot/Side Mirror Replacement Cameras

- Automotive Viewing/Processing Fusion Cameras

#### **ORDERING INFORMATION**

**Table 2. ORDERABLE PART NUMBERS**

| Part Number             | Description       | Orderable Product Attribute Description                                        |

|-------------------------|-------------------|--------------------------------------------------------------------------------|

| AS0140AT2C00XUSM0-DPBR  | 0° CRA, RGB iEBGA | Dry Pack with Protective Film, Double Side BBAR Glass, Engineering Sample      |

| AS0140AT2C00XUSM0-DRBR  | 0° CRA, RGB iEBGA | Dry Pack w/o Protective Film, Double Side BBAR Glass, Engineering Sample       |

| AS0140AT2C00XUSM0-TPBR  | 0° CRA, RGB iEBGA | Tape and Reel with Protective Film, Double Side BBAR Glass, Engineering Sample |

| AS0140AT2C00XUSM0-TRBR  | 0° CRA, RGB iEBGA | Tape and Reel w/o Protective Film, Double Side BBAR Glass, Engineering Sample  |

| AS0140AT2C00XUSMH3-GEVB | RGB Headboard     |                                                                                |

| MARS1-AS0140AT2-GEVB    | RGB MARS Board    |                                                                                |

#### **Function Overview**

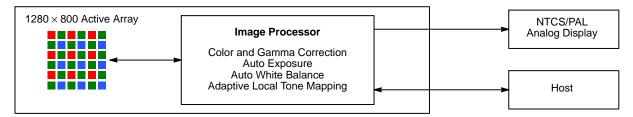

Figure 1 shows the typical configuration of the AS0140AT in a camera system. On the host side, a two-wire

serial interface is used to control the operation of the AS0140AT, and image data is transferred using the analog or parallel interface between the AS0140AT and the host.

Figure 1. AS0140AT Connectivity

# **System Interfaces**

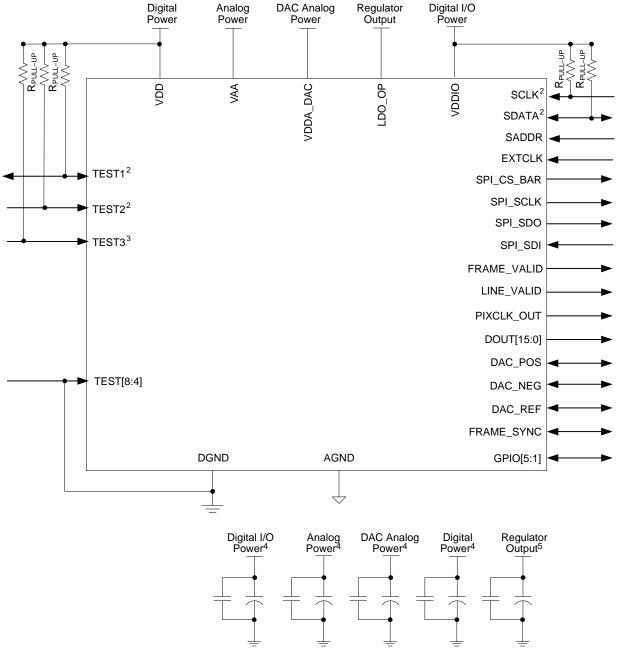

Figure 2 shows typical AS0140AT device connections.

All power supply rails must be decoupled from ground using capacitors as close as possible to the package.

Table 3 provides pin descriptions for the AS0140AT.

#### Notes:

- 1. This typical configuration shows only one scenario out of multiple possible variations for this device.

- 2. ON Semiconductor recommends a 1.5 kΩ resistor value for the two-wire serial interface R<sub>PULL-UP</sub>. However, greater values may be used for slower two–wire serial transmission speed.

- 3. ON Semiconductor recommends a 10  $k\dot{\Omega}$  resistor value for TEST3 to avoid potential power–up issues.

- 4. ON Semiconductor recommends that  $0.1 \,\mu\text{F}$  and  $10 \,\mu\text{F}$  decoupling capacitors for each power supply are mounted as close as possible to the pin. Actual values and numbers may vary depending on layout and design consideration.

- 5. The decoupling capacitors for the regulator input and output should have a value of 1.0 μF. The capacitors should be ceramic and need to have X5R or X7R dielectric.

**Figure 2. Typical Device Configuration**

**Table 3. PIN DESCRIPTION**

| Pin Number         | Pin Name    | Туре   | Description                                                                                                                                                                                                                                                                                                                 |

|--------------------|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLOCK AND RESET    | 1           |        |                                                                                                                                                                                                                                                                                                                             |

| L9                 | EXTCLK      | Input  | Master Input Clock                                                                                                                                                                                                                                                                                                          |

| F1                 | STANDBY     | Input  | Standby Mode Control, Active HIGH                                                                                                                                                                                                                                                                                           |

| B10                | RESET_BAR   | Input  | Master reset signal, active LOW. This signal has an internal pull up.                                                                                                                                                                                                                                                       |

| B8                 | FRAME_SYNC  | Input  | This signal is used to synchronize to external sources or multiple cameras together. This signal should be connected to GND if not used.                                                                                                                                                                                    |

| L12                | TRIGGER_OUT | Output | If utilizing trigger modes, TRIGGER_OUT should be connected to the TRIGGER pin; otherwise, this signal should be left unconnected.                                                                                                                                                                                          |

| H11                | TRIGGER     | Input  | If utilizing trigger modes, TRIGGER_OUT should be connected to the TRIGGER pin; otherwise, this signal should be connected to GND.                                                                                                                                                                                          |

| REGISTER INTERFACE | <u>.</u>    |        |                                                                                                                                                                                                                                                                                                                             |

| В3                 | SCLK        | Input  | SCLK: Two-wire Serial Interface Clock (Host Interface)                                                                                                                                                                                                                                                                      |

| C12                | SDATA       | I/O    | Two-wire Serial Interface Data (Host Interface)                                                                                                                                                                                                                                                                             |

| А7                 | SADDR       | Input  | Selects device address for the two-wire slave serial interface. When connected to GND the device ID is 0x90. When wired to VDDIO, a device ID of 0xBA is selected.                                                                                                                                                          |

| SPI INTERFACE      |             |        |                                                                                                                                                                                                                                                                                                                             |

| J1                 | SPI_SCLK    | Output | Clock Output for Interfacing to an External SPI Flash or EEPROM Memory                                                                                                                                                                                                                                                      |

| A8                 | SPI_SDI     | Input  | Data in from SPI flash or EEPROM memory. When no SPI device is fitted, this signal is used to determine whether the AS0140AT should auto-configure:  0: Do not auto-configure; Two-wire interface will be used to configure the device (host-config mode)  1: Auto-configure.  This signal has an internal pullup resistor. |

| A4                 | SPI_SDO     | Output | Data Out to SPI Flash or EEPROM Memory                                                                                                                                                                                                                                                                                      |

| A5                 | SPI_CS_BAR  | Output | Chip Select Out to SPI Flash or EEPROM Memory                                                                                                                                                                                                                                                                               |

| PIXEL DATA OUTPUT  |             |        |                                                                                                                                                                                                                                                                                                                             |

| H1                 | FRAME_VALID | Output | Frame Valid Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                              |

| B4                 | LINE_VALID  | Output | Line Valid Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| B5                 | PIXCLK_OUT  | Output | Pixel Clock Output                                                                                                                                                                                                                                                                                                          |

| E2                 | DOUT0       | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| M10                | DOUT1       | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| L8                 | DOUT2       | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| E12                | DOUT3       | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| L10                | DOUT4       | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| L3                 | DOUT5       | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| D2                 | DOUT6       | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| M9                 | DOUT7       | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| D12                | DOUT8       | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| J2                 | DOUT9       | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| H2                 | DOUT10      | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

| E1                 | DOUT11      | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                                               |

Table 3. PIN DESCRIPTION (continued)

| Table 3. PIN DESCRIPTION                                                                                                                                                           | ,        | T      | Decription                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number                                                                                                                                                                         | Pin Name | Туре   | Description                                                                                                                                                                                                                                                                                    |

| PIXEL DATA OUTPUT                                                                                                                                                                  |          | 1      |                                                                                                                                                                                                                                                                                                |

| C2                                                                                                                                                                                 | DOUT12   | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                  |

| A10                                                                                                                                                                                | DOUT13   | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                  |

| G1                                                                                                                                                                                 | DOUT14   | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                  |

| F12                                                                                                                                                                                | DOUT15   | Output | Pixel Data Output (Synchronous to PIXCLK_OUT)                                                                                                                                                                                                                                                  |

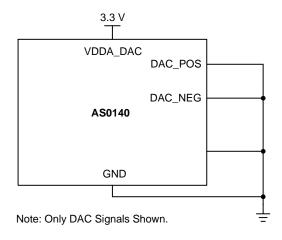

| COMPOSITE VIDEO OUTPUT                                                                                                                                                             |          |        |                                                                                                                                                                                                                                                                                                |

| M3                                                                                                                                                                                 | DAC_REF  | Output | External Reference Resistor for Video DAC                                                                                                                                                                                                                                                      |

| L7                                                                                                                                                                                 | DAC_POS  | Output | Positive video DAC output in differential mode. Video DAC output in single-ended mode. This interface is enabled by default using NTSC/PAL signaling. For applications where composite video output is not required, the video DAC can be placed in a power-down state under software control. |

| L6                                                                                                                                                                                 | DAC_NEG  | Output | Negative Video DAC Output in Differential Mode                                                                                                                                                                                                                                                 |

| GPIO                                                                                                                                                                               |          |        |                                                                                                                                                                                                                                                                                                |

| G2                                                                                                                                                                                 | GPIO_1   | I/O    | General Purpose Digital I/O                                                                                                                                                                                                                                                                    |

| C1                                                                                                                                                                                 | GPIO_2   | I/O    | General Purpose Digital I/O                                                                                                                                                                                                                                                                    |

| D1                                                                                                                                                                                 | GPIO_3   | I/O    | General Purpose Digital I/O                                                                                                                                                                                                                                                                    |

| F2                                                                                                                                                                                 | GPIO_4   | I/O    | General Purpose Digital I/O                                                                                                                                                                                                                                                                    |

| А3                                                                                                                                                                                 | GPIO_5   | I/O    | General Purpose Digital I/O                                                                                                                                                                                                                                                                    |

| POWER                                                                                                                                                                              |          | •      |                                                                                                                                                                                                                                                                                                |

| E10, F10, G10, H12, J12                                                                                                                                                            | AGND     | Supply | Analog Ground                                                                                                                                                                                                                                                                                  |

| K2, D4, E4, F4, G4, H4, J4,<br>L4, D5, E5, F5, G5, H5, J5,<br>D6, E6, F6, G6, H6, J6, B7,<br>D7, E7, F7, G7, H7, J7, D8,<br>E8, F8, G8, H8, J8, B9, D9,<br>E9, F9, G9, H9, J9, G12 | DGND     | Supply | Digital Ground                                                                                                                                                                                                                                                                                 |

| C10, D10, D11, E11                                                                                                                                                                 | VDDIO    | Supply | I/O Supply Power                                                                                                                                                                                                                                                                               |

| H10, J10, K10, K12                                                                                                                                                                 | VAA      | Supply | Analog Power                                                                                                                                                                                                                                                                                   |

| E3, F3, G3, H3, J3, K3, M4,<br>M5, M7                                                                                                                                              | VDD      | Supply | Digital Power                                                                                                                                                                                                                                                                                  |

| M6                                                                                                                                                                                 | VDDA_DAC | Supply | Video DAC Analog Power                                                                                                                                                                                                                                                                         |

| A6                                                                                                                                                                                 | LDO_OP   | Output | Output from on Chip 1.8 to 1.2 V Regulator                                                                                                                                                                                                                                                     |

| TEST PINS                                                                                                                                                                          |          | - I    | ,                                                                                                                                                                                                                                                                                              |

| F11                                                                                                                                                                                | TEST1    | Input  | Must be Pulled Up via 1.5 kΩ to V <sub>DD</sub> for Normal Operation                                                                                                                                                                                                                           |

| G11                                                                                                                                                                                | TEST2    | Input  | Must be Pulled Up via 1.5 k $\Omega$ to V <sub>DD</sub> for Normal Operation                                                                                                                                                                                                                   |

| A12                                                                                                                                                                                | TEST3    | Input  | Recommended Pull Up to V <sub>DD</sub>                                                                                                                                                                                                                                                         |

| B6                                                                                                                                                                                 | TEST4    | Input  | Must be Tied to GND for Normal Operation                                                                                                                                                                                                                                                       |

| K11                                                                                                                                                                                | TEST5    | Input  | Must be Tied to GND for Normal Operation                                                                                                                                                                                                                                                       |

| L2                                                                                                                                                                                 | TEST6    | Input  | Must be Tied to GND for Normal Operation                                                                                                                                                                                                                                                       |

| L11                                                                                                                                                                                | TEST7    | Input  | Must be Tied to GND for Normal Operation                                                                                                                                                                                                                                                       |

| M8                                                                                                                                                                                 | TEST8    | Input  | Must be Tied to GND for Normal Operation                                                                                                                                                                                                                                                       |

| A1, B1, K1, L1, M1, A2, B2,<br>M2, L5, A9, A11, B11, C11,<br>J11, M11, B12, M12                                                                                                    | NC NC    |        |                                                                                                                                                                                                                                                                                                |

**Table 4. PACKAGE PINOUT**

|   | 1               | 2      | 3           | 4              | 5              | 6            | 7           | 8              | 9      | 10            | 11      | 12              |

|---|-----------------|--------|-------------|----------------|----------------|--------------|-------------|----------------|--------|---------------|---------|-----------------|

| Α | NC              | NC     | GPIO_5      | SPI_<br>SDO    | SPI_CS_<br>BAR | LDO_OP       | SADDR       | SPI_SDI        | NC     | DOUT13        | NC      | TEST3           |

| В | NC              | NC     | SCLK        | LINE_<br>VALID | PIXCLK_<br>OUT | TEST4        | DGND        | FRAME_<br>SYNC | DGND   | RESET_<br>BAR | NC      | NC              |

| С | GPIO_2          | DOUT12 |             |                |                |              |             |                |        | VDDIO         | NC      | SDATA           |

| D | GPIO_3          | DOUT6  |             | DGND           | DGND           | DGND         | DGND        | DGND           | DGND   | VDDIO         | VDDIO   | DOUT8           |

| Е | DOUT11          | DOUT0  | VDD         | DGND           | DGND           | DGND         | DGND        | DGND           | DGND   | AGND          | VDDIO   | DOUT3           |

| F | STANDBY         | GPIO_4 | VDD         | DGND           | DGND           | DGND         | DGND        | DGND           | DGND   | AGND          | TEST1   | DOUT15          |

| G | DOUT14          | GPIO_1 | VDD         | DGND           | DGND           | DGND         | DGND        | DGND           | DGND   | AGND          | TEST2   | DGND            |

| Н | FRAME_<br>VALID | DOUT10 | VDD         | DGND           | DGND           | DGND         | DGND        | DGND           | DGND   | VAA           | TRIGGER | AGND            |

| J | SPI_SCL<br>K    | DOUT9  | VDD         | DGND           | DGND           | DGND         | DGND        | DGND           | DGND   | VAA           | NC      | AGND            |

| K | NC              | DGND   | VDD         |                |                |              |             |                |        |               | TEST5   | VAA             |

| L | NC              | TEST6  | DOUT5       | DGND           | NC             | DAC_<br>NEG  | DAC_<br>POS | DOUT2          | EXTCLK | DOUT4         | TEST7   | TRIGGER_<br>OUT |

| М | NC              | NC     | DAC_<br>REF | VDD            | VDD            | VDDA_<br>DAC | VDD         | TEST8          | DOUT7  | DOUT1         | NC      | NC              |

# **On-Chip Regulator**

The AS0140AT has an on-chip regulator, the output from the regulator is  $1.2\ V.$

# **Power-Up Sequence**

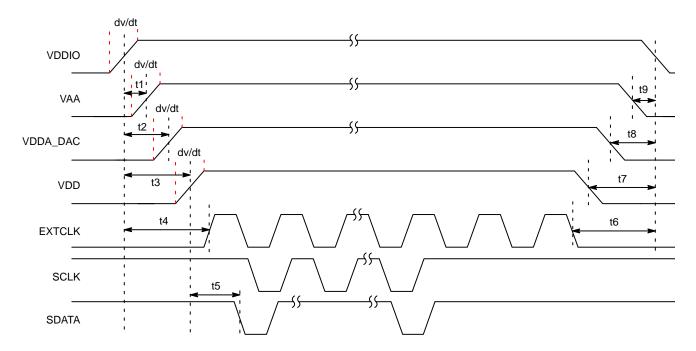

Powering up the AS0140AT requires voltages to be applied in a particular order, as seen in Figure 3. The timing requirements are shown in Table 5. The AS0140AT includes a power-on reset feature that initiates a reset upon power up of the AS0140AT.

Figure 3. Power-Up and Power-Down Sequence

Table 5. POWER-UP AND POWER-DOWN SIGNAL TIMING

| Symbol | Parameter                          | Min    | Тур | Max | Unit          |

|--------|------------------------------------|--------|-----|-----|---------------|

| t1     | Delay from VDDIO to VAA            | 0      | -   | 50  | ms            |

| t2     | Delay from VDDIO to VDDA_DAC       | 0      | -   | 50  | ms            |

| t3     | Delay from VDDIO to VDD            | 0      | -   | 50  | ms            |

| t4     | EXTCLK Activation                  | t3 + 1 | -   | -   | ms            |

| t5     | First Serial Command               | 100    | -   | -   | EXTCLK Cycles |

| t6     | EXTCLK Cutoff                      | t7     | -   | -   | ms            |

| t7     | Delay from VDD to VDDIO            | 0      | -   | 50  | ms            |

| t8     | Delay from VDDA_DAC to VDDIO       | 0      | -   | 50  | ms            |

| t9     | Delay from VAA to VDDIO            | 0      | -   | 50  | ms            |

| dv/dt  | Power Supply Ramp Time (Slew Rate) | _      | _   | 0.1 | V/µs          |

<sup>1.</sup> It is critical that VAA is not powered up after VDD. It must be powered before or at least at the same time. If the case happens that VAA is powered after VDD then sensor may have functionality issues and will experience high current draw on this supply.

#### Reset

The AS0140AT has three types of reset available:

- A hard reset is issued by toggling the RESET\_BAR signal

- A soft reset is issued by writing commands through the two-wire serial interface

- An internal power-on reset

Table 6 shows the output states when the part is in various states

# **Table 6. OUTPUT STATES**

|                                                 | Hardwar                     | e States                    |                             | Firmwar                     |                            |                            |                                                                                   |

|-------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|----------------------------|----------------------------|-----------------------------------------------------------------------------------|

| Name                                            | Reset State                 | Default State               | Hard Standby                | Soft Standby                | Streaming                  | Idle                       | Notes                                                                             |

| EXTCLK                                          | (Clock Running or Stopped)  | (Clock Running)             | (Clock Running or Stopped)  | (Clock Running)             | (Clock Running)            | (Clock Running)            | Input                                                                             |

| RESET_BAR                                       | (Asserted)                  | (Negated)                   | (Negated)                   | (Negated)                   | (Negated)                  | (Negated)                  | Input                                                                             |

| SCLK                                            | N/A                         | N/A                         | (Clock Running or Stopped)  | (Clock Running or Stopped)  | (Clock Running or Stopped) | (Clock Running or Stopped) | Input. Must always be driven to a valid logic level.                              |

| SDATA                                           | High-impedance              | High-impedance              | High-impedance              | High-impedance              |                            |                            | Input/Output. A valid logic level should be established by pull-up.               |

| SADDR                                           | N/A                         | N/A                         | N/A                         | N/A                         | N/A                        | N/A                        | Input. Must always be driven to a valid logic level.                              |

| FRAME_SYNC                                      | N/A                         | N/A                         | N/A                         | N/A                         | N/A                        | N/A                        | Input. Must always be driven to a valid logic level.                              |

| STANDBY                                         | N/A                         | (Negated)                   | (Asserted)                  | (Negated)                   | (Negated)                  | (Negated)                  | Input. Must always be driven to a valid logic level.                              |

| SPI_SCLK                                        | High-impedance              | Driven, Logic 0             | Driven, Logic 0             | Driven, Logic 0             |                            |                            | Output                                                                            |

| SPI_SDI                                         | Internal Pull-up<br>Enabled | Internal Pull-up<br>Enabled | Internal Pull-up<br>Enabled | Internal Pull-up<br>Enabled |                            |                            | Input. Internal pull-up permanently enabled.                                      |

| SPI_SDO                                         | High-impedance              | Driven, Logic 0             | Driven, Logic 0             | Driven, Logic 0             |                            |                            | Output                                                                            |

| SPI_CS_BAR                                      | High-impedance              | Driven, Logic 1             | Driven, Logic 1             | Driven, Logic 1             |                            |                            | Output                                                                            |

| FV_OUT,<br>LV_OUT,<br>PIXCLK_OUT,<br>DOUT[15:0] | High-impedance              | Varied                      | Driven if Used              | Driven if Used              | Driven if Used             | Driven if Used             | Output. Default state dependent of configuration.                                 |

| DAC_POS<br>DAC_NEG                              | Varied                      | Varied                      | Driven if Used              | Driven if Used              | Driven if Used             | Driven if Used             | Output. Default state dependent on configuration. Tie to ground if VDAC not used. |

| DAC_REF                                         | N/A                         | N/A                         | N/A                         | N/A                         | N/A                        | N/A                        | Output. Requires reference resistor. Tie to ground if VDAC not used.              |

Table 6. OUTPUT STATES (continued)

|             | Hardwar        | e States                      |                | Firmwar        |                |                |                                                                                            |

|-------------|----------------|-------------------------------|----------------|----------------|----------------|----------------|--------------------------------------------------------------------------------------------|

| Name        | Reset State    | Default State                 | Hard Standby   | Soft Standby   | Streaming      | Idle           | Notes                                                                                      |

| GPIO[5:2]   | High-impedance | Input, then<br>High-impedance | Driven if Used | Driven if Used | Driven if Used | Driven if Used | Input/Output. After reset, these pins are sampled as inputs as part of auto-configuration. |

| GPIO1       | High-impedance | High-impedance                | High-impedance | High-impedance | High-impedance | High-impedance |                                                                                            |

| TRIGGER_OUT | N/A            | N/A                           | N/A            | N/A            | N/A            | N/A            | Output. Tie to TRRIGER if used; otherwise leave NC.                                        |

| TRIGGER     | N/A            | N/A                           | N/A            | N/A            | N/A            | N/A            | Input. Tie to TRRIGER_OUT if used; otherwise tie to ground.                                |

| TEST[3:1]   | N/A            | N/A                           | N/A            | N/A            | N/A            | N/A            | Input. A valid logic level should be established by pull-up.                               |

| TEST[8:4]   | N/A            | N/A                           | N/A            | N/A            | N/A            | N/A            | Input. Must always be driven to GND.                                                       |

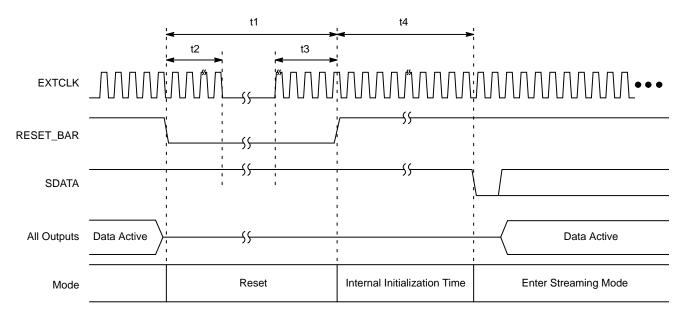

# Hard Reset

The AS0140AT enters reset state when the external RESET\_BAR is asserted LOW, as shown in Figure 4. All the output signals will be in High-Z state.

Figure 4. Hard Reset Operation

**Table 7. HARD RESET**

| Symbol | Parameter                                                         | Min | Тур | Max | Unit          |

|--------|-------------------------------------------------------------------|-----|-----|-----|---------------|

| t1     | RESET_BAR Pulse Width                                             | 50  | -   | _   | EXTCLK Cycles |

| t2     | Active EXTCLK Required after RESET_BAR Asserted                   | 10  | -   | -   | EXTCLK Cycles |

| t3     | Active EXTCLK Required before RESET_BAR De-asserted               | 10  | _   | _   | EXTCLK Cycles |

| t4     | First Two-wire Serial Interface Communication after RESET is HIGH | 100 | _   | _   | EXTCLK Cycles |

# Soft Reset

A soft reset sequence to the AS0140AT can be activated by writing to a register through a two-wire serial interface.

#### **Hard Standby Mode**

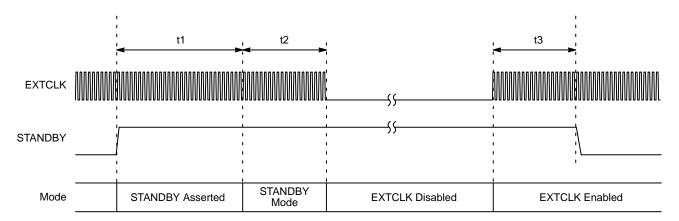

The AS0140AT can enter hard standby mode by using external STANDBY signal, as shown in Figure 5.

Entering Standby Mode

• Assert STANDBY signal HIGH.

Exiting Standby Mode

• De-assert STANDBY signal LOW.

Figure 5. Hard Standby Operation

**Table 8. HARD STANDBY SIGNAL TIMING**

| Symbol | Parameter                                            | Min | Тур | Max      | Unit    |

|--------|------------------------------------------------------|-----|-----|----------|---------|

| t1     | Standby Entry Complete                               | -   | -   | 2 Frames | Lines   |

| t2     | Active EXTCLK Required after Going into STANDBY Mode | 10  | -   | -        | EXTCLKs |

| t3     | Active EXTCLK Required before STANDBY De-asserted    | 10  | -   | -        | EXTCLKs |

# **Multi-Camera Synchronization Support**

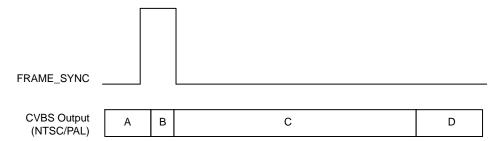

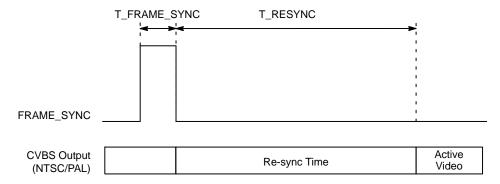

The AS0140AT supports multi-camera synchronization through the FRAME\_SYNC pin.

The behavior will be different depending if the user is using interlaced or progressive mode.

When using the interlaced modes, on the rising edge of FRAME\_SYNC this will cause the output to stop the current frame (A) and during B the image output will be

indeterminate. On the falling edge of FRAME\_SYNC this will cause the re-synchronization to begin, this will continue for a period (C), during C black fields will be output. The resynchronized interlaced signal will be available at D. During C if the user toggles the FRAME\_SYNC input the AS0140AT will ignore it, the user cannot re-synchronize again until at D.

Figure 6. Frame Sync Behavior with Interlaced Mode

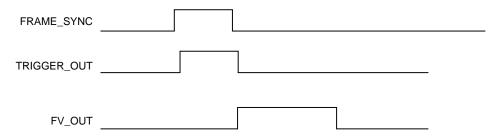

When using progressive mode, the host (or controlling entity) 'broadcasts' a sync-pulse to all cameras within the system that triggers capture. The AS0140AT will propagate the signal to the TRIGGER\_OUT pin, and subsequently to the attached sensor's TRIGGER pin.

The AS0140AT supports two different trigger modes when using progressive output. The first mode supported is 'single-shot'; this is when the trigger pulse will cause one frame to be output from the AS0140AT (see Figure 7).

Figure 7. Single-Shot Mode

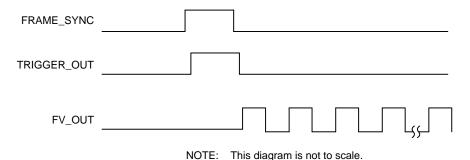

The second mode supported is called 'continuous', this is when a trigger pulse will cause the part to continuously output frames, see Figure 8. This mode would be especially useful for applications which have multiple sensors and need to have their video streams synchronized (for example, surround view or panoramic view applications).

-

Figure 8. Continuous Mode

When two or more cameras have a signal applied to the FRAME\_SYNC input at the same time, the respective FRAME\_VALID signals would be synchronized within 5

PIXCLK\_OUT cycles. This assumes that all cameras have the same configuration settings and that the exposure time is the same.

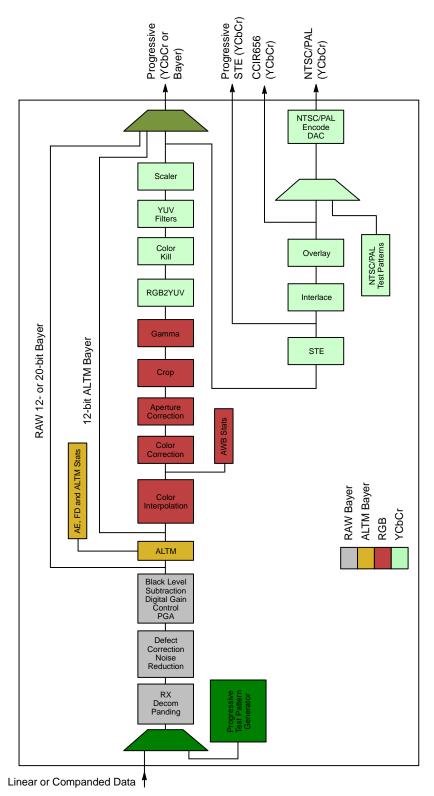

#### **Image Flow Processor**

Image and color processing in the AS0140AT is implemented as an image flow processor (IFP) coded in hardware logic. During normal operation, the embedded microcontroller will automatically adjust the operating

parameters. For normal operation of the AS0140AT, streams of raw image data are fed into the color pipeline. The user also has the option to select a number of test patterns to be input instead of sensor data. The IFP is broken down into different sections, as outlined in Figure 9.

Figure 9. AS0140AT IFP

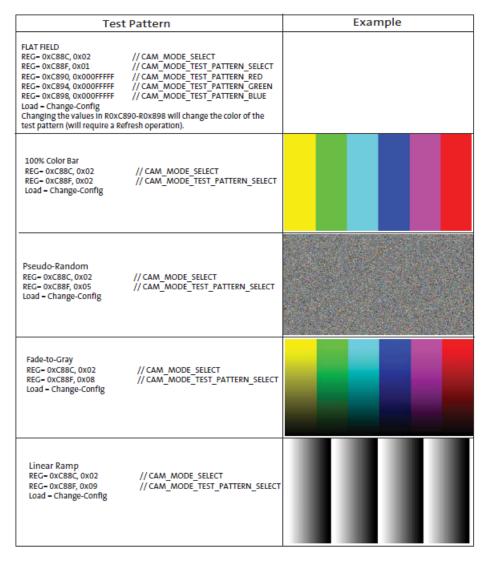

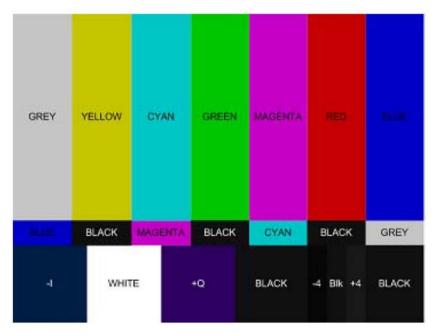

#### Test Patterns

The AS0140AT has a number of test patterns that are available when using the progressive NTSC and PAL modes. The test patterns can be selected by programming variables. To enter test pattern mode, set R0xC88F to 0x02

and issue a Change-Config request; to exit this mode, set R0xC88F to 0x00, and issue a Change-Config request.

NTSC and PAL test patterns can only be selected when the device is configured for interlaced operation.

#### **Progressive Test Patterns:**

Figure 10. Progressive Test Patterns

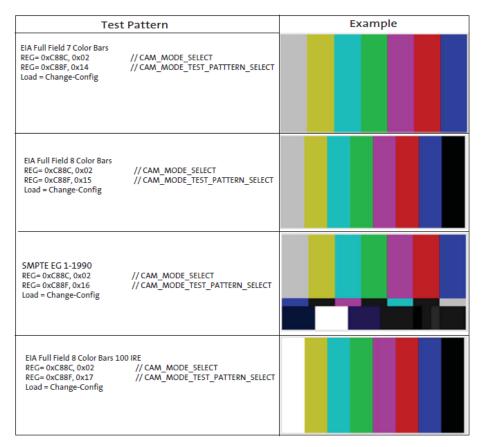

#### NTSC Test Patterns:

Figure 11. NTSC Test Patterns

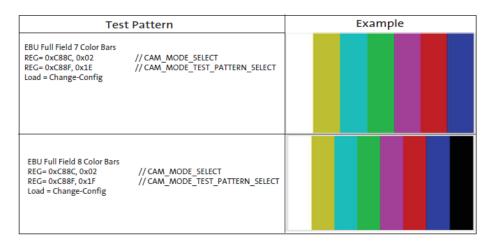

# PAL Test Patterns:

Figure 12. PAL Test Patterns

Each NTSC/PAL test pattern consists of seven or eight color bars (white, yellow, cyan, green, magenta, red, blue and optionally black). The Y, Cb and Cr values for each bar are detailed in Table 9.

For the NTSC SMPTE test pattern it is also required to generate –I, +Q, –4 black and +4 black.

Table 9. NTSC/PAL TEST PATTERN VALUES

|    | Nominal<br>Range | White<br>100% | White<br>75% | Yellow | Cyan | Green | Magenta | Red | Blue | Black | -1  | -Q  | -4 Black | +4 Black |

|----|------------------|---------------|--------------|--------|------|-------|---------|-----|------|-------|-----|-----|----------|----------|

| Υ  | 16 to 235        | 235           | 180          | 162    | 131  | 112   | 84      | 65  | 35   | 16    | 16  | 16  | 7        | 25       |

| Cb | 16 to 240        | 128           | 128          | 44     | 156  | 72    | 184     | 100 | 212  | 128   | 156 | 171 | 128      | 128      |

| Cr | 16 to 240        | 128           | 128          | 142    | 44   | 58    | 198     | 212 | 114  | 128   | 97  | 148 | 128      | 128      |

Figure 13. Test Pattern

#### Defect Correction

Image stream processing commences with the defect correction function immediately after data decompanding.

To obtain defect free images, the pixels marked defective during sensor readout and the pixels determined defective by the defect correction algorithms are replaced with values derived from the non-defective neighboring pixels. This image processing technique is called defect correction.

#### AdaCD (Adaptive Color Difference)

Automotive applications require good performance in extremely low light, even at high temperature conditions. In these stringent conditions the image sensor is prone to higher noise levels, and so efficient noise reduction techniques are required to circumvent this sensor limitation and deliver a high quality image to the user.

#### Black Level Subtraction and Digital Gain

After noise reduction, the pixel data goes through black level subtraction and multiplication of all pixel values by a programmable digital gain. Independent color channel digital gain can be adjusted with registers. Black level subtraction (to compensate for sensor data pedestal) is a single value applied to all color channels. If the black level subtraction produces a negative result for a particular pixel, the value of this pixel is set to 0.

#### Positional Gain Adjustments

Lenses tend to produce images whose brightness is significantly attenuated near the edges. There are also other factors causing fixed pattern signal gradients in images captured by image sensors. The cumulative result of all these factors is known as image shading. The AS0140AT has an embedded shading correction module that can be programmed to counter the shading effects on each individual R, Gb, Gr, and B color signal.

#### **The Correction Function:**

The correction functions can then be applied to each pixel value to equalize the response across the image as follows:

$$P_{corrected}$$

(row, col) =  $P_{sensor}$  (row, col) · f (row, col) (eq. 1)

where P are the pixel values and f is the color dependent correction functions for each color channel.

#### Adaptive Local Tone Mapping

Real world scenes often have very high dynamic range (HDR) that far exceeds the electrical dynamic range of the imager. Dynamic range is defined as the luminance ratio between the brightest and the darkest object in a scene. In recent years many technologies have been developed to capture the full dynamic range of real world scenes. For example, the multiple exposure method is widely adopted

for capturing high dynamic range images, which combines a series of low dynamic range images of the same scene taken under different exposure times into a single HDR image.

Even though the new digital imaging technology enables the capture of the full dynamic range, low dynamic range display devices are the limiting factor. Today's typical LCD monitor has contrast ratio around 1,000:1; however, it is not typical for an HDR image (the contrast ratio for an HDR image is around 250,000:1). Therefore, in order to reproduce HDR images on a low dynamic range display device, the captured high dynamic range must be compressed to the available range of the display device. This is commonly called tone mapping.

Tone mapping methods can be classified into global tone mapping and local tone mapping. Global tone mapping methods apply the same mapping function to all pixels. global tone mapping methods computationally simple and easy to use solutions, they often cause loss of contrast and detail. A local tone mapping is thus necessary in addition to global tone mapping for the reproduction of visually more appealing images that also reveal scene details that are important for automotive safety and surveillance applications. Local tone mapping methods use a spatially variable mapping function determined by the neighborhood of a pixel, which allows it to increase the local contrast and the visibility of some details of the image. Local methods usually yield more pleasing results because they exploit the fact that human vision is more sensitive to local contrast.

ON Semiconductor's ALTM solution significantly improves the performance over global tone mapping. ALTM is directly applied to the Bayer domain to compress the dynamic range from 20-bit to 12-bit. This allows the regular color pipeline to be used for HDR image rendering.

#### Color Interpolation

In the raw data stream fed by the external sensor to the IFP, each pixel is represented by a 20- or 12-bit integer number, which can be considered proportional to the pixel's response to a one-color light stimulus, red, green, or blue, depending on the pixel's position under the color filter array. Initial data processing steps, up to and including ALTM, preserve the one-color-per-pixel nature of the data stream, but after ALTM it must be converted to a three-colors-per-pixel stream appropriate for standard color processing. The conversion is done by an edge-sensitive color interpolation module. The module pads the incomplete color information available for each pixel with information extracted from an appropriate set of neighboring pixels. The algorithm used to select this set and extract the information seeks the best compromise between preserving edges and filtering out high frequency noise in flat field areas. The edge threshold can be set through register settings.

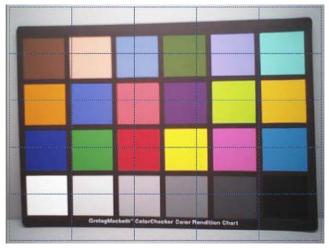

Color Correction and Aperture Correction

To achieve good color fidelity of the IFP output, interpolated RGB values of all pixels are subjected to color correction. The IFP multiplies each vector of three pixel colors by a  $3\times3$  color correction matrix. The three components of the resulting color vector are all sums of three 10-bit numbers. The color correction matrix can be either programmed by the user or automatically selected by the auto white balance (AWB) algorithm implemented in the IFP. Color correction should ideally produce output colors that are corrected for the spectral sensitivity and color crosstalk characteristics of the image sensor. The optimal values of the color correction matrix elements depend on those sensor characteristics and on the spectrum of light incident on the sensor. The color correction variables can be adjusted through register settings.

Traditionally this would have been derived from two sets of CCM, one for Warm light like Tungsten and the other for Daylight (the part would interpolate between the two matrices). This is not an optimal solution for cameras used in a Cool White Fluorescent (CWF) environment. A better solution is to provide three CCMs, which would include a matrix for CWF (interpolation now between three matrices). The AS0140AT offers this feature which will give the user improved color fidelity when under CWF type lighting.

To increase image sharpness, a programmable 2D aperture correction (sharpening filter) is applied to color-corrected image data. The gain and threshold for 2D correction can be defined through register settings.

#### Gamma Correction

The gamma correction curve is implemented as a piecewise linear function with 33 knee points, taking 12-bit arguments and mapping them to 10-bit output. The abscissas of the knee points are fixed at 0, 8, 16, 24, 32, 40, 48, 56, 64, 80, 96, 112, 128, 160, 192, 224, 256, 320, 384, 448, 512, 640, 768, 896, 1024, 1280, 1536, 1792, 2048, 2560, 3072, 3584, and 4096. The 10-bit ordinates are programmable through variables.

#### Color Kill

To remove high- or low-light color artifacts, a color kill circuit is included. It affects only pixels whose luminance exceeds a certain preprogrammed threshold. The U and V values of those pixels are attenuated proportionally to the difference between their luminance and the threshold.

#### YUV Color Filter

As an optional processing step, noise suppression by one-dimensional low-pass filtering of Y and/or UV signals is possible. A 3- or 5-tap filter can be selected for each signal.

#### **Camera Control and Auto Functions**

#### Auto Exposure

The auto exposure algorithm optimizes scene exposure to minimize clipping and saturation in critical areas of the image. This is achieved by controlling exposure time and analog gains of the external sensor as well as digital gains applied to the image.

| W 0,0 | W 0,1 | W 0,2 | W 0,3 | W 0,4 |

|-------|-------|-------|-------|-------|

| W 1,0 | W 1,1 | W 1,2 | W 1,3 | W 1,4 |

| W 2,0 | W 2,1 | W 2,2 | W 2,3 | W 2,4 |

| W 3,0 | W 3,1 | W 3,2 | W 3,3 | W 3,4 |

| W 4,0 | W 4,1 | W 4,2 | W 4,3 | W 4,4 |

Auto exposure is implemented by a firmware algorithm that is running on the embedded microcontroller that analyzes image statistics collected by the exposure measurement engine, makes a decision, and programs the sensor and color pipeline to achieve the desired exposure. The measurement engine subdivides the image into 25 windows organized as a  $5 \times 5$  grid.

Figure 14. 5 × 5 Grid

#### AE Track Driver

Other algorithm features include the rejection of fast fluctuations in illumination (time averaging), control of speed of response, and control of the sensitivity to small changes. While the default settings are adequate in most situations, the user can program target brightness, measurement window, and other parameters described above.

The driver changes AE parameters (integration time, gains, and so on) to drive scene brightness to the programmable target.

To avoid unwanted reaction of AE on small fluctuations of scene brightness or momentary scene changes, the AE track driver uses a temporal filter for luma and a threshold around the AE luma target. The driver changes AE parameters only if the filtered luma is larger than the AE target step and pushes the luma beyond the threshold.

#### Auto White Balance

The AS0140AT has a built-in AWB algorithm designed to compensate for the effects of changing spectra of the scene illumination on the quality of the color rendition. The algorithm consists of two major parts: a measurement engine performing statistical analysis of the image and a driver performing the selection of the optimal color correction matrix and IFP digital gain. While default settings of these algorithms are adequate in most situations, the user can reprogram base color correction matrices, place limits on color channel gains, and control the speed of both matrix and gain adjustments. The AS0140AT ATAWB

displays the current AWB position in color temperature, the range of which will be defined when programming the CCM matrixes.

The region of interest can be controlled through the combination of an inclusion window and an exclusion window.

# Exposure and White Balance Control

The Sensor Manager firmware component is responsible for controlling the application of 'exposure' and 'white balance' within the system. This effectively means that all control of integration times and gains (whether for exposure or white balance) is delegated to the Sensor Manager. The Auto Exposure (AE) and Auto White Balance (AWB) algorithms use services provided by the Sensor Manager to apply exposure and/or white balance changes.

#### Dual Band IRCF

For some applications a day/night filter would be switched in/out, this option is an additional cost to the camera system. The AS0140AT supports the use of dual band IRCF, which removes the need for the switching day/night filter. Tuning support is provided for this usage case. Refer to the AS0140AT developer guide for details.

# Exposure and White Balance Modes

The AS0140AT supports auto and manual exposure and white balance modes. In addition, it will operate within synchronized multi-camera systems. In this use case, one camera within the system will be the 'master', and the others 'slaves'. The master is used to calculate the appropriate

exposure and white balance. This is then applied to all slaves concurrently under host control.

#### Auto Mode

In Auto Exposure mode the AE algorithm is responsible for calculating the appropriate exposure to keep the desired scene brightness, and for applying the exposure to the underlying hardware. In Auto White Balance mode the AWB algorithm is responsible for calculating the color temperature of the scene and applying the appropriate red and blue gains to compensate.

#### Triggered Auto Mode

The Triggered Auto Exposure and Triggered Auto White Balance modes are intended for the multi-camera use cases, where a host is controlling the exposure and white balance of a number of cameras. The idea is that one camera is in triggered-auto mode (the master), and the others in host-controlled mode (slaves). The master camera must calculate the exposure and gains, the host then copies this to the slaves, and all changes are then applied at the same time.

#### Manual Mode

Manual mode is intended to allow simple manual exposure and white balance control by the host. The host needs to set the CAM\_AET\_EXPOSURE\_TIME\_MS, CAM\_AET\_EXPOSURE\_GAIN and CAM\_AWB\_COLOR\_TEMPERATURE controls, the camera will calculate the appropriate integration times and gains.

#### **Host Controlled**

The Host Controlled mode is intended to give the host full control over exposure and gains.

#### Flicker Avoidance

Flicker occurs when the integration time is not an integer multiple of the period of the light intensity. The AS0140AT can be programmed to avoid flicker for 50 or 60 Hz. For integration times below the light intensity period (10 ms for 50 Hz environment), flicker cannot be avoided. The AS0140AT supports an indoor AE mode, that will ensure flicker-free operation.

#### Flicker Detection

The AS0140AT supports flicker detection, the algorithm is designed only to detect a 50 Hz or 60 Hz flicker source.

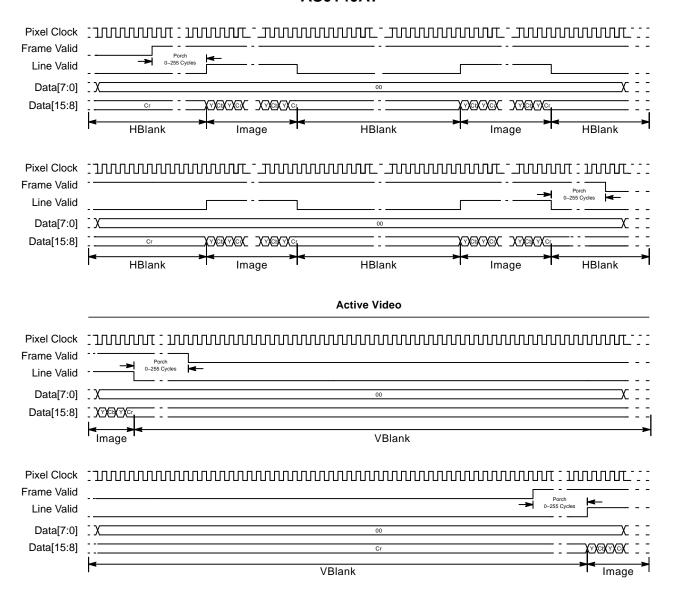

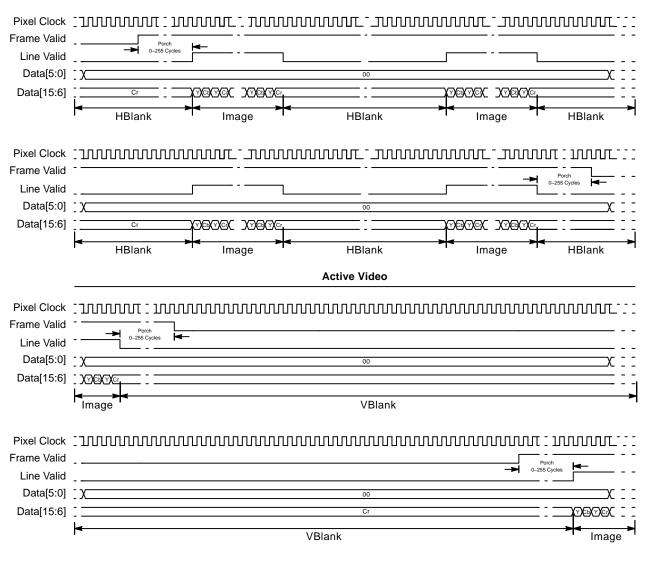

#### **Output Formatting**

The pixel output data in AS0140AT will be transmitted as an 8/10 bit word over one or two clocks.

#### Uncompressed YCbCr Data Ordering

The AS0140AT supports swapping YCbCr mode, as illustrated in Table 10.

Table 10. YCbCr OUTPUT DATA ORDERING

| Mode              | Data Sequence |     |                  |                  |  |  |

|-------------------|---------------|-----|------------------|------------------|--|--|

| Default (No Swap) | Cbi           | Yi  | Cri              | Y <sub>i+1</sub> |  |  |

| Swapped CrCb      | Cri           | Yi  | Cbi              | Y <sub>i+1</sub> |  |  |

| Swapped YC        | Yi            | Cbi | Y <sub>i+1</sub> | Cri              |  |  |

| Swapped CrCb, YC  | Yi            | Cri | Y <sub>i+1</sub> | Cbi              |  |  |

The data ordering for the YCbCr output modes for AS0140AT are shown in Table 11.

Table 11. YCbCr OUTPUT MODES (cam\_port\_parallel\_msb\_align=0x1)

| Mode            | Byte                | Pixel i                         | Pixel i+1                         | Notes                                            |

|-----------------|---------------------|---------------------------------|-----------------------------------|--------------------------------------------------|

| YCbCr_422_8_8   | Odd (DOUT[15:8])    | Cbi                             | Cri                               | Data Range of 0–255 (Y = 16–235 and C = 16–240)  |

|                 | Even (DOUT[15:8])   | Yi                              | Y <sub>i+1</sub>                  |                                                  |

| YCbCr_422_10_10 | Odd (DOUT[15:6])    | Cbi                             | Cri                               | Data Range of 0–1023 (Y = 64–940 and C = 64–960) |

|                 | Even (DOUT[15:6])   | Yi                              | Y <sub>i+1</sub>                  |                                                  |

| YCbCr_422_16    | Single (DOUT[15:0]) | Cb <sub>i</sub> _Y <sub>i</sub> | Cr <sub>i</sub> _Y <sub>i+1</sub> | Data Range of 0–255 (Y = 16–235 and C = 16–240)  |

Table 12. YCbCr OUTPUT MODES (cam\_port\_parallel\_msb\_align=0x0)

| Mode            | Byte                | Pixel i                         | Pixel i+1                         | Notes                                            |

|-----------------|---------------------|---------------------------------|-----------------------------------|--------------------------------------------------|

| YCbCr_422_8_8   | Odd (DOUT[7:0])     | Cbi                             | Cri                               | Data Range of 0–255 (Y = 16–235 and C = 16–240)  |

|                 | Even (DOUT[7:0])    | Y <sub>i</sub>                  | Y <sub>i+1</sub>                  |                                                  |

| YCbCr_422_10_10 | Odd (DOUT[9:0])     | Cbi                             | Cri                               | Data Range of 0–1023 (Y = 64–940 and C = 64–960) |

|                 | Even (DOUT[9:0])    | Y <sub>i</sub>                  | Y <sub>i+1</sub>                  |                                                  |

| YCbCr_422_16    | Single (DOUT[15:0]) | Cb <sub>i</sub> _Y <sub>i</sub> | Cr <sub>i</sub> _Y <sub>i+1</sub> | Data Range of 0–255 (Y = 16–235 and C = 16–240)  |

#### Notes:

- 1. Cb Y Cr Y by default.

- 2. cam\_port\_parallel\_msb\_align=0x1

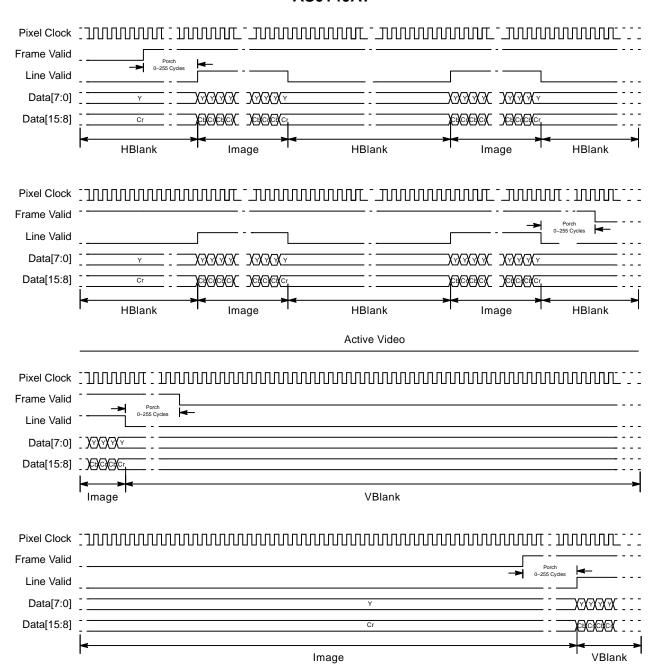

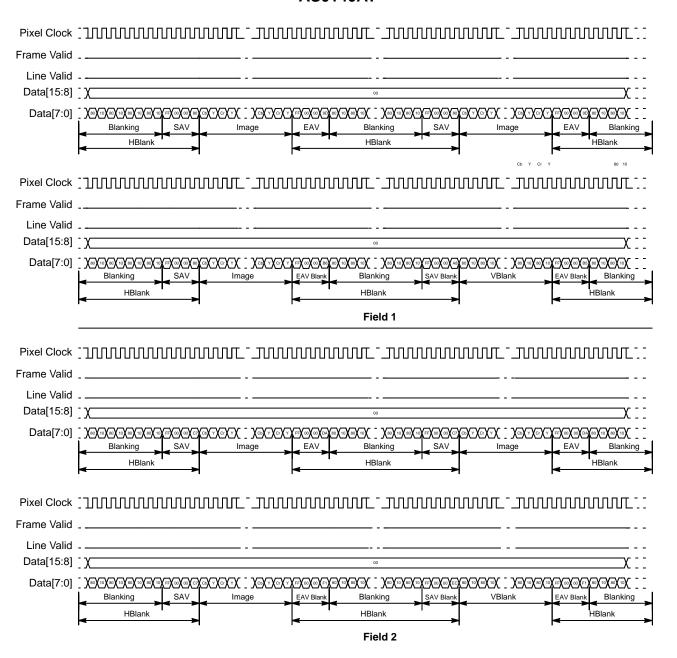

Figure 15. 8-bit YCrCr Output (YCbCr\_422\_8\_8)

# Notes:

- 1. Cb Y Cr Y by default.

- 2. cam\_port\_parallel\_msb\_align=0x1

Figure 16. 10-bit YCrCr Output (YCbCr\_422\_10\_10)

Figure 17. 16-bit YCrCr Output (YCbCr\_422\_16)

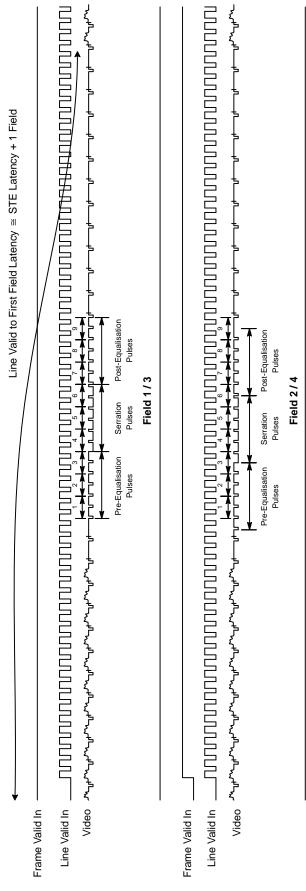

Progressive STE can output any of the YCbCr modes in Figure 15 to Figure 17.

Figure 18. Typical CCIR656 Output

Figure 19. Typical CVBS Output (NTSC/PAL)

#### Bayer Modes

Bayer output modes are only available in progressive output mode before STE. The data ordering for the ALTM Bayer output modes for AS0140AT are shown in Table 13.

**Table 13. ALTM BAYER OUTPUT MODES**

| Mode          | Byte   | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---------------|--------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| ALTM_Bayer_10 | Single | 0   | 0   | 0   | 0   | 0   | 0   | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| ALTM_Bayer_12 | Single | 0   | 0   | 0   | 0   | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

Table 13 and Table 14 show LSB aligned data; it is possible using register setting to obtain MSB aligned data.

The data ordering for the Bayer output modes for AS0140AT are shown in Table 14.

**Table 14. BAYER OUTPUT MODES**

| Mode     | Byte   | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Notes          |

|----------|--------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|----------------|

| Bayer_12 | Single | 0   | 0   | 0   | 0   | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | RAW Bayer Data |

#### Sensor Embedded Data

The AS0140AT is capable of passing sensor embedded data in Bayer output mode only.

The AS0140AT Statistics are available through the serial interface. Refer to the developer guide for details.

#### **Spatial Transform Engine (STE)**

A spatial transform is defined as a transform in which some pixels are in different positions within the input and output pictures. Examples include zoom, lens distortion correction, turn, rotate, roaming and projection. STE is a fully programmable engine which can perform spatial transforms and eliminates the need for an expensive DSP for image correction.

#### Lens Distortion Correction

Automotive backup cameras typically feature a wide FOV lens so that a single camera mounted above the center of the rear bumper can present the driver with a view of all potential obstacles immediately behind the full width of the vehicle. Lenses with a wide field of view typically exhibit at least a noticeable amount of barrel distortion.

Barrel distortion is caused by a reduction in object magnification the further away from the optical axis.

For the image to appear natural to the driver, the AS0140AT corrects this barrel distortion and reprocesses the image so that the resulting distortion is much smaller. This is called distortion correction. Distortion correction is the ability to digitally correct the lens barrel distortion and to provide a natural view of objects. In addition, with barrel distortion one can adjust the perspective view to enhance the visibility by virtually elevating the point of viewing objects.

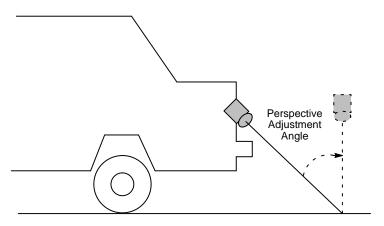

#### Perspective View

A backup camera has to be able to virtually adjust the vertical perspective as if the camera were placed immediately behind the vehicle pointed directly down, as illustrated in Figure 20. The vertical perspective adjustment may be employed temporarily to assist with parking conditions, or it may be enabled permanently by loading new parameters.

Figure 20. Vertical Perspective Adjustment

Pan, Tilt, Zoom and Rotate

Using the STE it is possible to implement image transforms like Pan, Tilt, Zoom, and Rotate.

Figure 21. Uncorrected Image

Figure 22. Zoomed

Figure 23. Zoom and Look Left

Figure 24. Zoom and Look Right

#### Multi-Panel

STE supports multi-panel views, these can be 2 or 3 panels. This feature is ideally suited for applications where viewing at a junction is required.

Figure 25. Multi-Panel

#### **Overlay Capability**

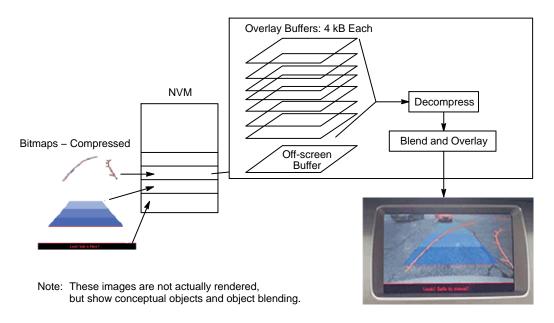

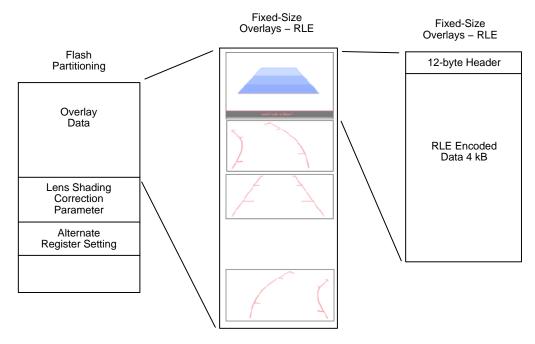

Figure 26 highlights the graphical overlay data flow of the AS0140AT. The images are separated to fit into 4 kB blocks of memory after compression.

- Up to seven overlays may be blended simultaneously

- Overlay size up to 720 × 576 pixels rendered

- Selectable readout: rotating order is user programmable

- Dynamic movement through predefined overlay images

- Palette of 32 colors out of 16 million with 16 colors per bitmap

- Each color has a YCbCr (8-8-8 bit) and 8 bits for the Alpha value (Transparency).

- Each layer has a built in fader which when enabled scales the Alpha value for each pixel.

- Blend factors may be changed dynamically to achieve smooth transitions

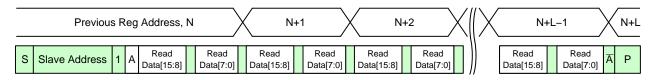

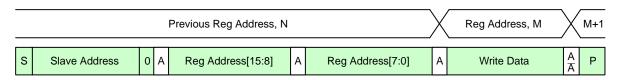

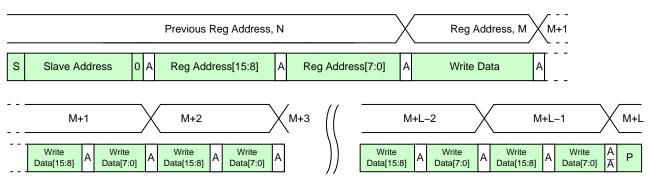

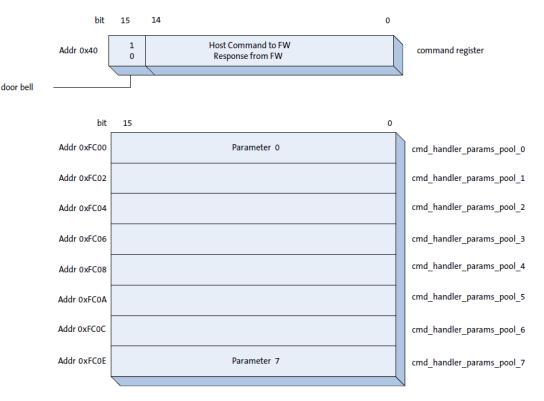

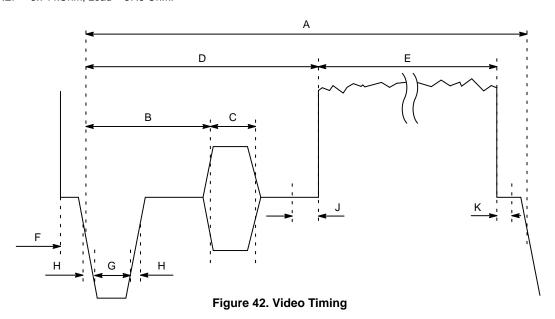

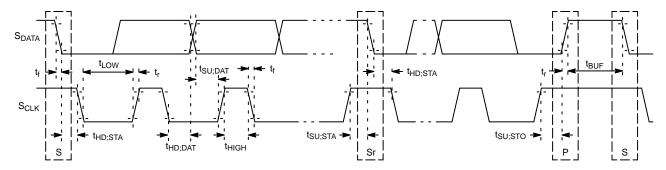

The overlay engine is controlled through host commands that allow a bitmap to be written piecemeal to memory buffer through the two-wire serial interface, and through a DMA channel direct from SPI Flash memory. Multiple encoding passes may be required to fit an image into a 4 kB block of memory; alternatively, the image can be divided into two or more blocks to make the image fit. Every graphic image may be positioned in an x/y direction and overlap with other graphic images.