# Universal (Step-Up/Step-Down) Charge Pump Regulated DC/DC Converter

#### Description

The FAN5602 is a universal switched capacitor DC/DC converter capable of step—up or step—down operation. Due to its unique adaptive fractional switching topology, the device achieves high efficiency over a wider input/ output voltage range than any of its predecessors. The FAN5602 utilizes resistance—modulated loop control, which produces lower switching noise than other topologies. Depending upon actual load conditions, the device automatically switches between constant—frequency and pulse—skipping modes of operation to extend battery life.

The FAN5602 produces a fixed regulated output within the range of 2.7 V to 5.5 V from any type of voltage source. High efficiency is achieved under various input/ output voltage conditions because an internal logic circuit automatically reconfigures the system to the best possi– ble topology. Only two 1  $\mu F$  bucket capacitors and one 10  $\mu F$  output capacitor are needed. During power on, soft–start circuitry prevents excessive current drawn from the supply. The device is protected against short–circuit and over–temperature conditions.

The FAN5602 is available with 4.5 V and 5.0 V output voltages in a 3x3 mm WDFN8 package.

#### **Features**

- Low-Noise, Constant-Frequency Operation at Heavy Load

- High-Efficiency, Pulse-Skip (PFM) Operation at Light Load

- Switch Configurations (1:3, 1:2, 2:3, 1:1, 3:2, 2:1, 3:1)

- 92% Peak Efficiency

- Input Voltage Range: 2.7 V to 5.5 V

- Output Current: 4.5 V, 100 mA at V<sub>IN</sub> = 3.6 V

- ±3% Output Voltage Accuracy

- I<sub>CC</sub> < 1 μA in Shutdown Mode

- 1 MHz Operating Frequency

- Shutdown Isolates Output from Input

- Soft-Start Limits Inrush Current at Startup

- Short-Circuit and Over-Temperature Protection

- Minimum External Component Count

- No Inductors

- This is a Pb-Free Device

#### **Applications**

- Cell Phones

- Handheld Computers

- Portable RF Communication Equipment

### ON Semiconductor®

www.onsemi.com

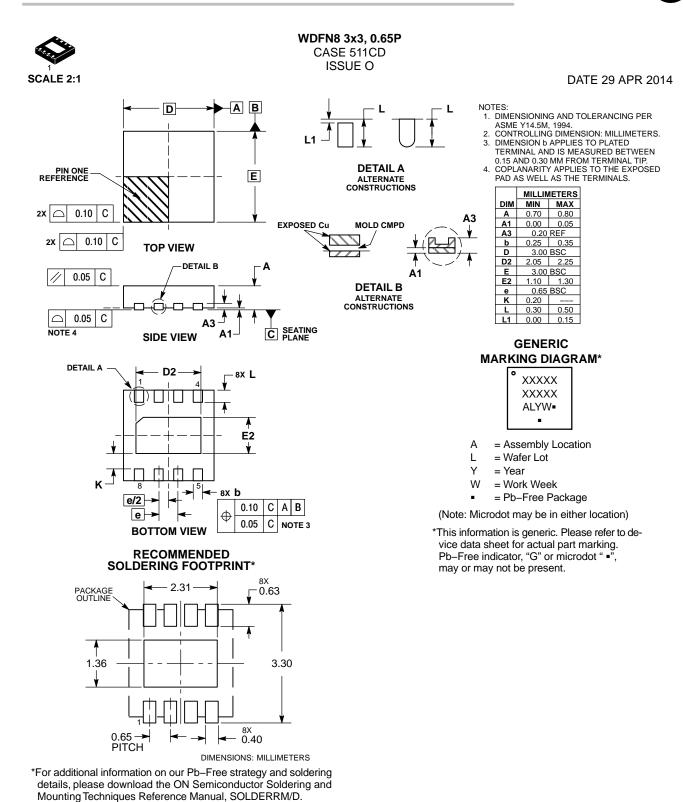

WDFN8 3x3, 0.65P CASE 511CD

#### MARKING DIAGRAM

602 = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

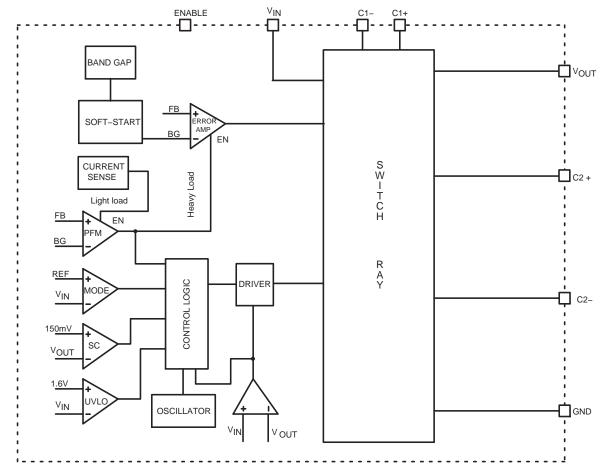

## PIN ASSIGNMENTS

3x3mm 8-Lead MLP

### ORDERING INFORMATION

See detailed ordering and shipping information on page 2 of this data sheet.

- Core Supply to Low–Power Processors

- Low-Voltage DC Bus

- DSP Supplies

#### **ORDERING INFORMATION**

| Part Number  | Output Voltage, N <sub>VOM</sub> | Package                    | Packing Method <sup>†</sup> |

|--------------|----------------------------------|----------------------------|-----------------------------|

| FAN5602MP45X | 4.5 V                            | WDFN8 3x3, 0.65P (Pb-Free) | 3000 / Tape & Reel          |

| FAN5602MP5X  | 5.0 V                            | WDFN8 3x3, 0.65P (Pb-Free) | 3000 / Tape & Reel          |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D

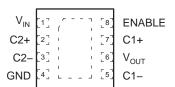

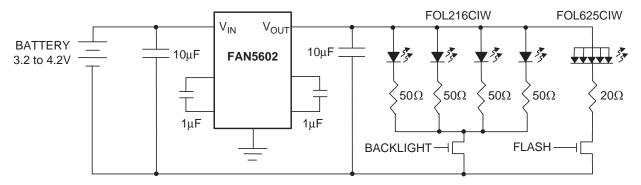

## **Application Diagram**

**Figure 1. Typical Application Diagram**

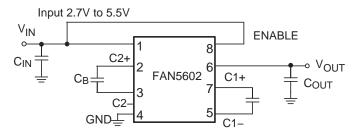

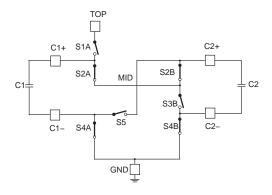

## **Block Diagram**

Figure 2. Block Diagram

## **Pin Assignments**

Figure 3. Pin Assignments

**Table 1. PIN DESCRIPTIONS**

| Pin # | Name   | Description                                                                                                                                           |  |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | VIN    | Supply Voltage Input.                                                                                                                                 |  |

| 2     | C2+    | Bucket Capacitor2. Positive Connection.                                                                                                               |  |

| 3     | C2-    | Bucket Capacitor2. Negative Connection.                                                                                                               |  |

| 4     | GND    | Ground                                                                                                                                                |  |

| 5     | C1-    | Bucket Capacitor1. Negative Connection.                                                                                                               |  |

| 6     | Vout   | Regulated Output Voltage. Bypass this pin with 10 μF ceramic low–ESR capacitor.                                                                       |  |

| 7     | C1+    | Bucket Capacitor1. Positive Connection.                                                                                                               |  |

| 8     | ENABLE | Enable Input. Logic high enables the chip and logic low disables the chip, reducing the supply current to less than 1 $\mu$ A. Do not float this pin. |  |

#### **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                                                                                  | Min | Max                   | Unit |

|------------------|------------------------------------------------------------------------------------------------------------|-----|-----------------------|------|

| VIN              | V <sub>IN,</sub> V <sub>OUT,</sub> ENABLE, Voltage to GND -3.0  Voltage at C1+,C1-,C2+, and C2-to GND -3.0 |     | 6.0                   | V    |

|                  |                                                                                                            |     | V <sub>IN</sub> + 0.3 | V    |

| $P_{D}$          | P <sub>D</sub> Power Dissipation                                                                           |     | Internally Limited    |      |

| T <sub>L</sub>   | Lead Soldering Temperature (10 seconds)                                                                    |     | 300                   | °C   |

| T <sub>J</sub>   | T <sub>J</sub> Junction Temperature                                                                        |     | 150                   | °C   |

| T <sub>STG</sub> | Storage Temperature                                                                                        | -55 | 150                   | °C   |

| ESD              | Human Body Model (HBM)                                                                                     |     | 2                     | kV   |

| 230              | Charged Device Model (CDM)                                                                                 |     | 2                     | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Using Mil Std. 883E, method 3015.7 (Human Body Model) and EIAJ/JESD22C101–A (Charged Device Model).

**Table 3. RECOMMENDED OPERATING CONDITIONS**

| Symbol         | Parameter           | Condition                          | Min | Тур | Max | Unit     |

|----------------|---------------------|------------------------------------|-----|-----|-----|----------|

| VIN            | Input Voltage       |                                    | 1.8 |     | 5.5 | <b>V</b> |

| IL             | Load Current        | V <sub>IN</sub> < 2 V              |     |     | 30  | mA       |

|                |                     | 4.5 & 5.5, V <sub>IN</sub> = 3.6 V |     |     | 100 |          |

| T <sub>A</sub> | Ambient Temperature |                                    | -40 |     | +85 | °C       |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

2. Refer to Figure 9 in Typical Performance Characteristics

## **Table 4. DC ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 2.7 V to 5.5 V,  $C_1$  =  $C_2$  = 1  $\mu$ F,  $C_{IN}$  =  $C_{OUT}$  = 10  $\mu$ F, ENABLE =  $V_{IN}$ ,  $T_A$  =  $-40^{\circ}$ C to +85 $^{\circ}$ C unless otherwise noted. Typical values are at  $T_A$  = 25 $^{\circ}$ C.

| Symbol             | Parameter                             | Condition                                                                      |                         | Min                     | Тур  | Max                     | Unit |

|--------------------|---------------------------------------|--------------------------------------------------------------------------------|-------------------------|-------------------------|------|-------------------------|------|

| V <sub>UVLO</sub>  | Input Under-Voltage Lockout           |                                                                                |                         | 1.5                     | 1.7  | 2.2                     | v    |

| V <sub>OUT</sub>   | Output Voltage                        | $V_{IN} \ge 0.75 \text{ x } V_{NOM}, 0 \text{ mA} < I_{L}$                     | <sub>OAD</sub> < 100 mA | 0.97 x V <sub>NOM</sub> | VNOM | 1.03 x V <sub>NOM</sub> | V    |

| IQ                 | Quiescent Current                     | V <sub>IN</sub> ≥ 1.1 x V <sub>NOM</sub> , I <sub>LOAD</sub> = 0 m             | nA                      |                         | 170  | 300                     | μΑ   |

|                    | Off Mode Supply Current               | ENABLE = GND                                                                   |                         |                         | 0.1  | 1.0                     | μΑ   |

|                    | Output Short-Circuit                  | V <sub>OUT</sub> < 150 mV                                                      |                         |                         |      | 200                     | mA   |

|                    | Efficiency                            | V <sub>IN</sub> = 0.85 x V <sub>NOM</sub> , I <sub>LOAD</sub> = 30 mA          | 4.5, 5.0 V              |                         | 80   |                         | %    |

|                    |                                       | V <sub>IN</sub> = 1.1 x V <sub>NOM</sub> , I <sub>LOAD</sub> = 30 mA           | 4.5, 5.0 V              |                         | 92   |                         |      |

| fosc               | Oscillator Frequency                  | T <sub>A</sub> = 25°C                                                          |                         | 0.7                     | 1.0  | 1.3                     | MHz  |

| T <sub>SD</sub>    | Thermal Shutdown Threshold            |                                                                                |                         |                         | 145  |                         | °C   |

| T <sub>SDHYS</sub> | Thermal Shutdown Threshold Hysteresis |                                                                                |                         |                         | 15   |                         | °C   |

| V <sub>IH</sub>    | ENABLE Logic Input High<br>Voltage    |                                                                                |                         | 1.5                     |      |                         | V    |

| V <sub>IL</sub>    | ENABLE Logic Input Low<br>Voltage     |                                                                                |                         |                         |      | 0.5                     | V    |

| I <sub>EN</sub>    | ENABLE Logic Input Bias<br>Current    | ENABLE =V <sub>IN</sub> or GND                                                 |                         | -1                      |      | 1                       | μΑ   |

| t <sub>ON</sub>    | V <sub>OUT</sub> Turn–On Time         | V <sub>IN</sub> = 0.9 x V <sub>NOM</sub> , I <sub>LOAD</sub> = 0 mA,10% to 90% |                         |                         | 0.5  |                         | ms   |

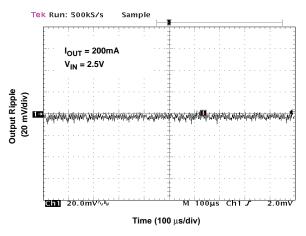

|                    | V <sub>OUT</sub> Ripple               | V <sub>IN</sub> = 2.5 V, I <sub>LOAD</sub> = 200 mA                            |                         |                         | 10   |                         | mVpp |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

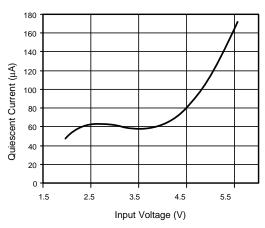

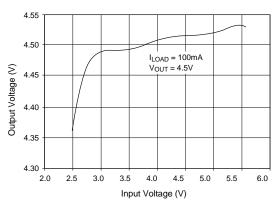

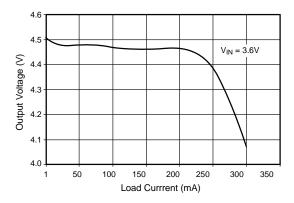

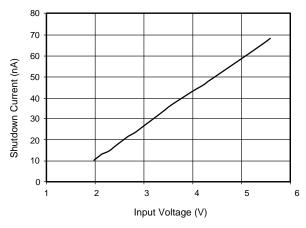

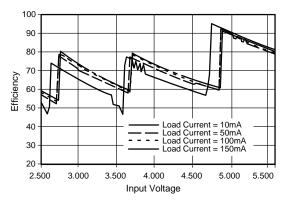

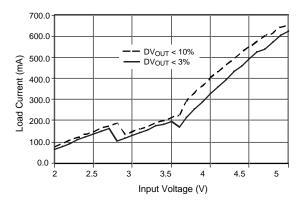

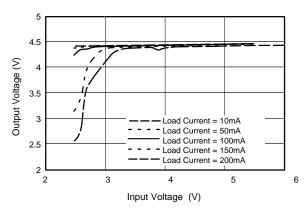

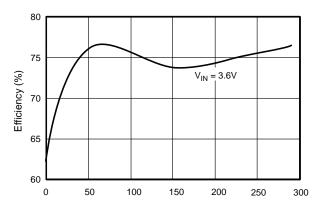

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C,  $V_{OUT} = 4.5$  V unless otherwise noted.

Figure 4. Quiescent Current vs. Input Voltage

Figure 6. Line Regulation

Figure 8. Load Regulation

Figure 5. Shutdown Current vs. Input Voltage

Figure 7. Efficiency vs. Input Voltage

Figure 9. Output Current Capacity vs. Input voltage

Figure 10. Output Voltage vs. Input Voltage

Figure 12. Peak Efficiency vs. Load Current

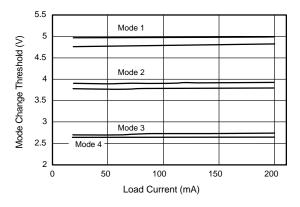

Figure 14. Mode Change Threshold and Hysteresis

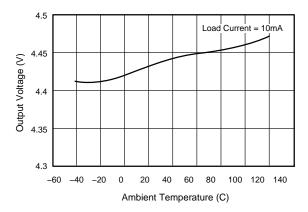

Figure 11. Output Voltage vs. Ambient Temperature

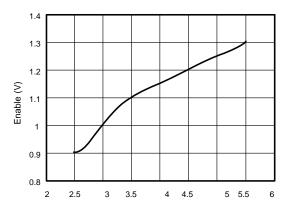

Figure 13. Enable Threshold vs. Input Voltage

## TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

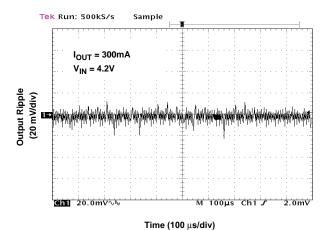

$T_A = 25$ °C,  $C_{IN} = C_{OUT} = 10 \mu F$ ,  $C_B = 1 \mu F$ ,  $V_{OUT} = 4.5 \text{ V}$  unless otherwise noted.

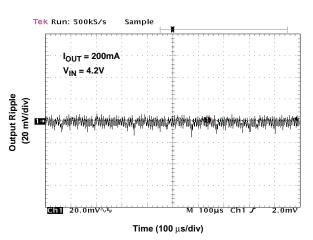

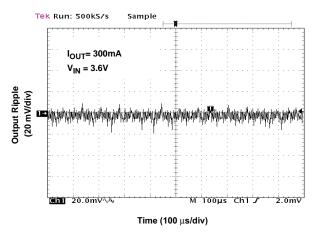

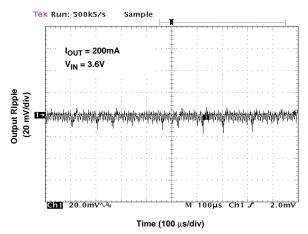

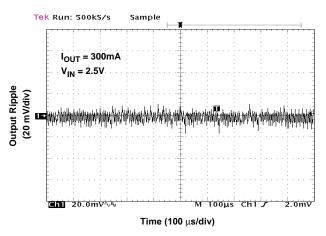

Figure 15. Output Ripple

Figure 17. Output Ripple

Figure 19. Output Ripple

Figure 16. Output Ripple

Figure 18. Output Ripple

Figure 20. Output Ripple

#### **FUNCTIONAL DESCRIPTION**

FAN5602 is a high-efficiency, low-noise switched capacitor DC/DC converter capable of step-up and step-down operations. It has seven built-in switch configurations. Based on the ratio of the input voltage to the output volt- age, the FAN5602 automatically reconfigures the switch to achieve the highest efficiency. The regulation of the output is achieved by a linear regulation loop, which modulates the on-resistance of the power transistors so that the amount of charge transferred from the input to the flying capacitor at each clock cycle is controlled and is equal to the charge needed by the load. The current spike is reduced to minimum. At light load, the FAN5602 automatically switches to Pulse Frequency Modulation (PFM) mode to save power. The regulation at PFM mode is achieved by skipping pulses.

#### **Linear Regulation Loop**

The FAN5602 operates at constant frequency at load higher than 10 mA. The linear regulation loop consisting of power transistors, feedback (resistor divider), and error amplifier is used to realize the regulation of the out—put voltage and to reduce the current spike. The error amplifier takes feedback and reference as inputs and generates the error voltage signal. The error voltage signal is then used as the gate voltage of the power transistor and modulates the on—resistance of the power transistor and, therefore, the charge transferred from the input to the output is controlled and the regulation of the output is realized. Since the charge transfer is controlled, the FAN5602 has a small ESR spike.

#### **Switch Array**

### **Switch Configurations**

The FAN5602 has seven built—in switch configurations, including 1:1, 3:2, 2:1 and 3:1 for step—down and 2:3, 1:2 and 1:3 for step—up.

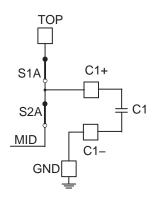

When 1.5 x  $V_{\text{OUT}} > V_{\text{IN}} > V_{\text{OUT}}$ , the 1:1 mode shown in Figure 21 is used. In this mode, the internal oscillator is

turned off. The power transistors connecting the input and the output become pass transistors and their gate voltages are controlled by the linear regulation loop, the rest of power transistors are turned off. In this mode, the FAN5602 operates exactly like a low dropout (LDO) regulator and the ripple of the output is in the micro–volt range.

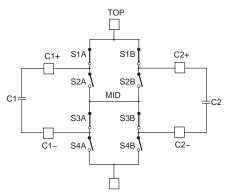

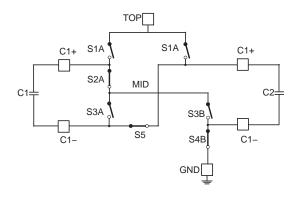

When 1.5 x  $V_{\rm IN}$  >  $V_{\rm OUT}$  >  $V_{\rm IN}$ , the 2:3 mode (step–up) shown in Figure 22 is used. In the charging phase, two flying capacitors are placed in series and each capacitor is charged

to a half of the input voltage. In pumping phase, the flying capacitors are placed in parallel. The input is connected to the bottom the capacitors so that the top of the capacitors is boosted to a voltage that equals  $V_{\rm IN}/2 + V_{\rm IN}$ , i.e.,  $3/2 \times V_{\rm IN}$ . By connecting the top of the capacitors to the output, one can ideally charge the output to  $3/2 \times V_{\rm IN}$ . If  $3/2 \times V_{\rm IN}$  is higher than the needed  $V_{\rm OUT}$ , the linear regulation loop adjusts the on– resistance to drop some voltage. Boosting the voltage of the top of the capacitors to  $3/2 \times V_{\rm IN}$  by connecting  $V_{\rm IN}$  the bottom of the capacitors, boosts the power efficiency  $3/2 \times V_{\rm IN}$ . For example, if  $V_{\rm IN}=2 \times V_{\rm IN}=2 \times V_{\rm IN}=4 \times V_{\rm IN}$ , the ideal power efficiency is 100%.

When 2 x  $V_{\rm IN}$  >  $V_{\rm OUT}$  > 1.5 x  $V_{\rm IN}$ , the 1:2 mode (step-up) shown in Figure 23 is used. Both in the charging phase and in pumping phase, two flying capacitors are placed in parallel. In charging phase, the capacitors are charged to the input voltage. In the pumping phase, the input volt— age is placed to the bottom of the capacitors. The top of the capacitors is boosted to 2 x  $V_{\rm IN}$ . By connecting the top of the capacitors to the output, one can ideally charge the output to 2 x  $V_{\rm IN}$ . Boosting the voltage on the top of the capacitors to  $2V_{\rm IN}$  boosts the power efficiency 2 times. In 1:2 mode, the ideal power efficiency is  $V_{\rm OUT}$  2 x  $V_{\rm IN}$ . For example,  $V_{\rm IN}$  = 2V,  $V_{\rm OUT}$  = 2 x  $V_{\rm IN}$  = 4V, the ideal power efficiency is 100%.

When 3 x  $V_{IN}$  >  $V_{OUT}$  > 2 x  $V_{IN}$ , the 1:3 mode (step-up) shown in Figure 24 is used. In charging phase, two flying capacitors are placed in parallel and each is charged to  $V_{IN}$ . In the pumping phase, the two flying capacitors are placed in series and the input is connected to the bottom of the series connected capacitors. The top of the series connected capacitors is boosted to 3 x  $V_{IN}$ . The ideal power efficiency is boosted 3 times and is equal to  $V_{OUT}$ /  $3V_{IN}$  For example,  $V_{IN}$  = 1 V,  $V_{OUT}$  = 3 x  $V_{IN}$  = 3 V, the ideal power efficiency is 100%. By connecting the output to the top of the series connected capacitors, one can charge the output to 3 x  $V_{IN}$ .

The internal logic in the FAN5602 monitors the input and the output compares them, and automatically selects the switch configuration to achieve the highest efficiency.

The step-down modes 3:2, 2:1, and 3:1 can be understood by reversing the function of  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  in the above discussion.

The built–in modes improve power efficiency and extend the battery life. For example, if  $V_{\text{OUT}} = 5$  V, mode 1:2 needs a minimum  $V_{\text{IN}} = 2.5$  V. By built–in 1:3 mode, the minimum battery voltage is extended to 1.7 V.

#### **Switch Array Modes**

Figure 21. Mode 1 (1:1)

Figure 23. Mode 3 (1:2 or 2:1) All Switches Set for Phase 1 and Reverse State for Phase 2

#### **Light-Load Operation**

The power transistors used in the charge pump are very large in size. The dynamic loss from the switching the power transistors is not small and increases its propor-tion of the total power consumption as the load gets light. To save power, the FAN5602 switches, when the load is less than 10mA, from constant frequency to pulse-skip- ping mode (PFM) for modes 2:3(3:2), 1:2(2:1) and 1:3(3:1), except mode 1:1. In PFM mode, the linear loop is disabled and the error amplifier is turned off. A PFM comparator is used to setup an upper threshold and a lower threshold for the output. When the output is lower than the lower threshold, the oscillator is turned on and the charge pump starts working and keeps delivering charges from the input to the output until the output is higher than the upper threshold. The oscillator shuts off power transistors and delivers the charge to the output from the output capacitor. PFM operation is not used for Mode 1:1, even if at light load. Mode 1:1 is designed as an LDO with the oscillator off. The power transistors at LDO mode are not switching and therefore do not have the dynamic loss.

Switching from linear operation to PFM mode ( $I_{LOAD}$ < 10 mA) and from PFM to linear mode ( $I_{LOAD}$ > 10 mA) is automatic, based on the load current, which is monitored all the time.

Figure 22. Mode 2 (2:3 or 3:2) All Switches Set for Phase 1 and Reverse State for Phase 2

Figure 24. Mode 4 (1:3 or 3:1) All Switches Set for Phase 1 and Reverse State for Phase 2

#### **Short Circuit**

When the output voltage is lower than 150mV, the FAN5602 enters short–circuit condition. In this condition, all power transistors are turned off. A small transistor shorting the input and the output turns on and charges the output. This transistor stays on as long as the  $V_{\text{OUT}} < 150 \text{ mV}$ . Since this transistor is very small, the current from the input to the output is limited. Once the short at the output is eliminated, this transistor is large enough to charge the output higher than 150mV and the FAN5602 enters soft–start period.

#### **Soft Start**

The FAN5602 uses a constant current, charging a low-pass filter to generate a ramp. The ramp is used as reference voltage during the startup. Since the ramp starts at zero and goes up slowly, the output follows the ramp and inrush current is restricted. When the ramp is higher than bandgap voltage, the bandgap voltage supersedes ramp as reference and the soft start is over. The soft start takes about 500 µs.

## **Thermal Shutdown**

The FAN5602 goes to thermal shutdown if the junction temperature is over 150°C with 15°C hysteresis.

#### APPLICATION INFORMATION

## Using the FAN5602 to Drive LCD Backlighting

The FAN5602 4.5V option is ideal for driving the back-lighting and flash LEDs for portable devices. One FAN5602 device can supply the roughly 150mA needed to power both the backlight and the flash LEDs. Even though drawing this much current from the FAN5602 drives the part out of the

3% output regulation, it is not a problem. The backlight and flash LEDs still produce opti—mal brightness at the reduced regulation. When building this circuit, use ceramic capacitors with low ESR. All capacitors should be placed as close as possible to the FAN5602 in the PCB layout.

Figure 25. Circuit for Backlighting / Flash Application

| DOCUMENT NUMBER: | 98AON84944F               | Electronic versions are uncontrolle                                  |             |  |  |

|------------------|---------------------------|----------------------------------------------------------------------|-------------|--|--|

| STATUS:          | ON SEMICONDUCTOR STANDARD | accessed directly from the Document versions are uncontrolled except | ' '         |  |  |

| NEW STANDARD:    |                           | "CONTROLLED COPY" in red.                                            |             |  |  |

| DESCRIPTION:     | WDFN8, 3X3, 0.65P         |                                                                      | PAGE 1 OF 2 |  |  |

| <b>DOCUMENT</b> | NUMBER: |

|-----------------|---------|

| 98AON84944      | \$F     |

PAGE 2 OF 2

| ISSUE | REVISION                                 | DATE        |

|-------|------------------------------------------|-------------|

| 0     | RELEASED FOR PRODUCTION. REQ. BY J. LIU. | 29 APR 2014 |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

|       |                                          |             |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify a

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative