# LC706210CA

## Product Preview

# Digital MEMS Microphone Controller including Pre-amplifier and Sigma Delta Modulator and Charge Pump

### **ON Semiconductor®**

www.onsemi.com

### Description

The LC706210CA is a MOS LSI which integrates digital MEMS microphone controller function. It supplies bias voltage to external MEMS sensor and accepts analog sound signal, outputs PDM (Pulse Density Modulation) data stream.

The LC706210CA includes LDO, pre-amplifier, ADC (Analog-to Digital Converter) and charge-pump. The charge-pump generates bias voltage which is needed by the MEMS sensor. The pre-amplifier amplifies analog sound signal from the MEMS sensor and drives ADC to obtain PDM data stream.

The LC706210CA features Gain Adjustment pad which enables sensitivity error reduction by the gain adjustment according to the deviation of MEMS sensor sensitivity. It also make the common MEMS sensor used in bottom–port structure available with top–port by the gain adjustment.

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

### **ORDERING INFORMATION**

| Device     | Package         | Shipping (Qty / Packing) |

|------------|-----------------|--------------------------|

| LC706210CA | Wafer (Pb-Free) | 1 / Wafer Carrier        |

### Features

- Optimized to be combined with a MEMS Sensor with 13.5 V Bias and -37.5 dBV @ 94 dBSPL Sensitivity

- Pulse Density Modulation (PDM) Output

- Standard 5-Wire Digital Interface

- 13.5 V Charge-pump Output for MEMS Sensor Bias

- +11.5 dB Initial Gain (Transfer Function)

- Dedicated Gain Adjustment Pad which enables -1.5 dB or +3 dB Adjustment from the Initial Gain according to Wire Connection

- Low Noise –91 dBFS Output makes total SNR up to 64 dB

- Low Power Operation Mode

- This is a Pb-Free Device

### Applications

- Digital MEMS Microphone

- Personal Computer

- Tablet Computer

- Mobile Handset

- Headset Accessories

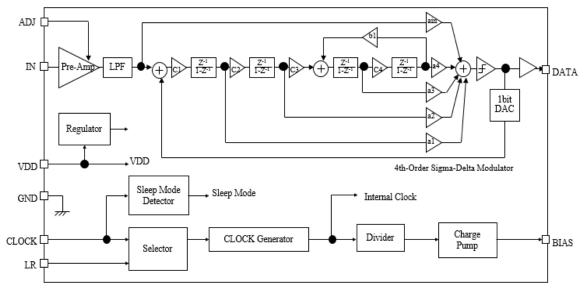

### **Block Diagram**

Figure 1. Block Diagram

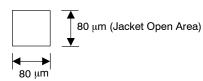

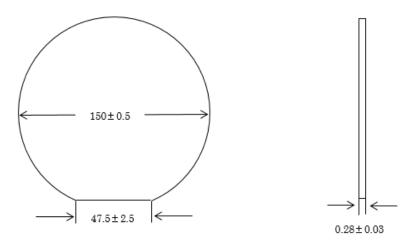

Figure 3. Pad Size

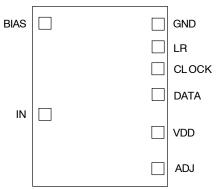

### Figure 2. Pad Coordinate

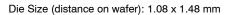

### Wafer Outline

Figure 4. Wafer Outline

### LC706210CA

### Table 1. ABSOLUTE MAXIMUM RATINGS at $T_a = 25^{\circ}C$ , GND = 0 V

| Parameter                    | Symbol               | Pin Name       | Min  | Мах                   | Unit |

|------------------------------|----------------------|----------------|------|-----------------------|------|

| Maximum power supply voltage | V <sub>DD</sub> max  | VDD            | -0.3 | +4.0                  | V    |

| Maximum input voltage        | V <sub>CLK</sub> max | CLOCK, LR, ADJ | -0.3 | V <sub>DD</sub> + 0.3 | V    |

|                              | V <sub>IN</sub> max  | IN             | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| Maximum output voltage       | V <sub>O</sub> max   | DATA           | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| Operating temperature range  | Та                   |                | -40  | 85                    | °C   |

| Storage temperature range    | Tstg                 |                | -40  | 85                    | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### Table 2. CIRCUIT PARAMETERS (Note 1)

| Parameter                | Symbol          | Pin Name | Test Condition | Min | Тур | Max | Unit |

|--------------------------|-----------------|----------|----------------|-----|-----|-----|------|

| Input capacitance of die | C <sub>IN</sub> | IN       |                |     | 0.4 |     | pF   |

1. IN-Pin has a limited protection against ESD. Value of IN-Pin is proven by design.

### Table 3. DC ELECTRICAL CHARACTERISTICS RATING at $T_a$ = 25°C, $V_{DD}$ = 1.8 V, GND = 0 V, Fduty = 50%

| Parameter                             | Symbol          | Pin Name                   | Condition                                 | Min                 | Тур  | Max                 | Unit |

|---------------------------------------|-----------------|----------------------------|-------------------------------------------|---------------------|------|---------------------|------|

| Power supply voltage                  | V <sub>DD</sub> | VDD                        |                                           | 1.64                | 1.8  | 3.6                 | V    |

| Power consumption<br>(Normal mode)    | IDD(n)          | VDD                        | V <sub>DD</sub> = 1.8 V<br>Fclk = 2.4 MHz |                     | 860  |                     | μΑ   |

| Power consumption<br>(Low power mode) | IDD(I)          | VDD                        | V <sub>DD</sub> = 1.8 V<br>Fclk = 768 kHz |                     | 450  |                     | μΑ   |

| Standby Current                       | ISTBY           | VDD                        | V <sub>DD</sub> = 3.3 V                   |                     |      | 50                  | μΑ   |

| Input/Output LOW level                | Viol            | CLOCK,<br>DATA, LR,<br>ADJ | DATA :<br>lol = 0.5 mA                    |                     |      | $0.35 	imes V_{DD}$ | V    |

| Input/Output HIGH level               | Vioh            | CLOCK,<br>DATA, LR,<br>ADJ | DATA :<br>loh = –0.5 mA                   | $0.65 	imes V_{DD}$ |      |                     | V    |

| Charge pump voltage                   | Vbias           | BIAS                       | V <sub>DD</sub> = 1.8 V                   |                     | 13.5 |                     | V    |

| Charge Pump voltage tolerance         | Tolerance       | BIAS                       |                                           | -8                  |      | +8                  | %    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

### Table 4. AC ELECTRICAL CHARACTERISTICS DESIGN

at T<sub>a</sub> = 25°C, V<sub>DD</sub> = 1.8 V, GND = 0 V, Signal Frequency = 1 kHz, Measurement frequency = 100 Hz to 20 kHz, Fduty = 50%, Input capacitor = 1.5 pF, Bypass capacitor = 0.1  $\mu$ F (V<sub>DD</sub> – GND)

| Parameter                                           | Symbol              | Pin Name | Condition                                                            | Min | Тур   | Мах | Unit         |

|-----------------------------------------------------|---------------------|----------|----------------------------------------------------------------------|-----|-------|-----|--------------|

| Clock Frequency (Note 2)<br>(Normal Operation)      | Fclk                | CLOCK    |                                                                      | 1   | 2.4   | 4.8 | MHz          |

| Clock Frequency (Note 2)<br>(Low power Operation)   | Fclk                | CLOCK    |                                                                      | 351 | 768   | 800 | kHz          |

| Clock Frequency<br>(Sleep Mode)                     | Fclk_SL             | CLOCK    |                                                                      |     |       | 1   | kHz          |

| Clock Duty (Note 2)                                 | Fduty               | CLOCK    |                                                                      | 40  |       | 60  | %            |

| Over Sampling Ratio                                 | OSR                 |          |                                                                      |     | 50    |     |              |

| Maximum Input Voltage<br>(Input Full Scale Voltage) | Vin                 | IN       | 0 dBFS<br>(= 120 dBSPL)                                              |     | 266   |     | mVrms        |

| THD / THD+N                                         | THD+N_0<br>(Note 2) | DATA     | Vout = 0 dBFS<br>(= 120 dBSPL)<br>(= 167.8 mVrms)<br>1 kHz Sin-Wave  |     |       | 10  | %<br>(THD)   |

|                                                     | THD+N5              | DATA     | Vout = -5 dBFS<br>(= 115 dBSPL)<br>(= 94.4 mVrms)<br>1 kHz Sin-Wave  |     |       | 1   | %<br>(THD+N) |

|                                                     | THD+N20<br>(Note 2) | DATA     | Vout = -20 dBFS<br>(= 100 dBSPL)<br>(= 16.8 mVrms)<br>1 kHz Sin-Wave |     |       | 1   | %<br>(THD+N) |

| Digital Noise Floor(n)                              | DNF_n               | DATA     | Bandwidth 20 kHz<br>A-weighted,<br>Fclk = 2.4 MHz                    |     | -91.0 |     | dBFS         |

| Digital Noise Floor(I)                              | DNF_I               | DATA     | Bandwidth 8 kHz<br>A-weighted,<br>Fclk = 768 kHz                     |     | -90.0 |     | dBFS         |

| Transfer function 1 (Note 3)                        | TF1                 | DATA     | ADJ = open                                                           |     | 11.5  |     | dB           |

| Transfer function 2 (Note 3)                        | TF2                 | DATA     | ADJ = GND                                                            |     | 10.0  |     | dB           |

| Transfer function 3 (Note 3)                        | TF3                 | DATA     | ADJ = V <sub>DD</sub>                                                |     | 14.5  |     | dB           |

| Wake Up Time (Note 2)                               | WUT                 | CLOCK    | Fclk = 2.4 MHz                                                       |     |       | 10  | ms           |

| Fall Asleep Time (Note 2)                           | FAT                 |          | Fclk = 1 kHz                                                         |     |       | 10  | ms           |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

2. Reference data : No measurement.

3. Each product has been designed with performance of ±0.5 dB tolerance for transfer function however it's not measured in outgoing inspection.

### Table 5. PIN DESCRIPTIONS

| No. | Pin Name | Function                                                                                                                                                                                     | I/O    | Pin Conditions |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| _   | GND      | Ground                                                                                                                                                                                       | _      | -              |

| -   | VDD      | Power Supply                                                                                                                                                                                 | _      | -              |

| -   | DATA     | PDM Data Output                                                                                                                                                                              | Output |                |

| _   | LR       | LR signal input<br>Case 1 : When LR is LOW, PDM data is<br>valid in sync with negative edge of CLOCK.<br>Case 2 : When LR is HIGH, PDM data is<br>valid in sync with positive edge of CLOCK. | Input  |                |

| -   | CLOCK    | Clock input                                                                                                                                                                                  | Input  |                |

| -   | BIAS     | Charge Pump Voltage Output                                                                                                                                                                   | Output | -              |

| _   | IN       | Audio signal input                                                                                                                                                                           | Input  |                |

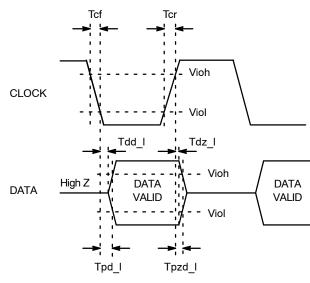

### Table 6. SWITCHING CHARACTERISTICS (Reference data: No measurement)

at T<sub>a</sub> = 25°C, V<sub>DD</sub> = 1.8 V, GND = 0 V, Fclk = 2.4 MHz, Fduty = 50% Case 1: LR = LOW

| Parameter                | Symbol | Pin Name | Condition             | Min | Тур | Max | Unit |

|--------------------------|--------|----------|-----------------------|-----|-----|-----|------|

| Clock Rise Time          | Tcr    | CLOCK    |                       |     |     | 10  | ns   |

| Clock Fall Time          | Tcf    | CLOCK    |                       |     |     | 10  | ns   |

| Output Data Delay        | Tpd_l  | DATA     | CL = 13 pF, RL = 1 MΩ | 18  |     | 60  | ns   |

| Output Hi–Z Delay        | Tpzd_l | DATA     | CL = 13 pF, RL = 1 MΩ | 0   |     | 16  | ns   |

| Delay for Data Assertion | Tdd_l  | DATA     |                       | 18  |     | 36  | ns   |

| Delay for Hi–Z           | Tdz_I  | DATA     |                       | 0   |     | 4   | ns   |

Figure 5.

### LC706210CA

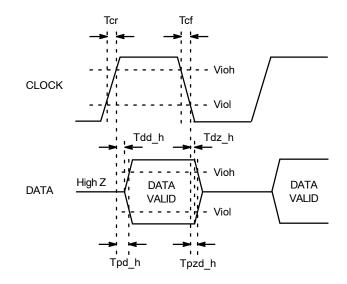

Table 7. SWITCHING CHARACTERISTICS (Reference data: No measurement) at  $T_a = 25$  °C,  $V_{DD} = 1.8$  V, GND = 0 V, Fclk = 2.4 MHz, Fduty = 50% Case 2: LR = HIGH

| Parameter                | Symbol | Pin Name | Condition                         | Min | Тур | Max | Unit |

|--------------------------|--------|----------|-----------------------------------|-----|-----|-----|------|

| Clock Rise Time          | Tcr    | CLOCK    |                                   |     |     | 10  | ns   |

| Clock Fall Time          | Tcf    | CLOCK    |                                   |     |     | 10  | ns   |

| Output Data Delay        | Tpd_h  | DATA     | $CL$ = 13 pF, $RL$ = 1 M $\Omega$ | 18  |     | 60  | ns   |

| Output Hi–Z Delay        | Tpzd_h | DATA     | $CL$ = 13 pF, RL = 1 M $\Omega$   | 0   |     | 16  | ns   |

| Delay for Data Assertion | Tdd_h  | DATA     |                                   | 18  |     | 36  | ns   |

| Delay for Hi-Z           | Tdz_h  | DATA     |                                   | 0   |     | 4   | ns   |

NOTE: Electrical information may be based on testing done on packaged devices. The packaging or device mounting may affect the electrical performance of the device; customers are responsible for verifying device performance and reliability after assembly, and the customer is responsible for the yield of the assembly process.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheets and/or application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights or others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application. Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and dis

Phone: 421 33 790 2910

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative