# Product Preview mWSaver<sup>®</sup> Integrated Power Switcher with 800 V SJ MOSFET for Offline SMPS

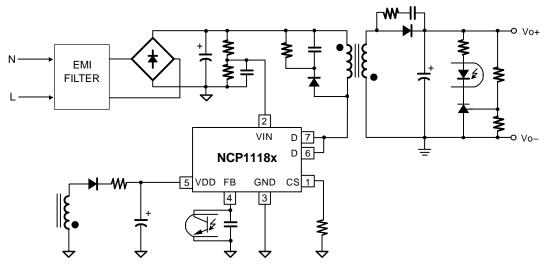

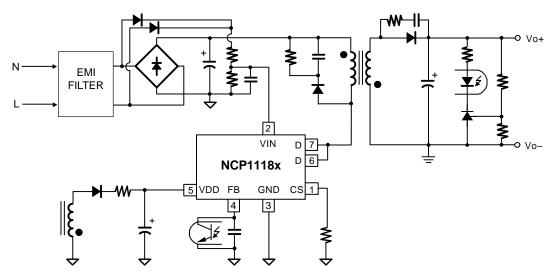

NCP1118x integrates a current-mode PWM controller employing mWSaver technology with a highly robust 800 V MOSFET providing enhanced performance of flyback converters.

The mWSaver technology reduces switching frequency at light–load condition and avoid acoustic–noise problems and even enables the power supply to meet international power conservation requirements, such as Energy Star<sup>®</sup>. The standby power consumption can be under 25 mW for most power supply designs. Additionally, the NCP1118x integrates an internal high–voltage startup circuitry, frequency–hopping function and slope compensation.

Protections feature a feedback pin open-loop protection, line under-voltage protection (brownout protection) and overvoltage protection using an input-voltage sensing pin (VIN) operated with auto-recovery operation.

## Features

- Integrated 800 V Super Junction MOSFET

- Build-in Start-up, Soft-Start, and Slope Compensation

- mWSaver Technology Provides Industry's Best-in-Class Standby Power

- Proprietary Asynchronous Frequency Hopping Technique to Reduce EMI

- Fixed PWM Frequency: 65/100/130 kHz

- Programmable Constant Power Limit for Entire Input–Voltage Range

- Brown–In/Out Protection with Hysteresis and Line Over–Voltage Protection to Detect Input Voltage through VIN Pin

- VDD Under-Voltage Lockout (UVLO)

- Current–Sense Short Protection (CSSP) and Abnormal Over–Current Protection (AOCP)

- Internal Thermal Shutdown (TSD) with Hysteresis

- Auto-Restart for All Protections include Feedback Open-Loop Protection (OLP), VDD Over-Voltage Protection (OVP)

## **Typical Applications**

- Isolated Auxiliary Power Supplies

- White Good Applications

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

# **ON Semiconductor®**

www.onsemi.com

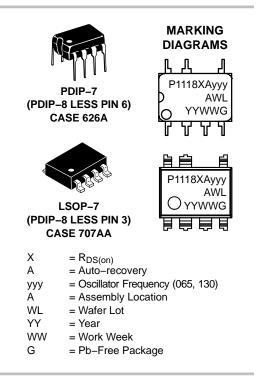

## ORDERING INFORMATION

See detailed ordering and shipping information on page 11 of this data sheet.

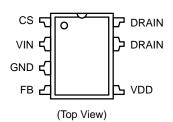

## Table 1. PIN FUNCTION DESCRIPTION

| PIN #<br>DIP 7, LSOP-7 | Name  | Description                                                                                                                                                                                                                                                                                                                                          |

|------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                      | CS    | Current sense. The sensed voltage is used for peak-current-mode control and cycle-by-cycle current limiting.                                                                                                                                                                                                                                         |

| 2                      | VIN   | Line–voltage detection. The line–voltage detection is used for brownout protection with hysteresis. Constant output power limit over universal AC input range is also achieved using this VIN pin. It is suggested to add a low–pass filter to filter out line ripple on the bulk capacitor. Pulling VIN HIGH also triggers auto–restart protection. |

| 3                      | GND   | Ground                                                                                                                                                                                                                                                                                                                                               |

| 4                      | FB    | The signal from the external compensation circuit is fed into this pin. The PWM duty cycle is deter-<br>mined in response to the signal on this pin and the currentsense signal on the SENSE pin.                                                                                                                                                    |

| 5                      | VDD   | Power supply. The internal protection circuit disables PWM output as long as $V_{\text{DD}}$ exceeds the OVP trigger point.                                                                                                                                                                                                                          |

| 6, 7                   | DRAIN | This pin is connected to internal high voltage startup circuit and the drain pin of an integrated MOSFET. Typically, this pin is directly connected to one of terminals of the transformer. At initial startup or restart mode, operating voltage is powered through this pin.                                                                       |

## Table 2. PRODUCTS INFORMATION & INDICATIVE MAXIMUM OUTPUT POWER

|                 |        |           |                           | Output Power Table (W)   |                          |                     |  |

|-----------------|--------|-----------|---------------------------|--------------------------|--------------------------|---------------------|--|

|                 |        | Switching |                           | Adapter                  | Open                     | Frame               |  |

| Part Number     | PKG    | Frequency | Max. $R_{DS(on)}(\Omega)$ | 85 ~ 265 V <sub>AC</sub> | 85 ~ 265 V <sub>AC</sub> | 230 V <sub>AC</sub> |  |

| NCP11184A065PG  |        |           | 2.25                      | 18                       | 25                       | 37                  |  |

| NCP11185A065PG  |        | 65 kHz    | 1.3                       | 22                       | 30                       | 45                  |  |

| NCP11186A065PG  | PDIP7  | 00 KHZ    | 0.85                      | 26                       | 35                       | 52                  |  |

| NCP11187A065PG  |        |           | 0.65                      | 30                       | 40                       | 60                  |  |

| NCP11184A100PG  |        | 100 kHz   | 2.25                      | 18                       | 25                       | 37                  |  |

| NCP11187A100PG  |        |           | 0.65                      | 30                       | 40                       | 60                  |  |

| NCP11184A130PG  |        | 120 141-  | 2.25                      | 18                       | 25                       | 37                  |  |

| NCP11185A130PG  |        | 130 kHz   | 1.3                       | 22                       | 30                       | 45                  |  |

| NCP11184A065LPG |        |           | 2.25                      | 18                       | 25                       | 37                  |  |

| NCP11185A065LPG |        | 65 kHz    | 1.3                       | 22                       | 30                       | 45                  |  |

| NCP11187A065LPG | LSOP-7 |           | 0.65                      | 30                       | 40                       | 60                  |  |

| NCP11184A100LPG |        | 100 kHz   | 2.25                      | 18                       | 25                       | 37                  |  |

## Table 3. QUICK SELECTION TABLE

| Device    | Max. R <sub>DS(ON)</sub> [Ω] | Frequency [kHz] | Package        |

|-----------|------------------------------|-----------------|----------------|

|           |                              | 65              | PDIP-7, LSOP-7 |

| NCP11184  | 2.25                         | 100             | PDIP-7, LSOP-7 |

|           |                              | 130             | PDIP-7         |

| NCP11185  | 1.3                          | 65              | PDIP-7, LSOP-7 |

| NCF 11105 | 1.0                          | 130             | PDIP-7         |

| NCP11186  | 0.85                         | 65              | PDIP-7         |

| NCP11187  | 0.65                         | 65              | PDIP-7, LSOP-7 |

|           | 0.05                         | 100             | PDIP-7         |

Figure 1. Typical Application, VIN Connects to Rectified Input Voltage

Figure 2. Typical Application, VIN Connects to AC–Side of Input Voltage

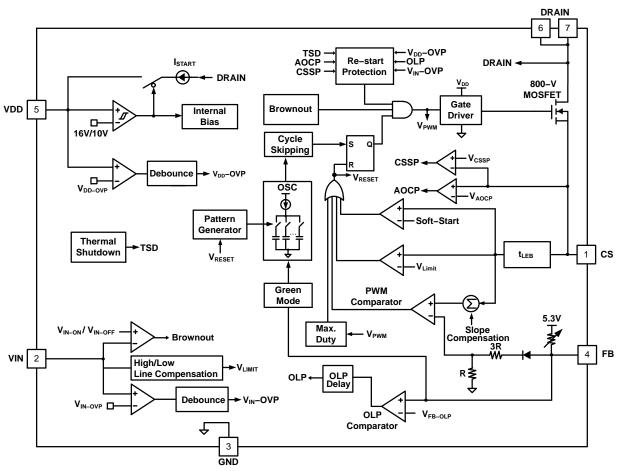

Figure 3. Simplified Internal Block Diagram

| Rating                                                                                                                                                                               | Symbol                | Value | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|------|

| Junction-to-Ambience Thermal Impedance (Note 1)<br>PDIP-7, LSOP-7, with 0.36 square inch, 2 oz. copper landing area<br>PDIP-7, LSOP-7, with 1 square inch, 2 oz. copper landing area | $R_{	heta JA}$        | TBD   | °C/W |

| Junction-to-Lead Thermal Impedance (Note 2)<br>PDIP-7, LSOP-7                                                                                                                        | $R_{	extsf{	heta}JL}$ | TBD   | °C/W |

1. JEDEC recommended environment as noted in JESD51-2

2. Measured from pin #7 (DRAIN) since it is the surface that copper area for heat sink is connected.

#### Table 5. RECOMMENDED OPERATING RANGE

| Rating                                                                                                 | Symbol | Min | Max                      | Unit |

|--------------------------------------------------------------------------------------------------------|--------|-----|--------------------------|------|

| Junction Temperature                                                                                   | TJ     | -40 | +125                     | °C   |

| Maximum Working Drain Current (T <sub>J</sub> = 100°C)<br>NCP11184<br>NCP11185<br>NCP11186<br>NCP11187 | ID     |     | 1.7<br>2.5<br>3.1<br>3.6 | A    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

## Table 6. MAXIMUM RATINGS TABLE (Note 3)

| Rating                                                                                    | Symbol             | Value                       | Unit |

|-------------------------------------------------------------------------------------------|--------------------|-----------------------------|------|

| DC Supply Voltage                                                                         | V <sub>DD</sub>    | -0.3 to 30                  | V    |

| FB-pin Input Voltage                                                                      | V <sub>FB</sub>    | -0.3 to 5.5                 | V    |

| CS-pin Input Voltage                                                                      | V <sub>CS</sub>    | -0.3 to 5.5                 | V    |

| VIN-pin Input Voltage                                                                     | V <sub>VIN</sub>   | -0.5 to 5.5                 | V    |

| DRAIN-pin Input Voltage                                                                   | V <sub>DRAIN</sub> | -0.3 to 800                 | V    |

| Maximum Pulsed Drain Current (Notes 4, 5)<br>NCP11184<br>NCP11185<br>NCP11186<br>NCP11187 | IDM                | 6.0<br>10.8<br>15.9<br>21.3 | A    |

| Single Pulsed Avalanche Energy (Note 6)<br>NCP11184<br>NCP11185<br>NCP11186<br>NCP11187   | E <sub>AS</sub>    | 21.6<br>48<br>114<br>204    | mJ   |

| Power Dissipation (PDIP-7, LSOP-7)                                                        | P <sub>D</sub>     | 1.25                        | W    |

| Operating Junction Temperature (Note 7)                                                   | TJ                 | -40 to +150                 | °C   |

| Storage Temperature                                                                       | T <sub>STG</sub>   | -40 to +150                 | °C   |

| Lead Temperature, Wave Soldering or IT, 10 seconds                                        | TL                 | 260                         | °C   |

| ESD Capability HBM, JESD22–A114<br>All Pins Except DRAIN Pin<br>DRAIN Pin                 |                    | 5.5 (TBD)<br>2.0 (TBD)      | kV   |

| ESD Capability CDM, JESD22–C101                                                           |                    | 2.0 (TBD)                   | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.All voltage values, except differential voltages, are given with respect to the ground terminal.

Repetitive rating pulse width is limited by maximum junction temperature.

The real value of IDM will be updated with characterization result.

6. Test conditions: L = 51 mH.

7. Although this parameter guarantees IC operation, it does not guarantee all electrical characteristics.

# Table 7. ELECTRICAL CHARACTERISTICS (T<sub>J</sub> = $-40^{\circ}$ C to $+125^{\circ}$ C unless otherwise noted)

| Parameter                                                                          | Test Conditions                                                                                                                                                                          | Symbol                | Min | Тур                             | Max                         | Unit  |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|---------------------------------|-----------------------------|-------|

| DRAIN AND MOSFET SECTION                                                           |                                                                                                                                                                                          |                       |     |                                 |                             |       |

| Power Switch and Start-up<br>Breakdown Voltage                                     | $V_{GS}$ = 0 V, I <sub>D</sub> = 1 mA, T <sub>J</sub> = 25°C                                                                                                                             | BV <sub>DSS</sub>     | 800 |                                 |                             | V     |

| Power Switch and Start-up Off-State<br>Leakage Current                             | CS and GND are shorted,<br>$V_{DD} \ge V_{DD-OVP}$ , $V_{DRAIN} = 800 V$<br>$T_J = 25^{\circ}C$<br>$T_J = 125^{\circ}C$                                                                  | I <sub>DSS</sub>      |     |                                 | TBD<br>TBD                  | μΑ    |

| Drain–Source On–State Resistance                                                   | $ \begin{array}{l} V_{DD} = 15 \ V, \ T_J = 25^\circ C \\ NCP11184, \ I_D = 0.3 \ A \\ NCP11185, \ I_D = 0.4 \ A \\ NCP11186, \ I_D = 0.5 \ A \\ NCP11187, \ I_D = 0.6 \ A \end{array} $ | R <sub>DS(on)</sub>   |     | 1.87<br>1.05<br>0.71<br>0.53    | 2.25<br>1.3<br>0.85<br>0.65 | Ω     |

| Rise Time (Note 8)                                                                 | $V_{DS}$ = 400 V, $V_{DD}$ = 15 V, 10 → 90%<br>NCP11184<br>NCP11185<br>NCP11186<br>NCP11187                                                                                              | tr                    |     | TBD<br>TBD<br>TBD<br>TBD<br>TBD |                             | ns    |

| Fall Time (Note 8)                                                                 | $\begin{array}{l} V_{DS} = 400 \; V, \; V_{DD} = 15 \; V, \; 90 \rightarrow 10\% \\ & \text{NCP11184} \\ & \text{NCP11185} \\ & \text{NCP11186} \\ & \text{NCP11187} \end{array}$        | t <sub>f</sub>        |     | TBD<br>TBD<br>TBD<br>TBD<br>TBD |                             | ns    |

| VDD SECTION                                                                        |                                                                                                                                                                                          |                       |     |                                 |                             |       |

| Start Threshold Voltage                                                            |                                                                                                                                                                                          | V <sub>DD-ON</sub>    |     | 16                              |                             | V     |

| Protection Mode                                                                    |                                                                                                                                                                                          | V <sub>DD-OFF</sub>   |     | 9.6                             |                             | V     |

| Normal Mode                                                                        |                                                                                                                                                                                          | V <sub>UVLO</sub>     |     | 7.8                             |                             | V     |

| Operating Supply Current                                                           | V <sub>DD</sub> = 15 V, V <sub>FB</sub> = 3 V<br>65 kHz Version<br>100 kHz Version<br>130 kHz Version                                                                                    | I <sub>DD-OP</sub>    |     |                                 | TBD<br>TBD<br>TBD           | mA    |

| Operating Supply Current without switching                                         | V <sub>DD</sub> = 15 V, V <sub>FB</sub> = 0 V                                                                                                                                            | I <sub>DD-OP2</sub>   |     |                                 | TBD                         | μΑ    |

| Threshold Voltage on V <sub>DD</sub> for HV<br>JFET Turn–On after Protection Mode  |                                                                                                                                                                                          | V <sub>DD-OLP</sub>   |     | 7.4                             |                             | V     |

| Internal Sink Current after Protection Mode                                        | V <sub>DD-OLP</sub> + 0.1 V                                                                                                                                                              | I <sub>DD-OLP</sub>   |     | 90                              |                             | μΑ    |

| Threshold Voltage to release from<br>Latch Protection                              | Latch version                                                                                                                                                                            | V <sub>DD-LH</sub>    |     | 6.9                             |                             | V     |

| Additional Sink Current after Latch–<br>Mode Protection                            | Latch version, $V_{DD}$ = 7 V                                                                                                                                                            | I <sub>DD-LH</sub>    |     | 30                              |                             | μΑ    |

| V <sub>DD</sub> Over–Voltage Protection                                            |                                                                                                                                                                                          | V <sub>DD-OLP</sub>   |     | 26                              |                             | V     |

| V <sub>DD</sub> Over–Voltage Protection<br>Debounce Counting Number                | 65–kHz version<br>100/130–kHz version                                                                                                                                                    | N <sub>VDDOVP</sub>   |     | 6<br>12                         |                             | pulse |

| V <sub>DD</sub> Level for I <sub>START1</sub> to I <sub>START2</sub><br>Transition |                                                                                                                                                                                          | V <sub>DD-INHIB</sub> |     | 2.1                             |                             | V     |

| Startup Current Flowing out of V <sub>DD</sub><br>Pin                              | $V_{DRAIN} = > 40 V, V_{DD} = 0 V$                                                                                                                                                       | I <sub>START1</sub>   |     | 0.5                             |                             | mA    |

| Startup Current Flowing out of $V_{DD}$ Pin                                        | $V_{DRAIN} = > 40 V,$<br>$V_{DD} = V_{DD-ON} - 0.5 V$                                                                                                                                    | I <sub>START2</sub>   |     | 4.5                             |                             | mA    |

| Threshold Voltage to Force Z <sub>FB</sub> Reset                                   | V <sub>FB</sub> < V <sub>FB-ZDC</sub> , V <sub>DD</sub> falling                                                                                                                          | V <sub>DD-ZFB</sub>   |     | 10                              |                             | V     |

8. Tested on a Flyback power converter. Result of just one golden sample.

9. Guaranteed by design.

# Table 7. ELECTRICAL CHARACTERISTICS (T<sub>J</sub> = $-40^{\circ}$ C to $+125^{\circ}$ C unless otherwise noted)

| Parameter                                                      | Test Conditions                                                                                        | Symbol                 | Min | Тур                   | Max | Unit   |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------|-----|-----------------------|-----|--------|

| OSCILLATOR SECTION                                             |                                                                                                        |                        |     |                       |     |        |

| Switching Frequency                                            | V <sub>FB</sub> = 4.5 V (V <sub>FB-OLP</sub> )<br>65-kHz Version<br>100-kHz Version<br>130-kHz Version | fosc                   |     | 65<br>100<br>130      |     | kHz    |

| Frequency Modulation Range                                     | V <sub>FB</sub> = 4.5 V (V <sub>FB-OLP</sub> )<br>65–kHz Version<br>100–kHz Version<br>130–kHz Version | f <sub>M</sub>         |     | ±5.2<br>±8.0<br>±10.4 |     | kHz    |

| Hopping Period                                                 |                                                                                                        | t <sub>HOP</sub>       |     | 12.5                  |     | ms     |

| Green–Mode Entry Frequency                                     | V <sub>FB</sub> = 3 V (V <sub>FB-OLP</sub> )<br>65–kHz Version<br>100–kHz Version<br>130–kHz Version   | fosc-N                 |     | 58.5<br>90<br>117     |     | kHz    |

| Green–Mode Ending Frequency                                    | V <sub>FB</sub> = 2.4 V (V <sub>FB-OLP</sub> )<br>65–kHz Version<br>100–kHz Version<br>130–kHz Version | fosc-g                 |     | 25.6<br>28<br>29      |     | kHz    |

| Entering–Burst Frequency                                       | $V_{FB} = V_{FB-ZDC}$                                                                                  | f <sub>OSC-ZDC</sub>   |     | 23                    |     | kHz    |

| Frequency Variation vs. V <sub>DD</sub> Devia-<br>tion         | $V_{DD} = 11 V \text{ to } 22 V$                                                                       | f <sub>DV</sub>        |     |                       | 5   | %      |

| Frequency Variation vs. Temperature Deviation (Note 9)         | $T_A = T_J = -40$ to $125^{\circ}C$                                                                    | fdt                    |     |                       | 5   | %      |

| VIN SECTION                                                    |                                                                                                        |                        |     |                       |     |        |

| PWM Turn-On (Brown-in) Threshold Voltage                       |                                                                                                        | V <sub>IN-ON</sub>     |     | 0.9                   |     | V      |

| PWM Turn–Off (Brownout) Threshold<br>Voltage                   | Default<br>Option                                                                                      | V <sub>IN-OFF</sub>    |     | 0.70<br>0.80          |     | V      |

| Brown-out Timer                                                | V <sub>FB</sub> = V <sub>FB-OPEN</sub><br>65–kHz Version<br>100–kHz Version                            | t <sub>D-VINOFF</sub>  |     | 62.5<br>81.25         |     | ms     |

| Threshold Voltage of V <sub>IN</sub> Over–Voltage Protection   | Default<br>Option A                                                                                    | V <sub>IN-OVP</sub>    |     | 3.85<br>4.15          |     | V      |

| Hysteresis for Recovery Level of V <sub>INOVP</sub> Comparator | Default<br>Option A                                                                                    | V <sub>IN-OVPHYS</sub> |     | 0.2<br>0.5            |     | V      |

| Debounce Time of V <sub>IN</sub> Over–Voltage<br>Protection    | 65–kHz version<br>100/130–kHz version                                                                  | t <sub>VINOVP</sub>    |     | 6<br>12               |     | pulse  |

| CURRENT SENSE SECTION                                          |                                                                                                        |                        |     |                       |     |        |

| Threshold Voltage for Current Limit                            | $V_{IN} = 1 V$<br>$V_{IN} = 3 V$                                                                       | V <sub>LIMIT</sub>     |     | 0.83<br>0.70          |     | V      |

| Current Limit Delay Time                                       |                                                                                                        | t <sub>CLD</sub>       |     | 100                   |     | ns     |

| Leading-Edge Blanking Time                                     | Soft Start (100/130-kHz version)<br>Steady State                                                       | t <sub>LEB</sub>       |     | 150<br>300            |     | ns     |

| Threshold of Abnormal Over–Current Protection                  | Enable after t <sub>SS</sub>                                                                           | V <sub>AOCP</sub>      |     | 1.25                  |     | V      |

| Debounce time for pulse of AOCP to be Counted                  |                                                                                                        | t <sub>ON-AOCP</sub>   |     | 110                   |     | ns     |

| Delay Time of Abnormal Over–Cur-<br>rent Protection            | Counting GATE Pulses                                                                                   | N <sub>AOCP</sub>      |     | 3                     |     | Pulses |

| Treshold Voltage for CSSP                                      | V <sub>IN</sub> = 1 V<br>V <sub>IN</sub> = 3 V                                                         | V <sub>CSSP</sub>      |     | 90<br>180             |     | mV     |

Tested on a Flyback power converter. Result of just one golden sample.

Guaranteed by design.

## Table 7. ELECTRICAL CHARACTERISTICS (T<sub>J</sub> = $-40^{\circ}$ C to $+125^{\circ}$ C unless otherwise noted)

| Parameter                                        | Test Conditions                                                                 | Symbol               | Min | Тур               | Max | Unit   |

|--------------------------------------------------|---------------------------------------------------------------------------------|----------------------|-----|-------------------|-----|--------|

| CURRENT SENSE SECTION                            | -                                                                               |                      |     |                   | -   |        |

| Minimum On-time of PWM Signal to<br>Trigger CSSP | 65–kHz version<br>100–kHz version<br>130–kHz version                            | t <sub>on-cssp</sub> |     | 4.6<br>3.0<br>2.3 |     | μs     |

| Delay Time of CSSP when CSSP<br>Condition is met | Counting GATE Pulses                                                            | N <sub>CSSP</sub>    |     | 4                 |     | Pulses |

| Period During Soft–Start Time                    | V <sub>FB</sub> = V <sub>FB-OPEN</sub><br>65/130–kHz Version<br>100–kHz Version | t <sub>SS</sub>      |     | 5.5<br>7.15       |     | ms     |

| Maximum Duty Cycle                               |                                                                                 | D <sub>MAX</sub>     |     | 80                |     | %      |

| Slope Compensation (Note 9)                      | Normalized to CS Signal<br>65–kHz Version<br>100–kHz Version<br>130–kHz Version | S <sub>E</sub>       |     | 30<br>46<br>60    |     | mV/μs  |

#### FEEDBACK INPUT SECTION

| Internal FB Voltage Attenuation                         |                                                                                 | A <sub>V</sub>         | 1/4.0         | -  |

|---------------------------------------------------------|---------------------------------------------------------------------------------|------------------------|---------------|----|

| Input Impedance                                         | $V_{FB} = 4 V$                                                                  | Z <sub>FB</sub>        | 15.25         | kΩ |

| Input Impedance in Burst Mode                           | $V_{FB} < V_{FB-ZDC}, V_{DD} > V_{DD-ZFB}$                                      | Z <sub>FB-ZDC</sub>    | 75            | kΩ |

| Time Duration of Switching from $Z_{FBZDC}$ to $Z_{FB}$ |                                                                                 | t <sub>ZFB</sub>       | 6.4           | ms |

| The Maximum Clamp of FB Voltage                         | FB Pin Open                                                                     | V <sub>FB-OPEN</sub>   | 5.1           | V  |

| FB Open–Loop Protection Triggering<br>Level             |                                                                                 | V <sub>FB-OLP</sub>    | 4.5           | V  |

| Delay Time of FB Pin Open–loop Pro-<br>tection          | V <sub>FB</sub> = V <sub>FB-OPEN</sub><br>65/130–kHz Version<br>100–kHz Version | t <sub>D-OLP</sub>     | 62.5<br>81.25 | ms |

| Green–Mode Entry FB Voltage                             |                                                                                 | V <sub>FB–N</sub>      | 3.0           | V  |

| Green–Mode Ending FB Voltage                            |                                                                                 | V <sub>FB-G</sub>      | 2.4           | V  |

| FB Threshold Voltage for Zero–Duty Recovery             |                                                                                 | V <sub>FB-ZDCR</sub>   | 1.8           | V  |

| FB Threshold Voltage for Zero–Duty                      |                                                                                 | V <sub>FB-ZDC</sub>    | 1.6           | V  |

| ZDC Hysteresis                                          | V <sub>FB-ZDCR</sub> - V <sub>FB-ZDC</sub>                                      | V <sub>FB-ZDCHYS</sub> | 0.2           | V  |

## THERMAL SHUT DOWN SECTION

| Protection Junction Temperature<br>(Note 9)      | T <sub>TSD</sub>     | 128 |    | °C |

|--------------------------------------------------|----------------------|-----|----|----|

| Hysteresis of Restarting Junction<br>Temperature | T <sub>TSD-HYS</sub> |     | 50 | °C |

Tested on a Flyback power converter. Result of just one golden sample.

Guaranteed by design.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### **Functional Descriptions**

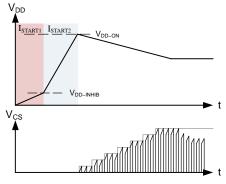

#### Startup & Soft-Start

At startup, an internal high–voltage current source connecting the DRAIN pin supplies internal bias and charges the external capacitor connected to the  $V_{DD}$  pin. When  $V_{DD}$  is lower than  $V_{DD-INHIB}$ , the charging is a smaller I<sub>START1</sub>. When  $V_{DD}$  exceeds  $V_{DD-INHIB}$ , charging current becomes a larger I<sub>START2</sub>. The lower charging current is designed to reduce power dissipation when  $V_{DD}$  is shorted to GND.

When  $V_{DD}$  level reaches  $V_{DD-ON}$ , the internal startup current source deactivates. At this moment, only the  $V_{DD}$  capacitor supplies an operating current to NCP1118X before the auxiliary winding of the main transformer provides the operating current. Moreover, the IC includes a function of soft–start to minimize the inrush current at startup. The built–in soft–start circuit significantly reduces the startup current spike and output voltage overshoot.

Figure 4. Startup and Soft Start

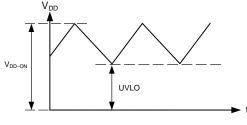

#### Under-Voltage Lockout (UVLO)

The turn-on and turn-off thresholds are fixed internally at 16 V and 7.8 V in normal mode as shown in Figure 5. During startup, the hold-up capacitor must be charged to 16 V through the internal high-voltage current source to enable the IC. The hold-up capacitor continues to supply  $V_{DD}$  before the energy can be delivered from auxiliary winding of the main transformer.  $V_{DD}$  must not drop below 7.8 V during startup. This large UVLO hysteresis window helps reducing size of the hold-up capacitor.

Normal Mode

Figure 5. V<sub>DD</sub> Behavior at Normal Mode

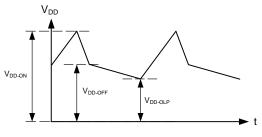

#### Auto Restart Operation

NCP1118x offers auto restart operation for the protections like feedback open-loop protection (OLP),  $V_{DD}$

over–voltage protection (V<sub>DD</sub> OVP), and over–temperature protection (OTP). Once one of the protections is trigger, the IC stops operation immediately and V<sub>DD</sub> starts to decrease. When V<sub>DD</sub> decreased to V<sub>DD-OFF</sub>, biaing current drawn from V<sub>DD</sub> pin is reduced to I<sub>DD-OLP</sub>, which stretches delay time for restart. When V<sub>DD</sub> decreases to V<sub>DD-OLP</sub>, the internal high–voltage startup circuit charges V<sub>DD</sub> again to re–initiate operation.

Protection Mode

Figure 6. V<sub>DD</sub> Behavior at Protection Mode

#### **Operating Current**

Operating current of NCP1118x is below 2 mA, and it is even lower in burst-mode operation. The low operating current enables better efficiency and reduces the requirement of  $V_{DD}$  hold-up capacitance.

#### **Green–Mode Operation**

The proprietary green–mode function provides reduced switching frequency in light–load and no–load conditions.  $V_{FB}$ , which is derived from the voltage feedback loop, is taken as a reference signal for green–mode operation. Once  $V_{FB}$  is decreased, switching frequency is also decreased to the minimum green–mode frequency  $V_{FB-ZDC}$ .

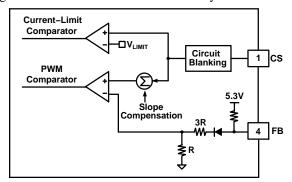

#### Current Sensing / PWM Current Limiting

Peak–current–mode control is utilized to regulate output voltage and provide pulse–by–pulse current limiting. The switching current is detected using the current–sensing resistor connecting at CS pin. The PWM duty cycle is determined by comparing this current sense signal  $V_{CS}$  with the feedback voltage  $V_{FB}$ . When  $V_{CS}$  reaches around  $V_{COMP} = (V_{FB}-0.6)/4$ , the PWM comparator generates a signal of the switch turns–off immediately.

Figure 7. Current Limit & PWM Comparator

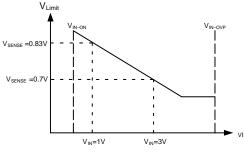

A current–limit comparator is used to set highest peak current through the power switch. For constant output power limit over universal input–voltage range, the peak–current threshold is adjusted by the voltage of  $V_{IN}$  pin.  $V_{IN}$  pin is connected to the rectified AC input line voltage through the resistive divider. The threshold voltage decreases as  $V_{IN}$ increases. Different  $V_{LIMIT}$  compensates the different maximum output power due to propagation delay.

Figure 8 shows V<sub>Limit</sub> variation depending on V<sub>IN</sub>.

Figure 8. V<sub>IN</sub> vs. V<sub>CS</sub>

## Leading-Edge Blanking (LEB)

Whenever the integrated MOSFET is turned on, a leading edge current occurs on the sense resistor. To avoid premature termination of the gate turn–on signal, a leading–edge blanking time is employed. During this blanking period, the current–limit comparator is disabled and the gate turn–on signal is maintained.

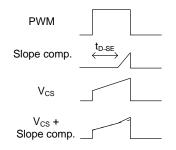

#### **Slope Compensation**

NCP1118x has built–in slope compensation to prevent sub–harmonic oscillator and improve stability. A sawtooth signal is generated when PWM pulse width exceeds  $t_{D-SE}$ . Initial voltage of the sawtooth waveform is 0.7 V. A weighted sum is then performs on current–sense signal and the sawtooth signal with weighting of 5/6 and 1/6 for each signal.

Slope of the sawtooth signal is 0.149 V/µs for 65–kHz version and 0.298 V/µs for 130–kHz version. The delay time  $t_{D-SE}$  is 6 µs for 65–kHz version and 3 µs for 130–kHz version, which is around 40% of duty cycle when operating at rated frequency.

**Figure 9. Slope Compensation**

#### V<sub>DD</sub> Over–Voltage Protection

$V_{DD}$  over-voltage protection prevents damage due to abnormal conditions. Once the  $V_{DD}$  voltage is over the

over–voltage protection voltage ( $V_{DD-OVP}$ ), and lasts for  $t_{D-VDDOVP}$  the PWM will be disabled. When the  $V_{DD}$  voltage drops below the  $V_{DD-OLP}$  the internal startup circuit turns on, and  $V_{DD}$  is charged to  $V_{DD-ON}$  to restart IC.

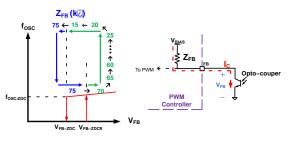

#### **Burst Mode and Feedback Impedance Switching**

NCP1118X actively varies FB-pin impedance ( $Z_{FB}$ ) in burst mode to reduce no-load power consumption. This technique can further reduce operating current of the controller when FB-pin voltage drops below V<sub>FB-ZDC</sub>.

Figure 10. Z<sub>FB</sub> Switching

#### **Brownout Protection**

Since the V<sub>IN</sub> pin is connected through a resistive divider to the rectified AC input line voltage, it can also be used for brownout protection. If V<sub>IN</sub> is less than 0.7 V, the PWM output is shut off. When V<sub>IN</sub> reaches over 0.9 V, the PWM output is turned on again. The hysteresis window for ON/OFF is around 0.2 V. The brownout voltage setting is determined by the potential divider formed with R<sub>Upper</sub> and R<sub>Lower</sub>. Equations to calculate the resistors are shown below:

$$V_{\text{IN}} = \frac{R_{\text{Lower}}}{R_{\text{Lower}} + R_{\text{Upper}}} \times V_{\text{AC}} \cdot \sqrt{2} \qquad (\text{eq. 1})$$

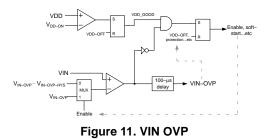

#### Input-Voltage Over-Voltage Protection

VIN pin is also used to realize over-voltage protection for AC input. More, while VIN voltage has been higher than  $V_{IN-OVP}$  when  $V_{DD}$  reaches  $V_{DD-ON}$  by HV start-up, switching operation will not be initiated.

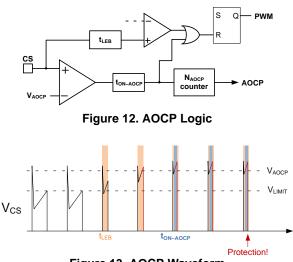

#### Abnormal Over–Current Protection (AOCP)

When conditions like shorted output, shorted secondary-side rectifier, and shorted transformer are met, an extremely high current can flow through power switch during leading-edge blanking time. Even though NCP1118x has over-load protection, it may not survive from such a severe current stress for the delay time of

over–load protection. AOCP is designed to protect NCP1118x from this kind of fault. If current–sensing signal exceeds AOCP threshold level for three consecutive switching periods, switching operation will be shut down to protect the power switch.

Figure 13. AOCP Waveform

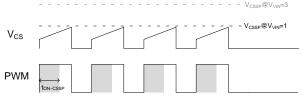

#### **Current–Sense Short Protection**

When CS pin is shorted to GND pin due to soldering defect, current-sense signal is not properly obtained. It causes current-mode PWM being not able to operate as designed. In this situation, PWM on-time will be large while current-sense gets no signal. Drain current will be out of control.

To protect power switch from this condition, NCP1118x shuts down by current–sense short protection (CSSP) when current–sense signal is kept low while PWM on–time is large enough. Treshold voltage of judging CSSP condition varies with VIN–pin voltage.

Figure 14. CSSP Waveform

### Thermal Shutdown

Thermal shutdown limits total power dissipation on chip. When the junction temperature exceeds  $T_{TSD}$ , the thermal sensor signals the shutdown logic and turns off most of the internal circuitry. The chip will resume operation if junction temperature drops below  $T_{TSD}$ - $T_{TSD}$ - $H_{YS}$ . Thermal shutdown is designed to protect the NCP1118X in the event of a fault condition. For continual operation, the controller should not exceed the absolute maximum junction temperature of  $T_J = +125^{\circ}C$ .

## **Over-Load Protection and Limited Power Control**

The FB voltage is saturated HIGH when the power supply output voltage drops below its nominal value and shunt regulator (ex. KA431) does not draw current through the opto-coupler. This occurs when the output feedback loop is open or output is short circuited. If the FB voltage is higher than a built-in threshold  $V_{FB-OLP}$  for longer than  $t_{D-OLR}$ PWM output is turned off. As PWM output is turned off,  $V_{DD}$  begins decreasing since no more energy is delivered from the auxiliary winding.

As the protection is triggered,  $V_{DD}$  enters into auto-restart UVLO mode, which extends the time it take to restart operation. This prevents the power supply from overheating at the overload conditions.

| Device          | R <sub>DS(ON)</sub> (Ω) | f <sub>OSC</sub> (kHz) | Package             | Shipping <sup>†</sup> |

|-----------------|-------------------------|------------------------|---------------------|-----------------------|

| NCP11184A065PG  | 2.25                    | 65                     | PDIP-7<br>(Pb-Free) |                       |

| NCP11185A065PG  | 1.3                     | 65                     |                     |                       |

| NCP11186A065PG  | 0.85                    | 65                     |                     |                       |

| NCP11187A065PG  | 0.65                    | 65                     |                     |                       |

| NCP11184A100PG  | 2.25                    | 100                    |                     | 50 Units / Rail       |

| NCP11187A100PG  | 0.65                    | 100                    |                     |                       |

| NCP11184A130PG  | 2.25                    | 130                    |                     |                       |

| NCP11185A130PG  | 1.3                     | 130                    |                     |                       |

| NCP11184A065LPG | 2.25                    | 65                     | LSOP-7<br>(Pb-Free) |                       |

| NCP11185A065LPG | 1.3                     | 65                     |                     |                       |

| NCP11187A065LPG | 0.65                    | 65                     |                     | 50 Units / Rail       |

| NCP11184A100LPG | 2.25                    | 100                    |                     |                       |

#### ORDERING INFORMATION

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

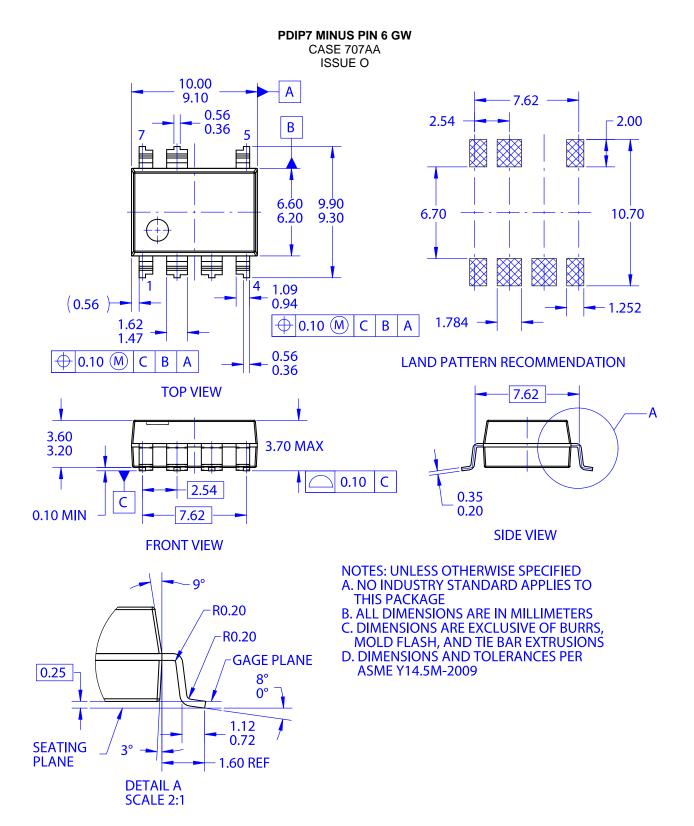

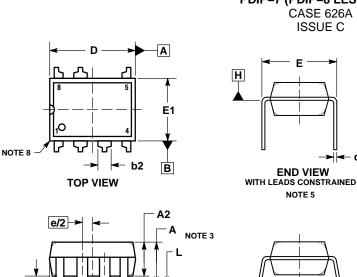

# PACKAGE DIMENSIONS

## PACKAGE DIMENSIONS

SEATING PLANE

$\oplus$  0.010  $\otimes$  C A  $\otimes$  B  $\otimes$

С

8X b

PDIP-7 (PDIP-8 LESS PIN 6) CASE 626A **ISSUE C**

eB

**END VIEW**

NOTE 6

NOTES

м

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: INCHES. DIMENSIONS A, A1 AND L ARE MEASURED WITH THE PACK-2 3.

- 4

- AGE SEATED IN JEDEC SEATING PLANE GAUGE GS-3. DIMENSIONS D, D1 AND E1 DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS ARE NOT TO EXCEED 0.10 INCH. 5

- DIMENSION E IS MEASURED AT A POINT 0.015 BELOW DATUM PLANE H WITH THE LEADS CONSTRAINED PERPENDICULAR TO DATUM C. DIMENSION eB IS MEASURED AT THE LEAD TIPS WITH THE

- 6 LEADS UNCONSTRAINED. DATUM PLANE H IS COINCIDENT WITH THE BOTTOM OF THE 7

- LEADS, WHERE THE LEADS EXIT THE BODY PACKAGE CONTOUR IS OPTIONAL (ROUNDED OR SQUARE 8. ORNERS

| CORNERS). |           |       |             |       |  |  |

|-----------|-----------|-------|-------------|-------|--|--|

|           | INC       | HES   | MILLIMETERS |       |  |  |

| DIM       | MIN       | MAX   | MIN         | MAX   |  |  |

| Α         |           | 0.210 |             | 5.33  |  |  |

| A1        | 0.015     |       | 0.38        |       |  |  |

| A2        | 0.115     | 0.195 | 2.92        | 4.95  |  |  |

| q         | 0.014     | 0.022 | 0.35        | 0.56  |  |  |

| b2        | 0.060 TYP |       | 1.52 TYP    |       |  |  |

| c         | 0.008     | 0.014 | 0.20        | 0.36  |  |  |

| D         | 0.355     | 0.400 | 9.02        | 10.16 |  |  |

| D1        | 0.005     |       | 0.13        |       |  |  |

| Е         | 0.300     | 0.325 | 7.62        | 8.26  |  |  |

| E1        | 0.240     | 0.280 | 6.10        | 7.11  |  |  |

| е         | 0.100 BSC |       | 2.54 BSC    |       |  |  |

| eB        |           | 0.430 |             | 10.92 |  |  |

| -         | 0 115     | 0 150 | 2 92        | 3.81  |  |  |

10°

10°

mWSaver is a registered trademark of Semiconductor Components Industries, LLC. Energy Star is a registered trademark of the U.S. Environmental Protection Agency

ON Semiconductor and ware trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

Phone: 421 33 790 2910

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT

D1

е

SIDE VIEW

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative