# Product Preview

# LDO Regulator, 500 mA, Ultra-Low Noise, High PSRR

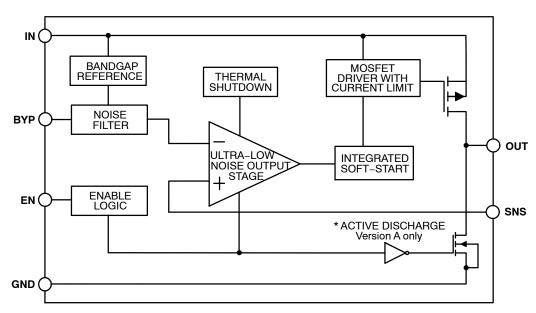

The NCP185 is designed to offer class leading noise performance only  $1.8~\mu V_{RMS}$  and excellent dynamic performance. In combination with very low quiescent current typ. 95  $\mu A$  the NCP185 is the best choice for latest generation of images sensors, wifi modules and battery powered devices. Minimum input voltage only 1.3 V allows to use the NCP185 in very wide range of applications in combination with very low dropout device improves efficiency and power dissipation.

#### **Features**

- Operating Input Voltage Range: 1.3 V to 5.5 V

- Available in Fixed Voltage Option: 1.2 V to 5.3 V

- ±2% Accuracy Over Load/Temperature

- Ultra Low Quiescent Current Typ. 95 μA

- Standby Current: Typ. 0.1 μA

- Very Low Dropout: 260 mV for 1.2 V at 500 mA

- Ultra High PSRR: Typ. 80 dB at 50 mA, f = 1 kHz

- Ultra Low Noise: 1.8 μV<sub>RMS</sub>

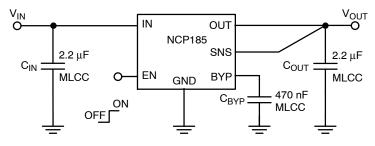

- Stable with a 2.2 μF Small Case Size Ceramic Capacitors

- Available in WLCSP6 1.2 mm x 0.8 mm

- WDFNW8 2 mm x 2 mm

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

# **Typical Applications**

- Battery-powered Equipment

- Wireless LAN Devices

- Smartphones, Tablets

- Cameras, DVRs, STB and Camcorders

Figure 1. Typical Application Schematics

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

# ON Semiconductor®

www.onsemi.com

# MARKING DIAGRAMS

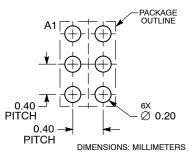

WLCSP6 CASE 567MV

WDFNW8 CASE 511CL

XX = Specific Device Code

M = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

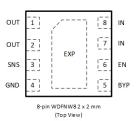

# **PIN CONNECTIONS**

6-pin WLCSP 1.2 x 0.8 mm (Top View)

# **ORDERING INFORMATION**

See detailed ordering, marking and shipping information on page 3 of this data sheet.

Figure 2. Simplified Schematic Block Diagram

# PIN FUNCTION DESCRIPTION

| Pin No.<br>WLCSP6 | Pin No.<br>WDFNW8 | Pin<br>Name | Description                                                                                                             |

|-------------------|-------------------|-------------|-------------------------------------------------------------------------------------------------------------------------|

| A1                | 7, 8              | IN          | Input voltage supply pin.                                                                                               |

| A2                | 1, 2              | OUT         | Regulated output voltage. The output should be bypassed with small 2.2 μF ceramic capacitor.                            |

| B1                | 6                 | EN          | Chip enable: Applying $V_{EN}$ < 0.2 V disables the regulator, Pulling $V_{EN}$ > 0.7 V enables the LDO.                |

| B2                | 3                 | SNS         | Sense pin should be connected directly to VOUT on load side to compensate PCB trace resistance and reduce voltage drop. |

| C1                | 5                 | BYP         | The 470 nF bypass capacitor should be connected to this pin to ensure excellent noise parameter                         |

| C2                | 4                 | GND         | Common ground connection                                                                                                |

| -                 | EPAD              | EPAD        | Expose pad should be tied to ground plane for better power dissipation.                                                 |

### **ABSOLUTE MAXIMUM RATINGS**

| Rating                                        | Symbol             | Value                                   | Unit |

|-----------------------------------------------|--------------------|-----------------------------------------|------|

| Input Voltage (Note 1)                        | V <sub>IN</sub>    | -0.3 V to 6                             | V    |

| Output Voltage                                | V <sub>OUT</sub>   | -0.3 to V <sub>IN</sub> + 0.3, max. 6 V | V    |

| Chip Enable Input                             | V <sub>CE</sub>    | -0.3 V to 6                             | V    |

| Bypass Pin                                    | V <sub>BYP</sub>   | -0.3 V to 6                             | V    |

| Sense Pin                                     | V <sub>SNS</sub>   | -0.3 V to 6                             | V    |

| Output Short Circuit Duration                 | t <sub>SC</sub>    | unlimited                               | S    |

| Maximum Junction Temperature                  | TJ                 | 150                                     | °C   |

| Storage Temperature                           | T <sub>STG</sub>   | -55 to 150                              | °C   |

| ESD Capability, Human Body Model (Note 2)     | ESD <sub>HBM</sub> | 2000                                    | V    |

| ESD Capability, Machine Model (Note 2)        | ESD <sub>MM</sub>  | 200                                     | V    |

| ESD Capability, Charged Device Model (Note 2) | ESD <sub>CDM</sub> | 1000                                    | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 2. This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model tested per EIA/JESD22-A114

- ESD Machine Model tested per EIA/JESD22-A115

- ESD Charged Device Model tested per EIA/JESD22-C101, Field Induced Charge Model

- Latchup Current Maximum Rating tested per JEDEC standard: JESD78.

#### THERMAL CHARACTERISTICS

| Rating                                                                        | Symbol          | Value | Unit |

|-------------------------------------------------------------------------------|-----------------|-------|------|

| Thermal Characteristics, WLCSP6 (Note 3), Thermal Resistance, Junction-to-Air | В               | TBD   | °C/W |

| Thermal Characteristics, WDFNW8 (Note 3), Thermal Resistance, Junction-to-Air | $R_{\theta JA}$ | TBD   | C/VV |

<sup>3.</sup> Measured according to JEDEC board specification. Detailed description of the board can be found in JESD51-7

**ELECTRICAL CHARACTERISTICS**  $-40^{\circ}C \le T_J \le 125^{\circ}C$ ;  $V_{IN} = V_{OUT(NOM)} + 0.5$  V;  $I_{OUT} = 1$  mA,  $C_{IN} = C_{OUT} = 2.2$   $\mu$ F,  $C_{BYP} = 470$  nF, unless otherwise noted.  $V_{EN} = 1.2$  V. Typical values are at  $T_J = +25^{\circ}C$  (Note 4).

| Parameter                          | Test Conditions                                                                                                |                                                          | Symbol              | Min | Тур                  | Max | Unit          |

|------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------|-----|----------------------|-----|---------------|

| Operating Input Voltage            |                                                                                                                |                                                          | V <sub>IN</sub>     | 1.3 |                      | 5.5 | V             |

| Output Voltage Accuracy            | $V_{IN} = (V_{OUT(NOM)} + 0.5 \text{ V}) \text{ to } 5.5 \text{ V}$<br>0 mA $\leq I_{OUT} \leq 500 \text{ mA}$ |                                                          | V <sub>OUT</sub>    | -2  |                      | +2  | %             |

| Line Regulation                    | V <sub>OUT(NOM)</sub> + 0.5                                                                                    | $5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ | Line <sub>Reg</sub> |     | 0.02                 |     | %/V           |

| Load Regulation                    | I <sub>OUT</sub> = 1 mA                                                                                        | A to 500 mA                                              | Load <sub>Reg</sub> |     | 1                    |     | mV            |

| Dropout Voltage (Note 5)           | I <sub>OUT</sub> = 500 mA                                                                                      | V <sub>OUT(NOM)</sub> = 1.2 V                            | $V_{DO}$            |     | 260                  | TBD | mV            |

| Output Current Limit               | V <sub>OUT</sub> = 90%                                                                                         | V <sub>OUT(NOM)</sub>                                    | I <sub>CL</sub>     | 600 | 800                  |     | A             |

| Short Circuit Current              | V <sub>OUT</sub> = 0 V                                                                                         |                                                          | I <sub>SC</sub>     |     | 850                  |     | mA            |

| Quiescent Current                  | I <sub>OUT</sub> = 0 mA                                                                                        |                                                          | ΙQ                  |     | 95                   | TBD | μΑ            |

| Shutdown Current                   | V <sub>EN</sub> ≤ 0.4 V, V <sub>IN</sub> = 5.5 V                                                               |                                                          | I <sub>DIS</sub>    |     | 0.01                 | 1   | μΑ            |

| EN Pin Threshold Voltage           | EN Input Voltage "H"                                                                                           |                                                          | V <sub>ENH</sub>    | 0.7 |                      |     | .,            |

|                                    | EN Input \                                                                                                     | /oltage "L"                                              | V <sub>ENL</sub>    |     |                      | 0.2 | V             |

| EN Pull Down Current               | V <sub>EN</sub> = 5.5 V                                                                                        |                                                          | I <sub>EN</sub>     |     | 0.2                  | 0.5 | μΑ            |

| Turn-On Time                       | $C_{OUT}$ = 1 $\mu$ F, From assertion of $V_{EN}$ to $V_{OUT}$ = 95% $V_{OUT(NOM)}$                            |                                                          |                     |     | TBD                  |     | μs            |

| Power Supply Rejection Ratio       | I <sub>OUT</sub> = 50 mA                                                                                       | f = 100 Hz<br>f = 1 kHz<br>f = 10 kHz<br>f = 100 kHz     | PSRR                |     | 91<br>92<br>85<br>60 |     | dB            |

| Output Voltage Noise               | f = 10 Hz to 100 kHz                                                                                           | I <sub>OUT</sub> = 50 mA                                 | V <sub>N</sub>      |     | 1.8                  |     | $\mu V_{RMS}$ |

| Thermal Shutdown Threshold         | Temperature rising                                                                                             |                                                          | T <sub>SDH</sub>    |     | 160                  |     | °C            |

|                                    | Temperature falling                                                                                            |                                                          | T <sub>SDL</sub>    |     | 140                  |     | °C            |

| Active Output Discharge Resistance | arge Resistance V <sub>EN</sub> < 0.4 V, Version A only                                                        |                                                          | R <sub>DIS</sub>    |     | 280                  |     | Ω             |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

# **DEVICE ORDERING INFORMATION**

| Device | Marking | Package             | Shipping <sup>†</sup> |

|--------|---------|---------------------|-----------------------|

| NCP185 | TBD     | WLCSP6<br>(Pb-Free) | TBD / Tape & Reel     |

| NCP185 | TBD     | WDFNW8<br>(Pb-Free) | TBD / Tape & Reel     |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>4.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization. Production tested at T<sub>A</sub> = 25°C. Low duty cycle pulse techniques are used during the testing to maintain the junction temperature as close to ambient as possible.

<sup>5.</sup> Dropout voltage is characterized when V<sub>OUT</sub> falls 20 mV below V<sub>OUT</sub>(NOM).

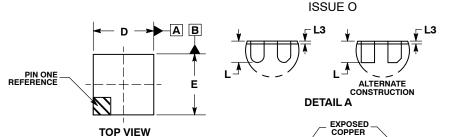

# **PACKAGE DIMENSIONS**

# WLCSP6, 1.20x0.80 CASE 567MV **ISSUE B**

**BOTTOM VIEW**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. COPLANARITY APPLIES TO SPHERICAL CROWNS OF SOLDER BALLS.

|     | MILLIMETERS |          |  |  |  |

|-----|-------------|----------|--|--|--|

| DIM | MIN MAX     |          |  |  |  |

| Α   |             | 0.33     |  |  |  |

| A1  | 0.04        | 0.08     |  |  |  |

| A2  | 0.23        | 0.23 REF |  |  |  |

| b   | 0.24        | 0.30     |  |  |  |

| D   | 1.20 BSC    |          |  |  |  |

| Е   | 0.80 BSC    |          |  |  |  |

| е   | 0.40 BSC    |          |  |  |  |

### **RECOMMENDED SOLDERING FOOTPRINT\***

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

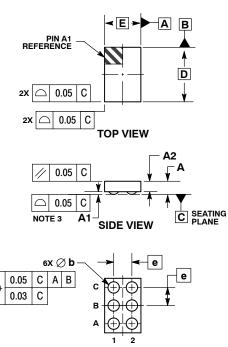

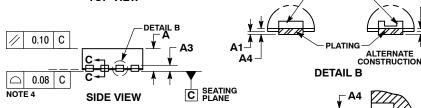

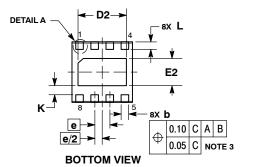

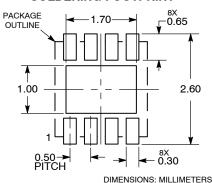

#### PACKAGE DIMENSIONS

# WDFNW8 2x2, 0.5P CASE 511CL

PLATED -

SECTION C-C

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS. DIMENSION & APPLIES TO PLATED

- TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM FROM TERMINAL TIP.

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

- THIS DEVICE CONTAINS WETTABLE FLANK DESIGN FEATURES TO AID IN FILLET FOR-MATION ON THE LEADS DURING MOUNTING.

|     | MILLIMETERS |          |      |  |

|-----|-------------|----------|------|--|

| DIM | MIN         | NOM      | MAX  |  |

| Α   | 0.70        | 0.75     | 0.80 |  |

| A1  | 0.00        | 0.03     | 0.05 |  |

| А3  |             | 0.20 REF |      |  |

| A4  | 0.05        | 0.10     | 0.15 |  |

| b   | 0.20        | 0.25     | 0.30 |  |

| D   | 1.90        | 2.00     | 2.10 |  |

| D2  | 1.50        | 1.60     | 1.70 |  |

| Е   | 1.90        | 2.00     | 2.10 |  |

| E2  | 0.80        | 0.90     | 1.00 |  |

| е   | 0.50 BSC    |          |      |  |

| Κ   | 0.25        |          |      |  |

| L   | 0.20        | 0.30     | 0.40 |  |

| L3  | 0.00        | 0.05     | 0.10 |  |

#### **RECOMMENDED** DERING FOOTPRINT\* SOL

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative