## Product Preview

# +48 V Electronic Fuse

The NIS7080 is a cost effective, resettable electronic fuse which is designed to protect the load from overcurrent events, overvoltage conditions, short circuits and other faults. It includes a programmable overvoltage and undervoltage protection, adjustable internal FET power limiting, thermal protection, selectable auto-retry and latch behavior, programmable restart, insertion delay and fault timers, load current monitoring, fault and power good indicator pins and digital enable pin. The NIS7080 is perfectly suitable for typical 48 V operation in various industrial and automotive applications and the input voltage of the device is tolerant to +80 V.

#### **Features**

- 55 mΩ Typical Rds(ON)

- Programmable Overvoltage and Undervoltage Protection

- Active-Low Open-Drain Power Good Indicator

- Active-Low Open-Drain FAULT Pin Indicator

- Pin Selectable Auto-Restart/Latch Operation Mode

- Pin Selectable Circuit Breaker Operation Mode

- Adjustable Output Current Limit Protection

- Adjustable Power Limiting for Internal FET

- Adjustable FAULT Pin Timer

- Adjustable Restart Timer for Auto-Restart Mode Operation

- Adjustable Hot-Plug Insertion Delay

- Integrated Current Monitoring

- Digital Active-Low Enable Pin

- NIV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

## **Typical Applications**

- Automotive

- Telecom

- Industrial

- Industrial Power Supplies

- Servers

- Power Tools

- Battery Management

- Lighting Systems

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

## ON Semiconductor®

www.onsemi.com

## **MARKING DIAGRAM**

XXXX = Specific Device Code Assembly Location

Υ = Year ww = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

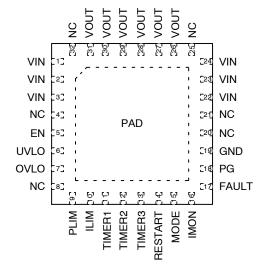

## **PIN CONNECTIONS**

## **ORDERING INFORMATION**

See detailed ordering and shipping information on page 10 of this data sheet.

**Table 1. PIN FUNCTION DESCRIPTION**

| Pin Number        | Function | Description                                                                                                                     |  |  |

|-------------------|----------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1,2,3,22,23,24    | VIN      | Input Voltage                                                                                                                   |  |  |

| 4,8,20,21,25,32   | NC       | Do Not Connect                                                                                                                  |  |  |

| 5                 | EN       | Active Low Enable pin. Default pull down. By default, device is enabled. Pull High to disable.                                  |  |  |

| 6                 | UVLO     | Undervoltage Lockout adjustment                                                                                                 |  |  |

| 7                 | OVLO     | Overvoltage Lockout adjustment pin                                                                                              |  |  |

| 15                | MODE     | Operation mode. Connect to GND or leave floating for power/current limit mode. Tie to logic high for circuit breaker only mode. |  |  |

| 9                 | PLIM     | Power Limit pin adjusted by resistor                                                                                            |  |  |

| 10                | ILIM     | Current Limit pin adjusted by resistor                                                                                          |  |  |

| 11                | TIMER1   | FAULT Timer value adjustment pin. Connect capacitor to GND                                                                      |  |  |

| 12                | TIMER2   | RESTART Timer value adjustment pin. Connect capacitor to GND                                                                    |  |  |

| 13                | TIMER3   | INSERTION DELAY Timer value adjustment pin. Connect capacitor to GND                                                            |  |  |

| 14                | RESTART  | Auto-Retry/Latch mode select pin. Tie to GND or leave floating for auto-restart. Connect to logic High for Latch mode.          |  |  |

| 16                | IMON     | Current Monitoring Resistor connection pin                                                                                      |  |  |

| 17                | FAULT    | Active Low FAULT pin. Leave floating if not used or pull up to +5 V with 10 k $\Omega$ pull up resistor.                        |  |  |

| 18                | PG       | Active Low Power Good pin. Leave floating if not used or pull up to +5 V with 10 k $\Omega$ pull up resistor.                   |  |  |

| 19                | GND      | Must be connected to Ground                                                                                                     |  |  |

| 26,27,28,29,30,31 | OUT      | Output Voltage                                                                                                                  |  |  |

| 33(PAD)           | PAD      | Can be left floating or connected to Ground plane for better thermals                                                           |  |  |

## **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                                                      | Symbol              | Value       | Unit       |

|-------------------------------------------------------------------------------------------------------------|---------------------|-------------|------------|

| IN, OUT Pin Input Voltage to GND, operating, steady-state (Note 1)                                          | V <sub>IN/OUT</sub> | -0.6 to +80 | V          |

| All Other pins                                                                                              | Vpin                | -0.6 to 5.5 | V          |

| Thermal Resistance, Junction-to-Air 0.1 in <sup>2</sup> copper (Note 2) 0.5 in <sup>2</sup> copper (Note 2) | θЈА                 | TBD<br>TBD  | °C/W       |

| Thermal Resistance, Junction-to-Lead                                                                        | $\theta_{JL}$       | TBD         | °C/W       |

| Total Power Dissipation @ T <sub>A</sub> = 25°C Derate above 25°C                                           | P <sub>MAX</sub>    | TBD<br>TBD  | W<br>mW/°C |

| Operating Temperature Range (Note 3)                                                                        | TJ                  | -40 to 125  | °C         |

| Non-operating Temperature Range                                                                             | T <sub>J</sub>      | -55 to 155  | °C         |

| Lead Temperature, Soldering (10 Sec)                                                                        | T <sub>L</sub>      | 260         | °C         |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Negative voltage will not damage device provided that the power dissipation is limited to the rated allowable power for the package.

- 2. 1 oz copper, double-sided FR4.

- 3. Thermal limit is set above the maximum thermal rating. It is not recommended to operate this device at temperatures greater than maximum ratings for extended periods of time.

**Table 3. ELECTRICAL CHARACTERISTICS**

| Characteristics                                                              | Symbol                  | Min | Тур                    | Max | Unit |

|------------------------------------------------------------------------------|-------------------------|-----|------------------------|-----|------|

| POWER FET                                                                    |                         |     |                        |     | -    |

| ON Resistance, T <sub>J</sub> = 25°C                                         | R <sub>ds(ON)</sub>     |     | 55                     |     | mΩ   |

| ON Resistance, T <sub>J</sub> = 85°C                                         |                         |     | TBD                    |     |      |

| Continuous Current (Ta = 25°C, 0.5 sq in pad)                                | ld                      |     | 8                      |     | Α    |

| Off State Leakage (V <sub>IN</sub> = 48 V, V <sub>EN</sub> = 5 V, Ta = 25°C) | loff                    |     | 1                      |     | μΑ   |

| THERMAL SHUTDOWN                                                             |                         |     |                        |     |      |

| Shutdown Temperature                                                         | T <sub>SD</sub>         |     | 175                    |     | °C   |

| Thermal Hysteresis (Auto-Restart Mode only)                                  | T <sub>HYST</sub>       |     | 40                     |     | °C   |

| UNDERVOLTAGE LOCKOUT                                                         |                         |     |                        |     |      |

| Undervoltage Lockout                                                         | V <sub>UVLO</sub>       |     | Adj.                   |     | V    |

| Undervoltage Lockout Default Value (No R1,R2,R3 connected)                   | V <sub>UVLO</sub>       |     | 8                      |     | V    |

| Undervoltage Lockout Threshold value                                         | V <sub>UV</sub>         |     | TBD                    |     | V    |

| Undervoltage Lockout Hysteresis                                              | V <sub>(UVLO)Hyst</sub> |     | 0.1                    |     | V    |

| Undervoltage Lockout Response Time                                           | t <sub>UVLO</sub>       |     | 5                      |     | μs   |

| Power On Reset Threshold voltage                                             | V <sub>POR</sub>        |     | 6                      |     | V    |

| Power On Reset Threshold voltage Hysteresis                                  | V <sub>POR(Hyst)</sub>  |     | 0.1                    |     | V    |

| OVERVOLTAGE LOCKOUT                                                          |                         |     |                        |     |      |

| Overvoltage Lockout                                                          | V <sub>OVLO</sub>       |     | Adj.                   |     | V    |

| Overvoltage Lockout Threshold value                                          | V <sub>OV</sub>         |     | TBD                    |     | V    |

| Overvoltage Lockout Hysteresis                                               | V <sub>(OVLO)Hyst</sub> |     | 0.1                    |     | V    |

| Output Clamping Voltage Response Time                                        | t <sub>OVLO</sub>       |     | 5                      |     | μs   |

| FORWARD CURRENT LIMIT                                                        |                         |     |                        |     |      |

| Current Limit (R <sub>LIM</sub> = TBD)                                       | I <sub>LIM</sub>        |     | Adj.                   |     | Α    |

| Circuit Breaker Level                                                        | I <sub>CB</sub>         |     | 1.5 x l <sub>LIM</sub> |     | Α    |

| Current Limit Response Time                                                  | t <sub>ILIM</sub>       |     | 10                     |     | μs   |

| Circuit Breaker Response Time                                                | t <sub>CB</sub>         |     | 1                      |     | μs   |

| INTERNAL FET POWER LIMIT                                                     |                         |     |                        |     |      |

| Internal FET Power Limit Threshold (RPLIM = TBD)                             | PLIM <sub>TH</sub>      |     | Adj.                   |     | W    |

| Power Limit Threshold Current                                                | I <sub>PLIM</sub>       |     | TBD                    |     | μΑ   |

| LOGIC INPUT/OUTPUT                                                           |                         |     |                        |     |      |

| Logic Level Low, EN pin (Device Enabled)                                     | V <sub>IL(EN)</sub>     |     |                        | 0.8 | V    |

| Logic Level High, EN pin (Device Disabled)                                   | V <sub>IH(EN)</sub>     | 2   |                        |     | V    |

| Output Voltage Low (FAULT, PGOOD pins)                                       | V <sub>OL</sub>         |     |                        | 0.3 | V    |

| Logic High Sink Current (FAULT, PGOOD pins)                                  | I <sub>O</sub>          |     | 0.5                    |     | mA   |

| POWER GOOD                                                                   |                         |     |                        |     |      |

| Power Good VIN-VOUT threshold voltage                                        | V <sub>PGOOD(Th)</sub>  |     | 1                      |     | V    |

| TIMER CONTROL                                                                |                         |     |                        |     |      |

| Timer Pin Threshold voltage, TIMER1,2,3                                      | V <sub>TIMER(Th)</sub>  |     | 4                      |     | V    |

| Timer Pin Current Source value                                               | I <sub>TIMER</sub>      |     | TBD                    |     | μΑ   |

| LOAD CURRENT MONITORING                                                      |                         |     |                        |     |      |

| Load Monitor Sense Current (RIMON = TBD)                                     | I <sub>SENSE</sub>      |     | 1                      |     | mA/A |

| Current Sense Measurement Error                                              | I <sub>SENSE(Err)</sub> |     | 10                     |     | %    |

**Table 3. ELECTRICAL CHARACTERISTICS**

| Characteristics                                                          | Symbol                 | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------|------------------------|-----|-----|-----|------|

| SUPPLY CURRENT                                                           |                        |     |     |     |      |

| Bias Current Operational (V <sub>IN</sub> = 48 V, V <sub>EN</sub> = 0 V) | I <sub>BIAS(ON)</sub>  |     | TBD |     | μΑ   |

| Bias Current Shutdown (V <sub>IN</sub> = 48 V, V <sub>EN</sub> = 5 V)    | I <sub>BIAS(OFF)</sub> |     | TBD |     | μΑ   |

| ESD CHARACTERISTICS                                                      |                        |     |     |     |      |

| Human Body Model (All pins)                                              | ESD-HBM                |     | ±2  |     | kV   |

| Charged Device Model (All pins)                                          | ESD-CDM                |     | 500 |     | V    |

| IEC61000-4-2 (VIN, VOUT pins                                             | IEC                    |     | 4   |     | kV   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

**Table 4. PROTECTION FEATURES**

| Protection                 | Min                                 | Тур | Max                                                                                        | Unit | Test Conditions                                                          |

|----------------------------|-------------------------------------|-----|--------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------|

| Ground Loss Disable time   | 5                                   |     |                                                                                            | μs   | Resistor from GND pin to Ground goes from 100 m $\Omega$ to 1 M $\Omega$ |

| ISO7637-2                  | -300                                |     |                                                                                            | V    | Pulse 1, 500 pulses                                                      |

|                            | 112                                 |     |                                                                                            | V    | Pulse 2a, 500 pulses                                                     |

|                            | 20                                  |     |                                                                                            | V    | Pulse 2b, 10 pulses                                                      |

|                            | -200                                |     |                                                                                            | V    | Pulse 3a, 1 hour                                                         |

|                            | 200                                 |     |                                                                                            | V    | Pulse 3b, 1 hour                                                         |

| ISO16750-2                 | 40                                  |     |                                                                                            | V    | Test B, U <sub>N</sub> = 24 V                                            |

| ISO7637-3                  | 112                                 |     |                                                                                            | V    | Pulse 2a, Level IV                                                       |

|                            | -150                                |     |                                                                                            | V    | Pulse 3a, Level IV                                                       |

|                            | 150                                 |     |                                                                                            | V    | Pulse 3b, Level IV                                                       |

| JESD78                     | -100                                |     | +100                                                                                       | mA   | Class II                                                                 |

| IEC-61967-4                |                                     |     | 80 (150–300 kHz)<br>58 (0.5–2 MHz)<br>50 (5–10 MHz)<br>40 (10–100 MHz)<br>30 (100–300 MHz) | dΒμV | VIN = 13.5 V / 1 A<br>150 Ω method                                       |

| IEC 62132-4<br>ISO 11452-7 | 35 (1–110 MHz)<br>24 (110–1000 MHz) |     |                                                                                            | dBm  | VIN = 13.5 V<br>F = 1-1000 MHz<br>CW, AM (1 kHz, 80%)                    |

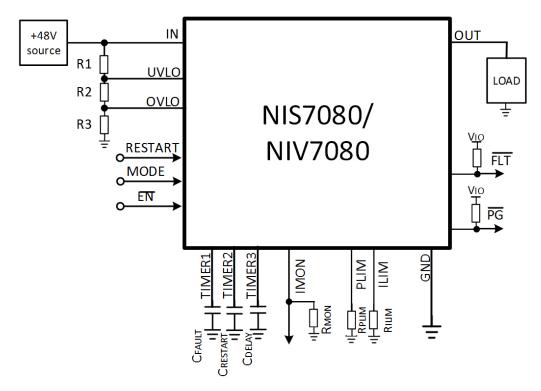

Figure 1. Typical Application Circuit

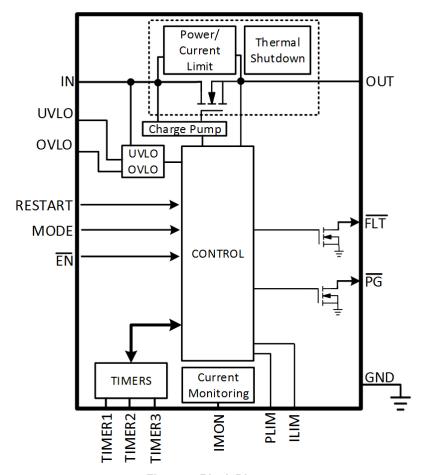

Figure 2. Block Diagram

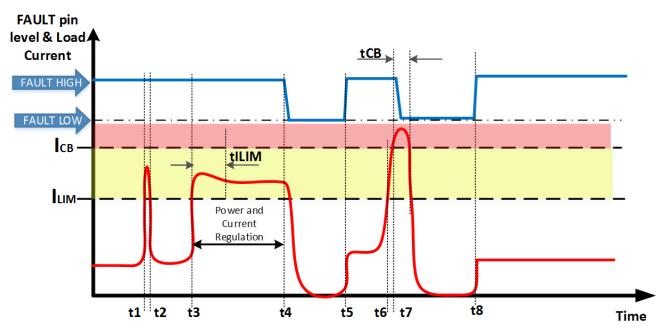

- t1: Current above  $I_{LIM}$ , FAULT counter started

- t2: Current went below I<sub>LIM</sub> before FAULT reached final count value. FAULT counter cleared, normal operation resumes

- t3: Current above I<sub>LIM</sub>, FAULT counter started. Device regulates current and power delivered to a load.

- t4: Device is shut down due to: A) FAULT timer ran out, OR B) Thermal shutdown, OR C) Current reached above ICB. FAULT pin is pulled Low.

- t5: FET temperature reduced by 40°C, device restarted manually or restart timer ran out (If configured to Auto-Restart)

- t6: Output short happened (or severe overload)

- t7: Current reached ICB level (output short is one reason). The device is immediately shut down within t<sub>CB</sub> time. FAULT pin pulled low

- t8: FET temperature reduced by 40°C, device restarted manually or restart timer ran out (If configured to Auto-Restart); normal operation resumed

Figure 3. Power and Current Limit Operation

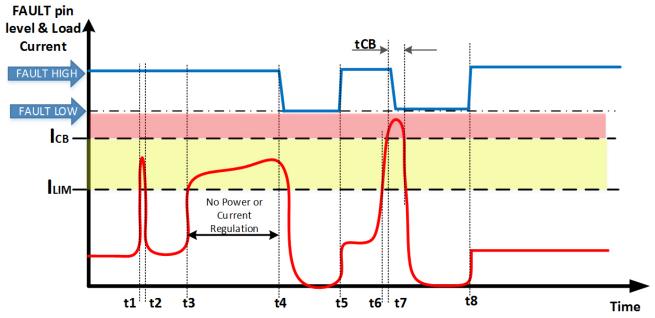

- t1: Current above I<sub>LIM</sub>, FAULT counter started

- t2: Current went below I<sub>LIM</sub> before tTRIP reached final count value. FAULT counter cleared, normal operation resumes

- t3: Current above I<sub>LIM</sub>, FAULT counter started. Device lets a load to draw as much current as it needs as long as it is below ICB and FET is not overheat

- t4: Device is shut down due to: A) FAULT timer ran out, OR B) Thermal shutdown, OR C) Current reached above ICB. FAULT pin is pulled Low.

- t5: FET temperature reduced by 40°C, device restarted manually or restart timer ran out (If configured to Auto-Restart)

- t6: Output short happened (or severe overload)

- t7: Current reached ICB level (output short is one reason). The device is immediately shut down within t<sub>CB</sub> time. FAULT pin pulled low

- t8: FET temperature reduced by 40°C, device restarted manually or restart timer ran out (If configured to Auto-Restart); normal operation resumed

Figure 4. Circuit Breaker Operation

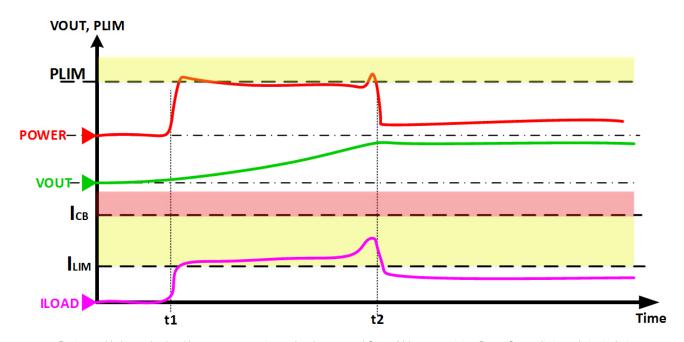

t1: Device enabled into a load and large output capacitance. Load current and Output Voltage start rising. Power/Current limit regulation in Action. FAULT timer is not started during this phase. If Current gets over ICB or if thermal limit of FET reached. The device is shutdown. t2: VOUT reached the target level. PG is pulled low. Load current settles down. External capacitor charged. At this point the device will be either in Power/Current limiting mode or in Circuit Breaker only mode; depending on the MODE pin selection.

Figure 5. Startup into Capacitive Load

## **APPLICATIONS INFORMATION**

## **Basic Operation**

This device is a self-protected, resettable, electronic fuse. It contains circuits to monitor the input voltage, output voltage, output current, dissipated power in the internal FET and die temperature. On application of the input voltage, the device will apply the input voltage to the load based on the restrictions of the controlling circuits and the state of the Enable pin. The output voltage ramp time is controlled by the internal power limit circuit which limits the power dissipated by the conduction FET to the level defined by user through PLIM pin. The device will remain on as long as load current does not exceed the circuit breaker level, enable pin is not driven high or the temperature does not exceed the 175°C limit that is programmed into the chip.

When configured for power and current limiting operation, upon the overcurrent condition the internal power and current limit circuit does not shut down the part but will reduce the conductivity of the FET to maintain a constant current at the externally set current limit level as well as limit the power dissipated by the internal FET to the externally set power limit.

When configured for circuit breaker operation the load current and the power dissipated by the internal FET is limited only during the startup; after startup, during normal operation upon the overcurrent event, the load is allowed to draw as much current as it needs as long as it does not exceed the circuit breaker level and internal FET temperature does not exceed 175°C. The device also employs the load current monitoring feature, configurable fault/restart/insertion delay timers, operating mode selection pin, auto-restart/latch behavior selection pin and an indicator pins for power good and fault status.

## Operating Mode Selection (MODE pin)

The device offers two overcurrent protection modes: Circuit Breaker operation mode and Power/Current limit operation mode. The desired operation mode is selected using the MODE pin. If MODE pin is grounded or left floating, the device is in power/current limit mode. If the MODE pin is tied to logic High, the device is in circuit breaker mode.

## **Power and Current Limit Mode**

The power and current limit operation mode is selected by connecting the MODE pin to ground or leaving it floating. If the operation mode needs to be changed the device needs to be restarted by removing the input voltage or re-cycling the enable pin.

The current limit circuit uses a reference and amplifier to control the conducted current in the internal FET of the device. The structure allows for a small fraction of the load current to be measured, which has the advantage of reducing the losses in the sense resistor. The measured load current is compared to the current limit set by the resistor at the ILIM pin and the set current limit is maintained by the device. The

measured load current is also multiplied by the voltage measured across the internal FET's drain and source and the product is compared to the power limit set by the resistor at PLIM pin, thus both the conducted current and power dissipated by the internal FET is limited by the device during an overcurrent event.

Once the load current exceeds the ILIM level the device enters the power and current limit mode and the FAULT timer starts counting. If the measured load current abruptly exceeds the circuit breaker level while the device is in power and current limit mode, for example due to the sudden output short to ground or if the internal FET temperature reaches 175°C the device will shut off the internal FET immediately. The device will shut down the FET also if the FAULT timer reached its value set by the user.

The current limit circuit has a limiting value which is programmed by connecting a resistor from the ILIM pin to GND. The power limit is set by the resistor connected between the PLIM pin and ground. It is recommended to have a 1% or better tolerance resistors for current and power limit programming. The diagram in Figure 3. shows a typical behavior of the device when configured for power and current limit mode.

#### **Circuit Breaker Mode**

The circuit breaker mode is selected by connecting the MODE pin to logic high. If the operation mode needs to be changed the device needs to be restarted by removing the input voltage or re-cycling the enable pin.

In this operating mode, the load current is measured by the internal sense circuitry. If the load current is exceeding the ILIM level set by a user the FAULT timer starts counting, however; neither the load current nor the power dissipated by the internal FET is limited. This mode avoids the voltage droop at the output during the overcurrent event and allows the load to draw as much current or power as it needs during the short overcurrent events, however; if the load current exceeds the circuit breaker level, if the FAULT timer runs out or if the internal FET temperature reaches 175°C the device will shut down the internal FET immediately.

The diagram in Figure 4. shows a typical behavior of the device when configured for circuit breaker operation mode.

#### **Startup into Capacitive Load**

During the startup, the power and current limit operation mode is active regardless of the MODE pin state. After the startup, when VOUT pin voltage is within 1V of VIN pin voltage and PGOOD pin is pulled low, the mode of operation is selected by the state of the MODE pin. This ensures that the device, even if configured for the latch mode operation, will successfully startup into large capacitive load without shutting down due to the internal FET overheat.

The output voltage ramp time when starting into capacitive load will depend on the power dissipated by the

internal FET and the capacitor energy as well as the current limit setting. The equation to compute the ramp time will be:

$$t_{Ramp} = (C_{LOAD} * V_{IN}^2)/(2 * P_{LIM}) + (C_{LOAD} * P_{LIM})/(2 * I_{LIM}^2)$$

Where tRamp is time required for output voltage to reach input voltage,  $C_{LOAD}$  is output capacitance,  $V_{IN}$  is input voltage and  $P_{LIM}$  is the limit for the power dissipated in the internal FET.

## Overvoltage and Undervoltage Lockout

The overvoltage and undervoltage lockout circuitry monitors the value of the input voltage not to exceed the threshold window set by the user. The threshold window for input voltage is set by connecting three resistors between input terminal, UVLO pin, OVLO pin and ground as shown in Figure 1. With internal threshold voltages for overvoltage and undervoltage  $-V_{\rm OV}$  and  $V_{\rm UV}$ , user can configure the overvoltage and undervoltage threshold windows using following equations:

$$V_{OVLO} = (V_{OV} * R3) / (R1 + R2 + R3)$$

$V_{UVLO} = (R2 + R3) * V_{UV} / (R1 + R2 + R3)$

#### Configurable Timers (TIMER1, TIMER2, TIMER3)

The NIS7080 employs configurable timers for fault timer, auto restart timer and insertion delay timer. The timers are configured externally by connecting the capacitor from TIMERx pin to ground. Each TIMERx pin has an internal current source which starts charging the capacitor connected to that pin once the timer is started. Once the voltage at the TIMERx pin charges up and reaches the internally programmed threshold value, the associated timer resets and generates an event. The larger capacitance connected to TIMERx pin will created larger time delays.

#### **Load Current Monitoring**

The current monitor "IMON" pin provides a small current proportional to the main device current which is passing through the internal FET. This pin should have a decoupling capacitor to filter out internal sampling noise. A resistor connected between the IMON pin and GND converts the IMON current into a GND referenced voltage. This pin can be floated if the feature is not required by application.

## **FAULT Indicator Pin and Fault Timer (TIMER1)**

The FAULT pin is an active-low open-drain pin indicating the host system about overcurrent shutdown. The FAULT pin has a fault timer TIMER1 associated with it which starts counting once the load current exceeds the I<sub>LIM</sub> level. If the timer runs out the internal FET will be turned off and FAULT pin will be pulled low by device indicating the fault condition.

The FAULT pin will be pulled low immediately if internal FET temperature reaches 175°C or if the load current exceeds circuit breaker  $I_{CB}$  level.

#### **Enable Pin**

The Enable pin is digital active low with internal pull down and provides a digital interface to control the output of the eFuse, without the need of any additional interface logic. When the EN pin is pulled low the device switches to its on state. When the EN pin is driven high, the eFuse output is turned off. All fault conditions will be cleared when the eFuse is reset through the Enable pin.

#### **Power Good Indicator Pin (PGOOD)**

The internal monitoring circuitry measures the output and input voltage. As soon as output voltage reaches the input voltage within 1 V threshold margin the PGOOD signal is pulled low indicating the host system about power good state. The pin can be left floating if not used, or pulled to logic high with  $10~\mathrm{k}\Omega$  resistor.

## Auto-Restart Delay (TIMER2)

When device is configured for auto-restart mode and the internal circuitry turned off the FET, the current source on TIMER2 pin starts charging the capacitor connected between TIMER2 pin and ground. Once the voltage on that pin reaches the internally programmed threshold value the device will attempt to turn the internal FET again. Adding larger capacitor to this pin increases the auto-restart time between faults.

## **Thermal Protection**

The NIS7080, NIV7080 includes an internal temperature sensing circuit that senses the temperature on the die of the power FET. If the temperature reaches 175°C, the device will shut down, and remove power from the load. If the device is configured in latching mode, output power can be restored by either recycling the input power or toggling the enable pin. An auto-retry mode configured device mode will automatically try to restore output power on its own after the TIMER2 runs out. The thermal limit has been set high intentionally, to increase the trip time during high power transient events. It is not recommended to operate this device above 125°C for extended periods of time.

#### Hot-Plug Insertion Delay (TIMER3)

The device features a hot-plug insertion delay which allows a delay between application of input voltage and time when the voltage on the VOUT pin starts rising. This feature is useful in situations where it is desirable to turn on the output after the input transient of hot-plug settled down. User can control the insertion delay by connecting the capacitor to TIMER3 pin, larger capacitor will increase the delay. Once the voltage at the VIN pin reaches 6 V, the power on reset is active and the TIMER3 current source starts charging the external capacitor; once the capacitor is charged to the internally programmed threshold value the

TIMER3 timer runs out and the internal FET is turned on to bring VOUT pin to the voltage level of VIN.

## Latch and Auto-Retry Pin Configuration

This device allows user to configure the latch or auto-retry operation using the RESTART pin. If the

RESTART pin is grounded or left floating, the part is configured in auto-restart mode. If the pin is connected to logic High, the part is configured for Latch mode operation. Once the state of the pin is changed the eFuse needs to be restarted either by cycling the input power or toggling the Enable pin.

## **ORDERING INFORMATION**

| Device  | Marking | Package         | Shipping †        |

|---------|---------|-----------------|-------------------|

| NIS7080 | TBD     | WDFNW12, 3x3 mm | TBD / Tape & Reel |

| NIV7080 | TBD     | (Pb – Free)     |                   |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

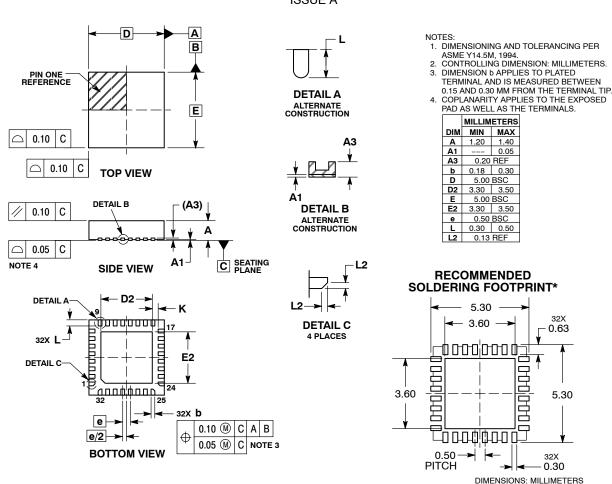

## PACKAGE DIMENSIONS

## LQFN32 5x5, 0.5P CASE 487AA **ISSUE A**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative