# Three-Output PTIC Control IC

## **TCC-303**

#### Introduction

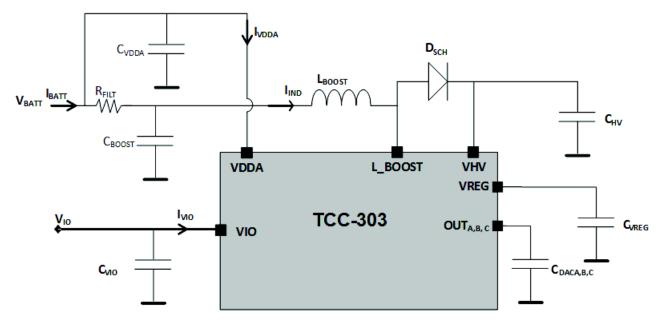

TCC-303 is a three-output high-voltage digital to analog control IC specifically designed to control and bias ON Semiconductor's Passive Tunable Integrated Circuits (PTICs).

These tunable capacitor control circuits are intended for use in mobile phones and dedicated RF tuning applications. The implementation of ON Semiconductor's tunable circuits in mobile phones enables significant improvement in terms of antenna radiated performance.

The tunable capacitors are controlled through a bias voltage ranging from 1 V to 24 V. The TCC-303 high-voltage PTIC control IC has been specifically designed to cover this need, providing three independent high-voltage outputs that control up to three different tunable PTICs in parallel. The device is fully controlled through a MIPI RFFE digital interface.

## **Key Features**

- Controls ON Semiconductor's PTIC Tunable Capacitors

- Compliant with Timing Needs of Cellular and Other Wireless System Requirements

- 28 V Integrated Boost Converter with Three 24 V Programmable DAC Outputs

- Low Power Consumption

- MIPI RFFE Interfaces (1.8 V)

- Available in WLCSP (RDL ball arrays)

- Compliant with MIPI 26 MHz Read-Back

- This is a Pb-Free Device

## **Typical Applications**

- Multi-band, Multi-standard, Advanced and Simple Mobile Phones

- Tunable Antenna Matching Networks

- Compatible with Closed–loop and Open–loop Antenna Tuner Applications

## ON Semiconductor®

www.onsemi.com

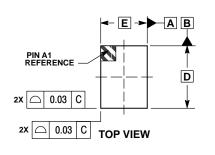

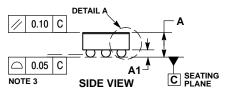

WLCSP12 CASE 567MW

## **MARKING DIAGRAM**

T33x= Specific Device Code

c = a or b

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

■ = Pb–Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 30 of this data sheet

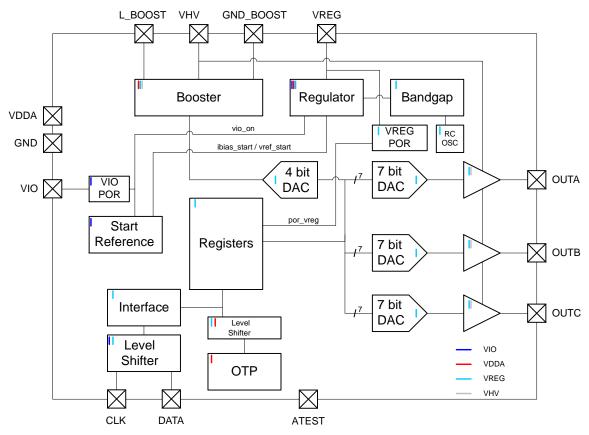

Figure 1. Control IC Functional Block Diagram

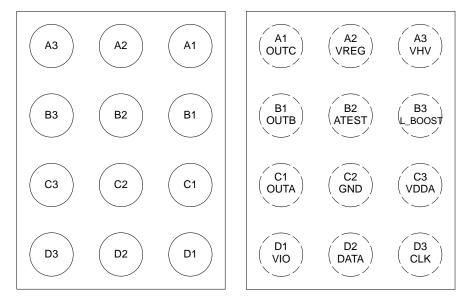

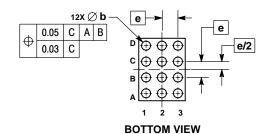

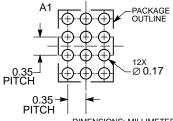

Figure 2. RDL Padout, Bump Side View (left), PCB footprint (right), with RDL Bump Assignment

## **RDL Pin Out**

**Table 1. PAD DESCRIPTIONS**

| RDL | Name    | Туре      | Description                                 |

|-----|---------|-----------|---------------------------------------------|

| A1  | OUTC    | АОН       | High Voltage Output C                       |

| A2  | VREG    | AO        | Regulator Output                            |

| A3  | VHV     | AOH / AIH | Boost High Voltage can be Forced Externally |

| B1  | OUTB    | АОН       | High Voltage Output B                       |

| B2  | ATEST   | AO        | Analog Test Out (Note 1)                    |

| В3  | L_BOOST | АОН       | Boost Inductor                              |

| C1  | OUTA    | AOH       | High Voltage Output A                       |

| C2  | GND     | Р         | Ground                                      |

| C3  | VDDA    | Р         | Analog Supply                               |

| D1  | VIO     | Р         | Digital IO Supply                           |

| D2  | DATA    | DIO       | MIPI RFFE Digital IO                        |

| D3  | CLK     | DI        | MIPI RFFE Clock                             |

Legend: Pad Types

AIH= High Voltage Analog Input

AO= Analog Output

AOH= High Voltage Analog Output

DI= Digital Input

DIO= Digital Input/Output (IO)

P= Power

## **ELECTRICAL PERFORMANCE SPECIFICATIONS**

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Symbol                  | Parameter                                        | Rating            | Unit |

|-------------------------|--------------------------------------------------|-------------------|------|

| VDDA                    | Analog Supply Voltage                            | -0.3 to +5.5      | V    |

| VIO                     | IO Reference Supply Voltage                      | -0.3 to +2.5      | V    |

| V <sub>I/O</sub>        | Input Voltage Logic Lines (DATA, CLK)            | -0.3 to VIO + 0.3 | V    |

| $V_{HVH}$               | VHV Maximum Voltage                              | -0.3 to 30        | V    |

| V <sub>ESD (HBM)</sub>  | Human Body Model, JESD22-A114, All I/O           | 2,000             | V    |

| V <sub>ESD (MM)</sub>   | Machine Model, JESD22-A115                       | 200               | V    |

| T <sub>STG</sub>        | Storage Temperature                              | -55 to +150       | °C   |

| T <sub>AMB_OP_MAX</sub> | Max Operating Ambient Temperature without Damage | +110              | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

<sup>1.</sup> To be grounded in normal operation.

**Table 3. RECOMENDED OPERATING CONDITIONS**

| Symbol              | Parameter                      | Min  | Тур | Max  | Unit |

|---------------------|--------------------------------|------|-----|------|------|

| T <sub>AMB_OP</sub> | Operating Ambient Temperature  | -30  | -   | +85  | °C   |

| $T_{J_{OP}}$        | Operating Junction Temperature | -30  | -   | +125 | °C   |

| VDDA                | Analog Supply Voltage          | 2.3  | -   | 5.5  | V    |

| VIO                 | IO Reference Supply Voltage    | 1.62 | -   | 1.98 | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

**Table 4. DC CHARACTERISTICS** ( $T_A$  = -30 to +85°C;  $V_{OUTX}$  = 15 V for each output; 2.3 V<VDDA< 5.5 V;  $V_{IO}$  = 1.8 V;  $R_{LOAD}$  = equivalent series load of 5.6 kΩ and 2.7 nF;  $C_{HV}$  = 22 nF;  $L_{BOOST}$  = 15 μH; unless otherwise specified)

| Symbol                    | Parameter                                                                                                                                           | Min        | Тур | Max  | Unit | Comment                                       |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|------|------|-----------------------------------------------|--|

| SHUTDOWN M                | ODE                                                                                                                                                 | •          | •   | •    |      |                                               |  |

| I <sub>VDDA</sub>         | VDDA Supply Current                                                                                                                                 | _          | _   | 1.5  | μΑ   | VIO Supply is Low                             |  |

| I <sub>L_BOOST</sub>      | L_BOOST Leakage                                                                                                                                     | -          | -   | 1.5  |      |                                               |  |

| I <sub>BATT</sub>         | Battery Current                                                                                                                                     | -          | -   | 2.5  |      |                                               |  |

| I <sub>VIO</sub>          | VIO Supply Current                                                                                                                                  | -1         | -   | 1    |      |                                               |  |

| I <sub>CLK</sub>          | CLK Leakage                                                                                                                                         | -1         | -   | 1    |      |                                               |  |

| I <sub>DATA</sub>         | DATA Leakage                                                                                                                                        | <b>–</b> 1 | -   | 1    |      |                                               |  |

| ACTIVE MODE               |                                                                                                                                                     |            |     |      |      |                                               |  |

| I <sub>BATT</sub>         | Average battery current, 3 outputs actively switching 16 V for 1205 $\mu s$ to 2 V for 1705 $\mu s$ to 8 V for 1705 $\mu s$                         | -          | 980 | 1290 | μΑ   | At VHV = 20 V<br>VDDA = 3.3 V                 |  |

| I <sub>BATT_SS0</sub>     | Average battery current, 3 outputs @ 0 V steady state                                                                                               | _          | 590 | 830  |      | At VHV = 20 V<br>VDDA = 3.3 V                 |  |

| I <sub>BAT_SS2</sub>      | Average battery current, 3 outputs @ 2 V steady state                                                                                               | _          | 610 | 860  | μΑ   | At VHV = 20 V<br>VDDA = 3.3 V                 |  |

| I <sub>BATT_SS16</sub>    | Average battery current, 3 outputs @ 16 V steady state                                                                                              | _          | 780 | 1020 |      | At VHV = 20 V<br>VDDA = 3.3 V                 |  |

| I <sub>L_BOOST</sub>      | Average inductor current, 3 outputs actively switching 16 V for 1205 μs to 2 V for 1705 μs to 8 V for 1705 μs and 3 outputs are @ 16 V steady state | -          | 730 | 1000 |      | At VHV = 20 V<br>VDDA = 3.3 V                 |  |

| I <sub>L_BOOST_SS0</sub>  | Average inductor current, 3 outputs @ 0 V steady state                                                                                              | -          | 350 | 550  |      | At VHV = 20 V<br>VDDA = 3.3 V                 |  |

| I <sub>L_BOOST_SS2</sub>  | Average inductor current, 3 outputs @ 2 V steady state                                                                                              | _          | 380 | 570  |      | At VHV = 20 V<br>VDDA = 3.3 V                 |  |

| I <sub>L_BOOST_SS16</sub> | Average inductor current, 3 outputs @ 16 V steady state                                                                                             | _          | 550 | 750  |      | At VHV = 20 V<br>VDDA = 3.3 V                 |  |

| I <sub>VIO_INACT</sub>    | VIO average inactive current                                                                                                                        | -          | -   | 3    |      | VIO is high, no bus activity                  |  |

| I <sub>VIO_ACTIVE</sub>   | VIO average active current                                                                                                                          | _          | -   | 250  |      | VIO = 1.8 V, master sending<br>data at 26 MHz |  |

| V <sub>VREG</sub>         |                                                                                                                                                     | 1.7        | _   | 1.9  | V    | No external load allowed                      |  |

Table 4. DC CHARACTERISTICS ( $T_A = -30$  to +85°C;  $V_{OUTX} = 15$  V for each output; 2.3 V<VDDA< 5.5 V;  $V_{IO} = 1.8$  V;  $R_{LOAD} = 0.5$  equivalent series load of 5.6 kΩ and 2.7 nF;  $C_{HV} = 22$  nF;  $C_{HV} = 1.5$  μH; unless otherwise specified)

| Symbol               | Parameter           | Min | Тур | Max | Unit | Comment                                  |

|----------------------|---------------------|-----|-----|-----|------|------------------------------------------|

| LOW POWER I          | MODE                |     |     |     |      |                                          |

| $I_{VDDA}$           | VDDA Supply Current | _   | _   | 8   | μΑ   |                                          |

| I <sub>L_BOOST</sub> | L_BOOST Leakage     | _   | -   | 6   |      |                                          |

| I <sub>BATT</sub>    | Battery Current     | -   | -   | 14  |      | I <sub>VDDA</sub> + I <sub>L_BOOST</sub> |

| I <sub>VIO</sub>     | VIO Supply Current  | _   | _   | 3   |      | No bus activity                          |

| $V_{VREG}$           |                     | 1.6 | -   | 1.9 | V    | No external load allowed                 |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

## **Table 5. BOOST CONVERTER CHARACTERISTICS**

(VDDA from 2.3 V to 5.5 V;  $V_{IO}$  = 1.8 V;  $T_{A}$  = -30 to +85°C;  $C_{HV}$  = 22 nF;  $L_{BOOST}$  = 15  $\mu H$ ; unless otherwise specified)

| Symbol                     | Parameter                                                     | Conditions  | Min | Тур | Max | Unit |

|----------------------------|---------------------------------------------------------------|-------------|-----|-----|-----|------|

| VHV_min                    | Minimum programmable output voltage (average), DAC Boost = 0h | Active mode | -   | 13  | -   | V    |

| VHV_max                    | Maximum programmable output voltage (average), DAC Boost = Fh | Active mode | -   | 28  | -   |      |

| Resolution                 | Boost voltage resolution                                      | 4-bit DAC   | -   | 1   | _   |      |

| I <sub>L_BOOST_LIMIT</sub> | Inductor current limit                                        |             | -   | 200 | _   | mA   |

## Table 6. ANALOG OUTPUTS (OUT A, OUT B, OUT C)

(VDDA from 2.3 V to 5.5 V;  $V_{IO}$  = 1.8 V;  $V_{HV}$  = 26 V;  $T_A$  = -30 to +85°C;  $R_{load}$  =  $\infty$  unless otherwise specified)

| Parameter           | Description                                       | Min  | Тур | Max  | Unit              | Comment                                                                                                                   |

|---------------------|---------------------------------------------------|------|-----|------|-------------------|---------------------------------------------------------------------------------------------------------------------------|

| SHUTDOWN            | MODE                                              |      |     |      |                   |                                                                                                                           |

| Z <sub>OUT</sub>    | OUT A, OUT B, OUT C output impedance              | 7    | _   | -    | МΩ                | DAC disabled                                                                                                              |

| ACTIVE MOI          | DE                                                |      |     |      |                   |                                                                                                                           |

| V <sub>OH</sub>     | Maximum output voltage                            | _    | 24  | -    | V                 | DAC A, B, C = 7Fh,<br>DAC Boost = Fh, I <sub>OH</sub> < 10 μA                                                             |

| V <sub>OL</sub>     | Minimum output voltage                            | -    | _   | 1    | V                 | DAC A, B C = 01h, DAC Boost = 0h to Fh, $I_{OH}$ < 10 $\mu$ A                                                             |

| Slew Rate           |                                                   | -    | 3   | 10   | μs                | 2 V to 20 V step, measured at $V_{OUT}$ = 15.2 V, $R_{LOAD}$ = equivalent series load of 5.6 kΩ and 2.7 nF, Turbo enabled |

| R <sub>PD</sub>     | OUT A, OUT B, OUT C set in pull-<br>down mode     | -    | _   | 1000 | Ω                 | DAC A, B C = 00h, DAC Boost = 0h to Fh, selected output(s) is disabled                                                    |

| Resolution          | Voltage resolution (1-bit)                        | _    | 189 | _    | mV                | (1 LSB = 1-bit)                                                                                                           |

| V <sub>OFFSET</sub> | Zero scale, least squared best fit                | -1   | _   | +1   | LSB               |                                                                                                                           |

| Gain Error          |                                                   | -3.0 | _   | +3.0 | %V <sub>OUT</sub> | 1 V to 24 V with 26 V VHV                                                                                                 |

| DNL                 | Differential non-linearity least squared best fit | -0.9 | -   | +0.9 | LSB               | 1 V to 24 V with 26 V VHV                                                                                                 |

| INL                 | Integral non-linearity least squared best fit     | -1   | _   | +1   | LSB               | 1 V to 24 V with 26 V VHV                                                                                                 |

| I <sub>SC</sub>     | Over current protection                           | -    | 5   | 65   | mA                | Any DAC output shorted to ground                                                                                          |

| V <sub>RIPPLE</sub> | Output ripple with all outputs at steady state    | -    | -   | 40   | mV RMS            | 1 V to 24 V with 26 V VHV                                                                                                 |

#### THEORY OF OPERATION

#### Overview

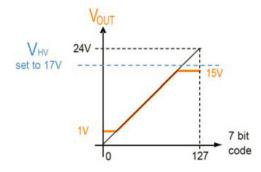

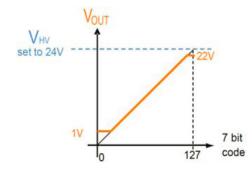

The control IC outputs are directly controlled by programming the three DACs (DAC A, DAC B, DAC C) through the digital interface.

The DAC stages are driven from a reference voltage, generating an analog output voltage driving a high-voltage amplifier supplied from the boost converter (see Figure 1 – Control IC Functional Block Diagram).

The control IC output voltages are scaled from 0 V to 24 V, with 127 steps of 189 mV. The nominal control IC output can be approximated to 189 mV x (DAC value).

For performance optimization the boost output voltage (VHV) can be programmed to levels between 13 V and 28 V via the DAC\_boost register (4 bits with 1 V steps). The startup default level for the boosted voltage is VHV = 24 V.

For proper operation and to avoid saturation of the output devices and noise issues, it is recommended to operate the boosted VHV voltage at least 2 V (>4 V [6 V recommended] if using Turbo–Charge Mode) above the highest programmed  $V_{\rm OUT}$  voltage of any of the three outputs.

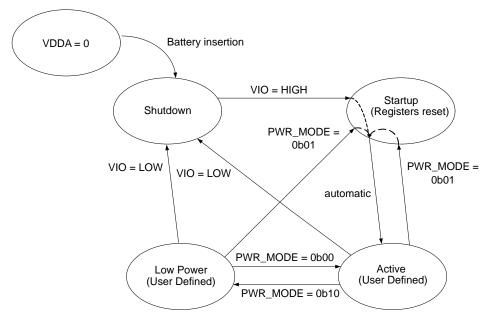

## **Operating Modes**

The following operating modes are available:

1. **Shutdown Mode:** All circuit blocks are off, the DAC outputs are disabled and placed in high Z state and current consumption is limited to minimal leakage current. The shutdown mode is entered upon initial application of VDDA or upon VIO being placed in the low state. The contents of the registers are not maintained in shutdown mode.

- 2. Startup Mode: Startup is only a transitory mode. Startup mode is entered upon a VIO high state. In startup mode all registers are reset to their default states, the digital interface is functional, the boost converter is activated, outputs OUT A, OUT B, OUT C are disabled and the DAC outputs are placed in a high Z state. Control software can request a full hardware and register reset of the TCC-303 by sending an appropriate PWR\_MODE command to direct the chip from either the active mode or the low power mode to the startup mode. From the startup mode the device automatically proceeds to the active mode.

- 3. Active Mode: All blocks of the TCC-303 are activated and the DAC outputs are fully controlled through the digital interface, DACs remain off until enabled. The DAC settings can be dynamically modified and the HV outputs will be adjusted according to the specified timing diagrams. Each DAC can be individually controlled and/or switched off according to application requirements. Active mode is automatically entered from the startup mode. Active mode can also be entered from the low power mode under control software command.

- 4. Low Power Mode: In low power mode the serial interface stays enabled, the DAC outputs are disabled and are placed in a high Z state and the boost voltage circuit is disabled. Control software can request to enter the low power mode from the active mode by sending an appropriate PWR\_MODE command. The contents of all registers are maintained in the low power mode.

Figure 3. Modes of Operation

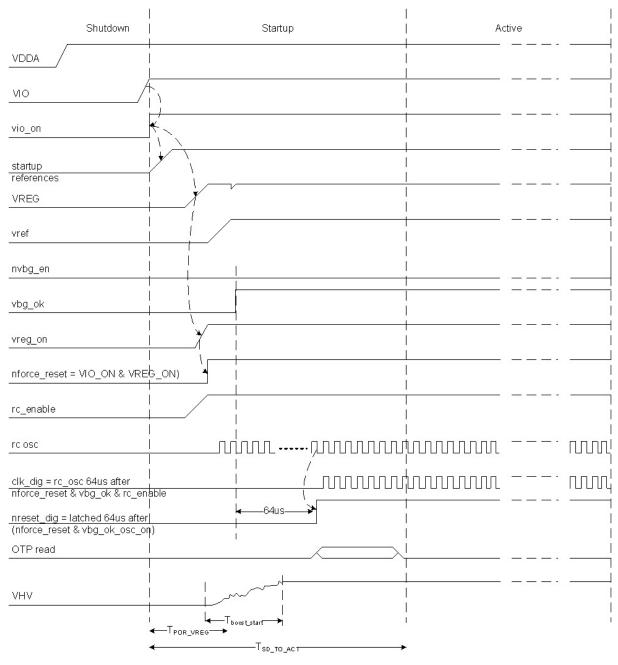

#### VDDA Power-On Reset (POR)

Upon application of VDDA, TCC-303 will be in shutdown mode. All circuit blocks are off and the chip draws only minimal leakage current.

#### **VIO Power-On Reset and Startup Conditions**

A high level on VIO places the chip in startup mode which provides a POR to TCC–303. POR resets all registers to their default settings as described in Register Content Details. VIO POR also resets the serial interface circuitry. POR is not a brown—out detector and VIO needs to be brought back to a low level to enable the POR to trigger again.

Table 7. VIO POWER-ON RESET AND STARTUP

| Register   | Default State for VIO POR | Comment                                                                    |

|------------|---------------------------|----------------------------------------------------------------------------|

| DAC Boost  | [1011]                    | VHV = 24 V                                                                 |

| Power Mode | [01]>[00]                 | Transitions from shutdown to startup and then automatically to active mode |

| DAC Enable | [000]                     | V <sub>OUT</sub> A, B, C Disabled                                          |

| DAC A      |                           | Output in High-Z Mode                                                      |

| DAC B      |                           | Output in High–Z Mode                                                      |

| DAC C      |                           | Output in High–Z Mode                                                      |

#### **VIO Shutdown**

A low level at any time on VIO places the chip in shutdown mode in which all circuit blocks are off. The contents of the registers are not maintained in shutdown mode.

Table 8. VIO THRESHOLDS (VDDA from 2.3 V to 5.5 V; T<sub>A</sub> = -30 to +85°C unless otherwise specified)

| Parameter | Description       | Min | Тур | Тур Мах |   | Comments                                                                                           |

|-----------|-------------------|-----|-----|---------|---|----------------------------------------------------------------------------------------------------|

| VIORST    | VIO Low Threshold | -   | -   | 0.2     | V | When VIO is lowered below this threshold level the chip is reset and placed into the shutdown mode |

#### **Power Supply Sequencing**

The VDDA input is typically directly supplied from the battery and thus is the first on. After VDDA is applied and before VIO is applied to the chip, all circuits are in the shutdown mode and draw minimum leakage currents. Upon application of VIO, the chip automatically starts up using default settings and is placed in the active state waiting for a command via the serial interface.

**Table 9. TIMING** (VDDA from 2.3 V to 5.5 V;  $V_{IO}$  = 1.8 V;  $T_A$  = -30 to +85°C; OUT A, OUT B, OUT C; CHV = 47 nF;  $L_{BOOST}$  = 15  $\mu$ H; VHV = 20 V; Turbo–Charge mode off unless otherwise specified)

| Parameter                | Description                                                                                                                                                                                 | Min | Тур | Max | Unit | Comments                                                                                                     |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--------------------------------------------------------------------------------------------------------------|

| T <sub>POR_VREG</sub>    | Internal bias settling time from shutdown to active mode                                                                                                                                    | -   | 50  | 120 | μs   | For info only                                                                                                |

| T <sub>BOOST_START</sub> | Time to charge CHV @ 95% of set VHV                                                                                                                                                         | -   | 130 | -   | μs   | For info only                                                                                                |

| T <sub>SD_TO_ACT</sub>   | Startup time from shutdown to active mode                                                                                                                                                   | -   | 180 | 300 | μs   |                                                                                                              |

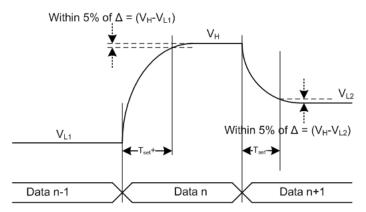

| T <sub>SET+</sub>        | Timing for a 2 V to 16 V transition, measured when voltage reaches within 5% of target voltage, measured between the R (5.6 k $\Omega$ ) and C (2.7 nF) of an equivalent PTIC series load.  | -   | 50  | 60  | μs   | Voltage settling time connected on V <sub>OUT</sub> A, B, C                                                  |

| T <sub>SET-</sub>        | Timing for a 16 V to 2 V transition, measured when voltage reaches within 5% of target voltage, measured between the R (5. 6 k $\Omega$ ) and C (2.7 nF) of an equivalent PTIC series load. | -   | 50  | 60  | μs   | Effective PTIC<br>tuning voltage<br>settling time,<br>measured between<br>an equivalent R and<br>C PTIC load |

| T <sub>SET+</sub>        | Output A, B, C positive settling time with Turbo                                                                                                                                            | _   | 35  | _   | μs   | Voltage settling time connected on V <sub>OUT</sub> A, B, C                                                  |

| T <sub>SET</sub> -       | Output A, B, C negative settling time with Turbo                                                                                                                                            | -   | 35  | -   | μs   | Voltage settling time connected on V <sub>OUT</sub> A, B, C                                                  |

Figure 4. Output Settling Diagram

Figure 5. Startup Timing Diagram

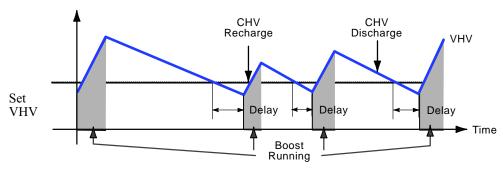

#### **Boost Control**

TCC-303 integrates an asynchronous current control boost converter. It operates in a discontinuous mode and features spread-spectrum circuitry for Electro-Magnetic Interference (EMI) reduction. The average boost clock is 2 MHz and the clock is spread between 0.8 MHz and 4 MHz.

## **Boost Output Voltage (VHV) Control Principle**

The asynchronous control starts the boost converter as soon as the VHV voltage drops below the reference set by the 4-bit DAC and stops the boost converter when the VHV voltage rises above the reference again.

Due to the slow response time of the control loop, the VHV voltage may drop below the set voltage before the control loop compensates for it. In the same manner, VHV can rise higher than the set value. This effect may reduce the maximum output voltage available. Please refer to Figure 6 below.

The asynchronous control reduces switching losses and improves the output (VHV) regulation of the DC/DC converter under light load, particularly in the situation where TCC–303 only maintains the output voltages to fixed values.

Figure 6. VHV Voltage Waveform

## High Impedance (High Z) Feature

In shutdown mode the OUT pins are set to a high impedance mode (high Z). Following is the principle of operation for the control IC:

1. The DAC output voltage V<sub>OUT</sub> is defined by:

$$V_{OUT} = \frac{DAC \text{ code}}{127} \times 24 \text{ V}$$

(eq. 1)

- 2. The voltage VHV defines the maximum supply voltage of the DAC supply output regulator and is set by a 4-bit control.

- 3. The maximum DAC DC output voltage  $V_{OUT}$  is limited to (VHV -2 V). DAC can achieve higher output voltages, but timing is not maintained for swings above VHV -2 V.

- The minimum output DAC voltage V<sub>OUT</sub> is 1.0 V max.

Figure 7. DAC Output Range Example A

Figure 8. DAC Output Range Example B

#### **Digital Interface**

The control IC is fully controlled through a digital interface (DATA, CLK). The digital interface is described in the following sections of this document.

## Turbo-Charge Mode

The TCC-303 control IC has a Turbo-Charge Mode that significantly shortens the system settling time when changing programming voltages.

In Turbo-Charge Mode the DAC output target voltage is temporarily set to either a delta voltage above or a delta voltage below the actual desired target. The delta voltage is 4 volts.

After the DAC value message is received, the delta voltage is calculated by hardware, and is applied in digital format to the input of the DAC, right after trigger is received. The period for which the delta voltage is maintained to the input of the DAC, the Turbo time, is calculated based on following considerations:

- DAC\_TIMER\_A[4:0] / DAC\_TIMER\_B[4:0] / DAC\_TIMER\_C[4:0]: These are the DAC timer configuration fields. For the turbo mode, they define the turbo latency value, when the target+delta voltage is active. If each DAC is updated over and over with the same turbo delay value, these fields do NOT need to be updated at each DAC update. The register has to hold a non-zero value for a Turbo update.

- DAC\_TC2X\_A / DAC\_TC2X\_B / DAC\_TC2X\_C: If these bits are set, the timer loads DAC\_TIMER\_X \* 2 value as opposed to DAC\_TIMER\_X value. This allows a turbo operation delay up to 124 μs.

- DAC\_TCM\_A [1:0] / DAC\_TCM\_B [1:0] /

DAC\_TCM\_C [1:0] : If the Turbo direction is down

and the Turbo target is below 4 V, these multiplication

factors are utilized to extend the turbo delay. Further

formula provided below.

- GL\_A / GL\_B / GL\_C: These are the DAC update

mode configuration fields, which need to be set to turbo

mode at the new DAC value update and prior to the SW

trigger (optional). These bits are part of the DAC value

register. If they are set to 0, the DAC is in Turbo Mode,

as long as the corresponding DAC\_TIMER register is

non-zero. A DAC\_TIMER =0 means an immediate

update independent of the GL\_A/B/C value.

- The Turbo UP or DOWN voltage is decided based on the comparison of the new DAC value and the old DAC value. If the new value is greater, the turbo direction will be UP. Otherwise it will be down. In case of both DAC values being equal, there is no DAC update applied. After a turbo request is received, any trigger will start the turbo output transition. The trigger could be:

- A MIPI-RFFE software trigger controlled by RFFE\_PM\_TRIG register

- An internal generated trigger after the corresponding DAC value is updated, as described in section DAC Update Triggering.

The DAC values send by digital turbo-charge logic to DACs are:

- During turbo-charge delay duration the value applied is "DAC\_new ±4 V" (the polarity of the 4 V turbo will depend on if turbo charge is up or down)

- If DAC\_new > DAC old, and DAC\_new+4 V is exceeding the word length of the DAC, it is saturated to max value possible.

- If DAC\_new < DAC\_old, and DAC\_new-4 V is a negative number, a DAC value of 0 is applied.

- After turbo-charge delay duration the value applied is the actual DAC\_new.

Table 10. DAC\_TIMER\_A/B/C UNIT DELAYS

| DAC_TIMER_A/B/C [4:0] |       |       |       |       |                                                                          |

|-----------------------|-------|-------|-------|-------|--------------------------------------------------------------------------|

| Bit 4                 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Turbo delay time in Turbo Mode or glide step duration in Glide Mode [μs] |

| 0                     | 0     | 0     | 0     | 0     | Immediate Update                                                         |

| 0                     | 0     | 0     | 0     | 1     | 2                                                                        |

| 0                     | 0     | 0     | 1     | 0     | 4                                                                        |

| 0                     | 0     | 0     | 1     | 1     | 6                                                                        |

| 0                     | 0     | 1     | 0     | 0     | 8                                                                        |

| 0                     | 0     | 1     | 0     | 1     | 10                                                                       |

| 0                     | 0     | 1     | 1     | 0     | 12                                                                       |

| 0                     | 0     | 1     | 1     | 1     | 14                                                                       |

| 0                     | 1     | 0     | 0     | 0     | 16                                                                       |

| 0                     | 1     | 0     | 0     | 1     | 18                                                                       |

| 0                     | 1     | 0     | 1     | 0     | 20                                                                       |

| 0                     | 1     | 0     | 1     | 1     | 22                                                                       |

| 0                     | 1     | 1     | 0     | 0     | 24                                                                       |

| 0                     | 1     | 1     | 0     | 1     | 26                                                                       |

| 0                     | 1     | 1     | 1     | 0     | 28                                                                       |

| 0                     | 1     | 1     | 1     | 1     | 30                                                                       |

| 1                     | 0     | 0     | 0     | 0     | 32                                                                       |

| 1                     | 0     | 0     | 0     | 1     | 34                                                                       |

| 1                     | 0     | 0     | 1     | 0     | 36                                                                       |

| 1                     | 0     | 0     | 1     | 1     | 38                                                                       |

| 1                     | 0     | 1     | 0     | 0     | 40                                                                       |

| 1                     | 0     | 1     | 0     | 1     | 42                                                                       |

| 1                     | 0     | 1     | 1     | 0     | 44                                                                       |

| 1                     | 0     | 1     | 1     | 1     | 46                                                                       |

| 1                     | 1     | 0     | 0     | 0     | 48                                                                       |

| 1                     | 1     | 0     | 0     | 1     | 50                                                                       |

| 1                     | 1     | 0     | 1     | 0     | 52                                                                       |

| 1                     | 1     | 0     | 1     | 1     | 54                                                                       |

| 1                     | 1     | 1     | 0     | 0     | 56                                                                       |

| 1                     | 1     | 1     | 0     | 1     | 58                                                                       |

| 1                     | 1     | 1     | 1     | 0     | 60                                                                       |

| 1                     | 1     | 1     | 1     | 1     | 62                                                                       |

The value of turbo delay time is deducted based on the hardware comparison of new DAC value in respect to old DAC value, as follows. In this calculation the decimal "21" value corresponds to 4 V DAC drive. As the DAC new value is closer to 0 V in a down Turbo, the delay time increases more.

If DAC new < DAC old, and DAC new < 21, then  $T_{DOWN}$  = DAC\_TIMER\_A/B/C << DAC\_TC2X\_A/B/C + DAC\_TCM\_A/B/C \* (21 – DAC new)

$$\begin{split} &\text{If DAC new} < \text{DAC old, and DAC new} > 21, \text{ then } T_{DOWN} \\ &= \text{DAC\_TIMER\_A/B/C} << \text{DAC\_TC2X\_A/B/C} \\ &\text{If DAC new} < \text{DAC old, and DAC new} = 21, \text{ then } T_{DOWN} \\ &= \text{DAC\_TIMER\_A/B/C} << \text{DAC\_TC2X\_A/B/C} \end{split}$$

Table 11. TURBO-CHARGE MULTIPLICATION FACTOR

| TCM [1:0]    | Multiplication Factor |

|--------------|-----------------------|

| 00 (default) | 4                     |

| 01           | 3                     |

| 10           | 2                     |

| 11           | 1                     |

#### Transition from Turbo to Turbo or Immediate Update

In the event a new trigger is received during a turbo transition, the ongoing turbo operation is halted and the new DAC value is applied immediately. There won't be any Turbo and the hi\_slew is kept low.

#### **Transition from Turbo to Glide**

In the event that a new glide transition is triggered during a turbo event, then the turbo process is stopped and the current target value is set at the DAC output immediately without hi\_slew. The new glide is started from this value.

## DAC disable during Turbo (including active to low power mode transition)

If the DAC, which is in Turbo is disabled, the target DAC value is immediately applied without hi\_slew. The DAC does not continue with the Turbo when it is re-enabled.

#### **Glide Mode**

The TCC-303 control IC has a Glide Mode that significantly extends the system transition time when changing programming voltages.

Glide Mode is controlled by the following registers:

- DAC\_TIMER\_A[4:0] / DAC\_TIMER\_B[4:0] / DAC\_TIMER\_C[4:0]: These are the DAC timer configuration fields. For the glide mode they define the step duration. If each DAC is updated over and over with the same glide step, these fields do NOT need to be updated at each DAC update. The register has to hold a non-zero value for a Glide update.

- GL\_A / GL\_B / GL\_C: These are the DAC update

mode configuration fields, which need to be set to glide

mode at the new DAC value update and prior to the SW

trigger (optional). These bits are part of the DAC value

register. If they are set to 1, the DAC is in glide mode,

as long as the corresponding DAC\_TIMER register is

non-zero. A DAC\_TIMER =0 means an immediate

update independent of the GL\_A/B/C value.

After a Glide request is received, any trigger will start the Glide output transition.

The trigger could be:

- a MIPI-RFFE software trigger controlled by RFFE\_PM\_TRIG register

- an internal generated trigger after the corresponding DAC value is updated, as described in a later section.

Immediately after the trigger, the DAC\_old value is loaded in the MSB's of the upper byte of a 15 bit accumulator, while the lower byte of accumulator is being reset to 0x00.

At the same time a count step is calculated:

GLIDE\_STEP[6:0] = DAC\_new - DAC\_old; if DAC\_new > DAC\_old

GLIDE\_STEP[6:0] = DAC\_old - DAC\_new; if DAC new < DAC old

$ACCUMULATOR[14:0] = DAC_old, 0x00;$

NOTE: Glide is disabled if DAC\_new = DAC\_old.

From the moment the trigger is received, a tick is generated internally, with a frequency controlled by the DAC\_TIMER\_A/B/C registers. Each DAC has its own tick generator running independently of the other DAC. Each time a trigger is received for a DAC, the setting of the DAC\_TIMER\_A/B/C register is sampled in a counter dedicated to that DAC. Any update of the DAC\_TIMER\_A/B/C register after trigger is received will be ignored until the next trigger is received

Each time a tick is generated, the content of the accumulator is either incremented or decremented, depending whether DAC\_new is either bigger or smaller than DAC old.

ACCUMULATOR[14:0] = ACCUMULATOR[14:0] + GLIDE\_STEP; if DAC\_new > DAC\_old

ACCUMULATOR[14:0] = ACCUMULATOR[14:0] - GLIDE STEP; if DAC new < DAC old

Each time a tick is generated, the output of the DAC[6:0] is updated with the value of ACCUMULATOR[14:8];

The Gliding process continues until, upper 7 bits of the accumulator matches the value of the DAC\_new.

ACCUMULATOR[14:8]  $\geq$  DAC\_new, when DAC\_new > DAC old

ACCUMULATOR[14:8]  $\leq$  DAC\_new, when DAC\_new < DAC\_old

The Glide timer will reference the 2 MHz clock divided to provide between 2  $\mu$ s and 62  $\mu$ s per glide step.

Each DAC is independent in terms of its switching operation, thus each DAC may be independently programmed for Normal, Turbo or Glide regardless of the switching operation of the other DACs.

Use-case hint:

In a scenario where the Turbo delay needs to be set to 54 us and the glide should be taking  $\sim$ 7 ms, the DAC\_TIMER can be configured as  $7000/256 = 27~\mu s$  and the DAC\_TC2X configuration can be set. This way the timer value would not need to be updated during the glide – turbo switches, and only the GL\_X bit in DAC value update needs to be toggled.

#### **Transition from Glide to Glide**

In the event a new glide request is received during a glide transition, the ongoing glide operation is halted and the new glide operation is started from the DAC value, where the previous glide has left off. The DAC timers can be updated to a new value at the trigger.

#### Transition from Glide to Turbo or Normal Switching

In the event that a new Normal switching or Turbo DAC value is received during a Glide transition, then the Glide process is stopped and the DAC immediately switches to the newly received target value without Turbo or Glide. The hi\_slew is not applied.

## DAC Disable during Glide (including active to low power mode transition)

If the DAC, which is gliding is disabled, the DAC value holds on to the value where the glide stops. The DAC does

not continue with the glide when it is re-enabled. It drives the last calculated DAC value without a hi\_slew.

## **DAC Update Triggering**

The entire digital logic responsible for DAC updates is using the clock provided by the internal RC oscillator. In order to minimize the power consumption, the RC clock is set at a low frequency around 2 MHz.

## **DAC Writes**

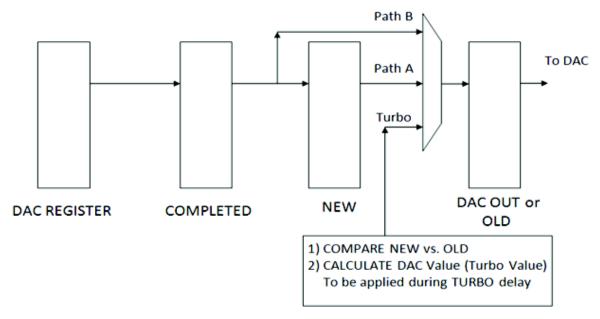

Figure 9 shows the diagram of the DAC data path, from the moment data is written into DACx\_value register, until it is sent out to DAC.

After the DACx\_value register is written using MIPI-RFFE clock, the data is copied on RC clock domain, into the first data stage represented in Figure 9 as 'Completed'. The data is moved into 'New' and 'DAC-Out' stages by the DAC driver state machine, once the trigger is detected. The Turbo path also highlights the glide calculation.

If SW trigger is not enabled, then data will flow through the stages right after the corresponding DAC is updated, without waiting for a trigger (MIPI write is considered as the trigger).

Figure 9. DACx Data Path

To bypass the SW trigger and enable an immediate trigger the Mask bits under the RFFE PM TRIG register should be set according to the USID control of the DAC. Trigger Mask 2 is controller with USID\_2, Trigger Mask 1 is controlled with USID 1 and Trigger Mask 0 is controlled with USID 0. In MIPI-RFFE configuration, if RFFE PM TRIG / **'1'**, and RFFE PM TRIG Trigger Mask 2 Trigger Mask 1 '1' and RFFE PM TRIG Trigger\_Mask\_0 = '1' (all software triggers are masked), then each DAC value is copied into 'Completed' stages of each DAC. after the messages RFFE REG 0x06, RFFE\_REG\_0x07 or RFFE\_REG\_0x08 respectively are received, as shown in following sequence.

MIPI\_RFFE\_WRITE #1: send DAC\_A\_value and glide/turbo mode to RFFE\_REG\_0x06

MIPI\_RFFE\_WRITE #2: send DAC\_B\_value and glide/turbo mode to RFFE\_REG\_0x07

MIPI\_RFFE\_WRITE #3: send DAC\_C\_value and glide/turbo mode to RFFE\_REG\_0x08

The individual writes above could be combined into a single extended write with all DACs controlled with the

same USID or the DURs of the DACs are sitting at "11" configuration. Right after MIPI\_RFEE\_WRITE #1 to RFFE\_REG\_0x06, above, is received the DAC\_A value register is copied in 'Completed' stage of DAC\_A. The timers DO NOT need to be updated for each DAC update. But if they need to be, they can be updated as part of a full extended write or single write prior to the DAC value updates without any timing limitation. Since the SW trigger is masked, next RC clock cycle after DAC values are copied in 'Completed' stage, the data will move in next stages 'New' and 'DAC-Out' without waiting for any trigger.

The similar events occur for DAC\_B and DAC\_C after the MIPI\_RFEE\_WRITE #2 and MIPI\_RFEE\_WRITE #3.

Due to the fact that the MIPI–RFFE master can send DAC updates messages at a higher frequency, than RC clock, the data buffer 'Completed', can be overwritten if new DAC updates occur in the same time when the buffer is loaded.

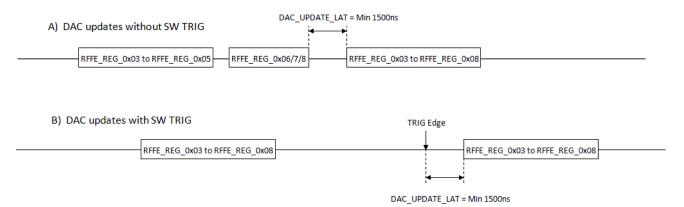

While data and configuration are copied from DACx\_value register into 'Completed' stage, the MIPI-RFFE master must not send any new DAC updates to DACx\_value registers or configurations. The time required

for the data to be copied from DACx\_value register into 'Completed' stage is Max 1500 ns, which is defined by the three RC clock cycles required to synchronize data from MIPI-RFFE clock domain to RC clock domain.

In Figure 10, DAC\_UPDATE\_LAT represents the period when MIPI-RFFE master is not allowed to send any new DAC updates to DACx\_value registers and DAC configuration registers.

The DAC enables (RFFE\_REG\_0x00) and Booster configurations (RFFE\_REG\_0x02) are applied immediately without waiting any trigger. These registers should be configured prior, so that the DAC updates are effective as fast as possible. In test mode the hi\_slew settings are sampled at the trigger similar to the dac\_timers.

Figure 10. DAC\_UPDATE\_LAT Requirement

The SW trigger as well as immediate trigger can be configured in many combinations using the DUR settings of the DACs and the USID values. The SW trigger masks can only be changed with the write access using the slave address of their corresponding USID. But the corresponding triggers can be set by accesses over broadcast, with broadcast ID (0x0) or GSID.

The triggering and DAC register access is governed by these rules:

- The DUR configuration assigns a DAC to a USID. The corresponding DAC registers can only be accessed with USID defined by its DUR.

- The immediate update of this DAC is enabled if the SW trigger mask of the corresponding USID is set (disabled).

- The PM\_TRIG register bit0 (SW trigger0) is masked by bit4 and assigned to DACs triggering, which are mapped to USID0 or all USIDs (the DAC DUR=0 or 3).

- The PM\_TRIG register bit1 (SW trigger1) is masked by bit5 and assigned to DACs triggering, which are mapped to USID1 or all USIDs (the DAC DUR=1 or 3).

- The PM\_TRIG register bit2 (SW trigger2) is masked by bit6 and assigned to DACs triggering, which are mapped to USID2 or all USIDs (the DAC DUR=2 or 3).

- For a DAC with DUR=3, all SW masks need to be set for that DAC to be triggered with direct access to its target register.

If all DACs are kept at DUR values of 3 and the USIDs are kept the same (reset condition), the part behaves according to the MIPI spec with single USID. If some of the USIDs are different while DUR=3, the part responds to the accesses with these different USIDs the same fashion.

If all USIDs are kept equal, the part functions with a single USID. But the DUR settings still control the SW trigger mapping for the DACs independent of the USID values. The DACs which are not holding a DUR value of 3 will be under the control of the SW trigger—mask duo mapped by their DUR setting.

In Table 12 some example register settings for listed functionality are provided. For the given functionality the response of the part to DAC updates and SW triggers are tabulated. In this table the "DAC trigger" corresponds to a trigger happening at the time of the DAC value update. The "SW trigger" corresponds to a trigger happening with the PM\_TRIG register write. At this point, it is assumed that the DACs are enabled and the new DAC value is not matching to the existing pre–triggered DAC value in the active register. Some of the abbreviations utilized in the table are:

TRG = successful trigger of the new targets

HLD = no trigger, hold on to existing DAC drives

WR = The new DAC values are captured into RFFE shadow registers

NW = The RFFE write to shadow registers are blocked, no register update.

Table 12. IMMEDIATE vs SOFTWARE TRIGGERING USING USIDs and DURs

| Table 12. IIVIVIEDIATE VS                                                                                                                        | 00                |                   |                   |                     | 00.                     |                         | J. D G G                | a D                       |                           |                           |                           |                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|---------------------|-------------------------|-------------------------|-------------------------|---------------------------|---------------------------|---------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FUNCTIONALITY & EXAM-<br>PLE REGISTER VALUES                                                                                                     | DACA<br>WR<br>ID0 | DACA<br>WR<br>ID1 | DACA<br>WR<br>ID2 | DACA<br>WR<br>Broad | Trigger<br>3b111<br>ID0 | Trigger<br>3b111<br>ID1 | Trigger<br>3b111<br>ID2 | Trigger<br>3b111<br>Broad | Trigger<br>3b001<br>Broad | Trigger<br>3b010<br>Broad | Trigger<br>3b100<br>Broad | Comments                                                                                                                                                         |

| (DEFAULT) DAC TRIGGER - SINGLE USID - DUR=3 DUR_A = 3 (USIDx, TRGx) SW-TRG Mask = 3'b111 USID0,1,2 = 4b0111                                      | TRG<br>(WR)       | TRG<br>(WR)       | TRG<br>(WR)       | HLD<br>(NW)         | HLD                     | HLD                     | HLD                     | HLD                       | HLD                       | HLD                       | HLD                       | All USIDs are the same. All<br>SW triggers are masked.<br>The USID DAC writes trig-<br>ger immediately.                                                          |

| SW TRIGGER -SINGLE<br>USID - DUR =3<br>DUR_A = 3 (USIDx, TRGx)<br>SW-TRG Mask = 3'b101<br>USID0,1,2 = 4b0111                                     | HLD<br>(WR)       | HLD<br>(WR)       | HLD<br>(WR)       | HLD<br>(NW)         | TRG                     | TRG                     | TRG                     | TRG                       | HLD                       | TRG                       | HLD                       | All USIDs are the same. Only trigger 1 is enabled. This enables the SW trigger since DUR=3, mapping the DAC to all triggers                                      |

| DAC TRIGGER -SINGLE<br>USID - DUR=0<br>DUR_A = 0 (USID0, TRG0)<br>SW-TRG Mask = 3'b101<br>USID0,1,2 = 4b0111                                     | TRG<br>(WR)       | TRG<br>(WR)       | TRG<br>(WR)       | HLD<br>(NW)         | HLD                     | HLD                     | HLD                     | HLD                       | HLD                       | HLD                       | HLD                       | All USIDs are the same. Only trigger 1 is enabled. The DUR of the DAC is mapping it to trigger 0 (masked). Therefore SW trigger is disabled.                     |

| SW TRIGGER -SINGLE<br>USID - DUR =1<br>DUR_A = 1 (USID1, TRG1)<br>SW-TRG Mask = 3'b101<br>USID0,1,2 = 4b0111                                     | HLD<br>(WR)       | HLD<br>(WR)       | HLD<br>(WR)       | HLD<br>(NW)         | TRG                     | TRG                     | TRG                     | TRG                       | HLD                       | TRG                       | HLD                       | All USID's are the same.<br>Only trigger 1 is enabled.<br>The DUR of the DAC is<br>mapping it to trigger 1 (en-<br>abled). Therefore SW trig-<br>ger is enabled. |

| DAC TRIGGER - (1,2)<br>USIDs - DUR=2<br>DUR_A = 2 (USID2, TRG2)<br>SW-TRG Mask = 3'b100<br>USID0,1 = 4b0111, USID2 =<br>4b1000                   | HLD<br>(NW)       | HLD<br>(NW)       | TRG<br>(WR)       | HLD<br>(NW)         | HLD                     | HLD                     | HLD                     | HLD                       | HLD                       | HLD                       | HLD                       | USID2 is different, only<br>USID2 dac access is al-<br>lowed and the DAC trig-<br>gers immediately, since the<br>SW trigger mask is set.                         |

| SW TRIGGER - (1,2)<br>USIDs - DUR =2<br>DUR_A = 2 (USID2, TRG2)<br>SW-TRG Mask = 3'b000<br>USID0,1 = 4b0111, USID2 =<br>4b1000                   | HLD<br>(NW)       | HLD<br>(NW)       | HLD<br>(WR)       | HLD<br>(NW)         | HLD                     | HLD                     | TRG                     | TRG                       | HLD                       | HLD                       | TRG                       | USID2 is different, only<br>USID2 dac access is al-<br>lowed. Trigger 2 is un-<br>masked, SW trigger is en-<br>abled. Only trigger 2 is ac-<br>tive for USID2.   |

| DAC TRIGGER - (2,1)<br>USIDs - DUR = 1<br>DUR_A = 1 (USID1, TRG1)<br>SW-TRG Mask = 3'b110<br>USID0,1 = 4b0111, USID2 =<br>4b1000                 | TRG<br>(WR)       | TRG<br>(WR)       | HLD<br>(NW)       | HLD<br>(NW)         | HLD                     | HLD                     | HLD                     | HLD                       | HLD                       | HLD                       | HLD                       | Since USID0 = USID1 both<br>USID0, USID1 DAC target<br>writes are allowed. SW<br>trigger1 masked; SW trig-<br>gering disabled                                    |

| SW TRIGGER - (2,1)<br>USIDs -DUR = 1<br>DUR_A = 1 (USID1, TRG1)<br>SW-TRG Mask = 3'b100<br>USID0,1 = 4b0111, USID2 =<br>4b1000                   | HLD<br>(WR)       |                   | HLD<br>(NW)       | HLD<br>(NW)         | TRG                     | TRG                     | HLD                     | TRG                       | HLD                       | TRG                       | HLD                       | Same as above but SW trigger 1 is enabled; SW triggering enabled. USID0, USID1 are the same but the DAC is mapped to Trg1 only. Trg0 alone does not trigger.     |

| DAC TRIGGER - (1,1,1)<br>USIDs - DUR = 0<br>DUR_A = 0 (USID0, TRG0)<br>SW-TRG Mask = 3'b001<br>USID0 = 4b0111, USID1 =<br>4b1000, USID2 = 4b1001 | TRG<br>(WR)       | HLD<br>(NW)       | HLD<br>(NW)       | HLD<br>(NW)         | HLD                     | HLD                     | HLD                     | HLD                       | HLD                       | HLD                       | HLD                       | The DAC is mapped to USID0 and the corresponding trigger is masked. It triggers immediately at DAC update with USID0                                             |

| SW TRIGGER - (1,1,1)<br>USIDS - DUR = 0<br>DUR_A = 0 (USID0, TRG0)<br>SW-TRG Mask = 3'b000<br>USID0 = 4b0111, USID1 =<br>4b1000, USID2 = 4b1001  | HLD<br>(WR)       | HLD<br>(NW)       | HLD<br>(NW)       | HLD<br>(NW)         | TRG                     | HLD                     | HLD                     | TRG                       | TRG                       | HLD                       | HLD                       | The DAC is mapped to USID0 and the TRG0 is enabled. It triggers only at TRG0 with USID0 or Broadcast access                                                      |

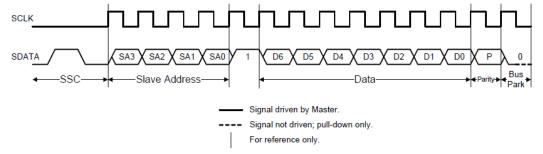

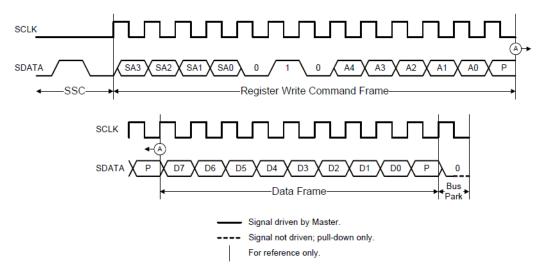

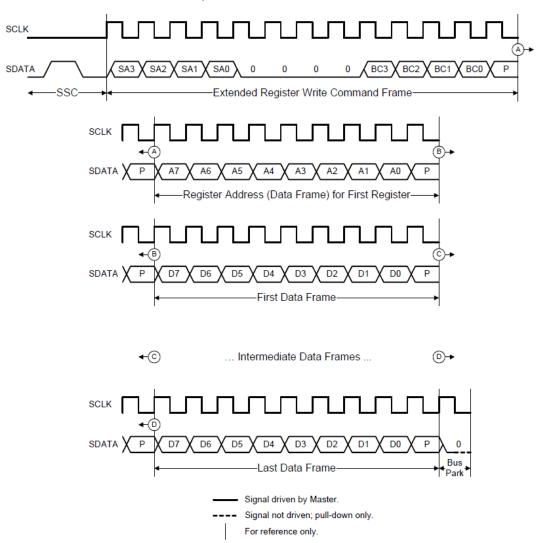

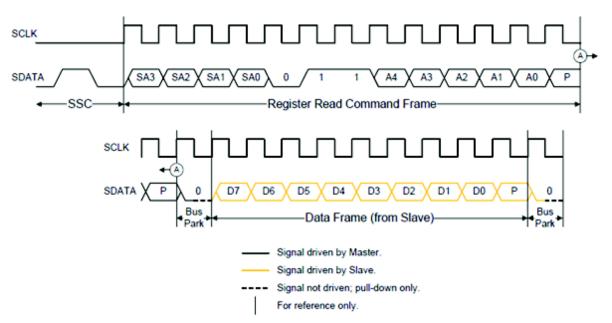

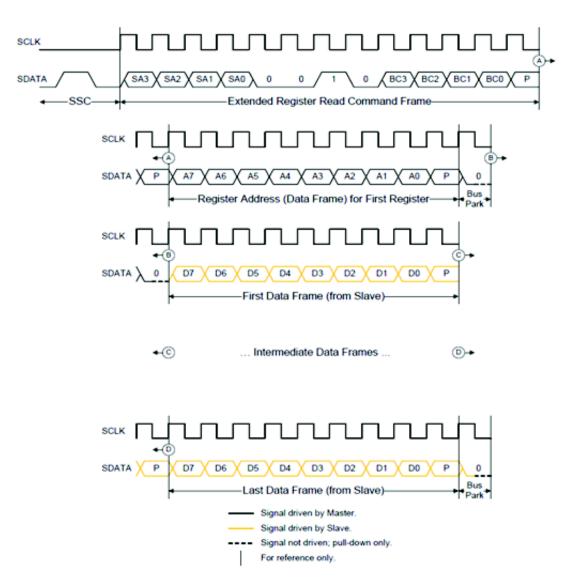

#### **MIPI RFFE Interface**

TCC-303 is a slave device and is fully compliant to the MIPI Alliance Specification for RF Front-End Control Interface (RFFE) Version 1.10.00.

Following MIPI RFFE commands are supported:

- 1. Register 0 WRITE

- 2. Register WRITE

- 3. Register READ

- 4. Extended Register WRITE

- 5. Extended Register READ

Registers 0x00 to 0x1F are available to be read/written. At full-speed read with heavy load, the RFFE read mode bit RFFE\_RDM can be configured to '1', to shift the data capture to falling edge. Otherwise it is recommended to keep this bit in its default state, since the falling edge read data

capture is a violation for RFFE interface standard. The violation is due to the toggling during the 2<sup>nd</sup> half of the bus park cycle, which could create bus contention with the master.

The extended register write long and read long commands are not supported. If an extended register write long command is received, no register is written and the RFFE\_STATUS.WURE flag is set. If an extended register read long command is received, the part responds with bus idle and the RFFE\_STATUS.RURE flag is set.

The read access to registers RFFE\_REG\_0x03 to RFFE\_REG\_0x08 returns the active register content, which is the register updated after a trigger. The pre-trigger shadow register does not have read access.

Table 13. MIPI RFFE INTERFACE SPECIFICATION ( $T_A = -30 \text{ to } +85^{\circ}\text{C}$ ; 2.3 V < VDDA < 5.5 V; 1.1 V <  $V_{IO}$  < 1.8 V; unless otherwise specified)

| Parameter                | Description                                                | Min        | Тур | Max       | Unit | Comments                                                                      |

|--------------------------|------------------------------------------------------------|------------|-----|-----------|------|-------------------------------------------------------------------------------|

| F <sub>SCLK</sub>        | Clock Full-Speed<br>Frequency                              | 0.032      | _   | 26        | MHz  | Full-Speed Operation:<br>1.65 V < V <sub>IO</sub> < 1.95 V                    |

| T <sub>SCLK</sub>        | Clock Full-Speed Period                                    | 0.038      | _   | 32        | μS   | Full-Speed Operation:<br>1.65 V < V <sub>IO</sub> < 1.95 V                    |

| T <sub>SCLKIH</sub>      | CLK Input High Time                                        | 11.25      | -   | -         | ns   | Full-Speed                                                                    |

| T <sub>SCLKIL</sub>      | CLK Input Low Time                                         | 11.25      | -   | -         | ns   | Full-Speed                                                                    |

| V <sub>TP</sub>          | Positive Going Threshold<br>Voltage                        | 0.4 x VIO  | -   | 0.7 x VIO | V    | CLK, DATA, 1.2 or 1.8 V Bus                                                   |

| V <sub>TN</sub>          | Negative Going Thresh-<br>old Voltage                      | 0.3 x VIO  | -   | 0.6 x VIO | V    | CLK, DATA, 1.2 or 1.8 V Bus                                                   |

| V <sub>H</sub>           | Hysteresis Voltage<br>(V <sub>TP</sub> - V <sub>TN</sub> ) | 0.1 x VIO  | -   | 0.4 x VIO | V    | CLK, DATA, 1.2 or 1.8 V Bus                                                   |

| I <sub>IH</sub>          | Input Current High                                         | -2         | -   | +10       | μΑ   | SDATA = 0.8 x VIO                                                             |

|                          |                                                            | <b>-1</b>  | -   | +10       | μΑ   | SCLK = 0.8 x VIO                                                              |

| I <sub>IL</sub>          | Input Current Low                                          | -2         | -   | +1        | μΑ   | SDATA = 0.2 x VIO                                                             |

|                          |                                                            | <b>–</b> 1 | -   | +1        | μΑ   | SCLK = 0.2 x VIO                                                              |

| C <sub>CLK</sub>         | Input Capacitance                                          | -          | -   | 2.2       | pF   | CLK Pin                                                                       |

| C <sub>DATA</sub>        | Input Capacitance                                          | _          | -   | 2.5       | pF   | DATA Pin                                                                      |

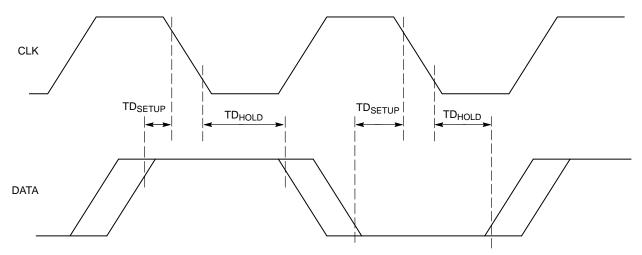

| TD <sub>SETUP</sub>      | Write DATA Setup Time                                      | -          | -   | 1         | ns   | Full-Speed                                                                    |

| TD <sub>HOLD</sub>       | Write DATA Hold Time                                       | -          | -   | 5         | ns   | Full-Speed                                                                    |

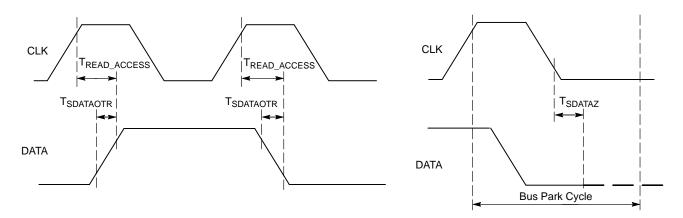

| T <sub>READ_ACCESS</sub> | Read DATA valid from<br>CLK rising edge                    | -          | -   | 7.11      | ns   | Full Speed at V <sub>IO</sub> = 1.80 V, +25°C, and max 15 pF load on DATA pin |

| T <sub>READ_ACCESS</sub> | Read DATA valid from<br>CLK rising edge                    | -          | -   | 9.11      | ns   | Full Speed at V <sub>IO</sub> = 1.80 V, +25°C, and max 50 pF load on DATA pin |

Figure 11. MIPI-RFFE Signal Timing during Master Writes to PTIC Control IC

Figure 12. MIPI-RFFE Signal Timing during Master Reads from PTIC Control IC

Figure 13. Bus Park Cycle Timing when MIPI-RFFE Master Reads from PTIC Control IC

The control IC contains eighteen 8-bit registers. Register content is described in Table 14. Some additional registers implemented as provision, are not described in this document.

Table 14. MIPI RFFE ADDRESS MAP

| Address      | Description              | USID                     | Purpose                                                             | Access           | Size [bits] |

|--------------|--------------------------|--------------------------|---------------------------------------------------------------------|------------------|-------------|

| 0x00         | RFFE_REG_0x00            | All                      | DAC enables                                                         | R/W<br>RegWrite0 | 8           |

| 0x01         | RFFE_REG_0x01            | All                      | DUR for DAC_A/_B/_C                                                 | R/W              | 8           |

| 0x02         | RFFE_REG_0x02            | All                      | All Booster settings                                                |                  | 8           |

| 0x03         | RFFE_REG_0x03            | DUR_A                    | DAC_A timer setup                                                   | R/W              | 8           |

| 0x04         | RFFE_REG_0x04            | DUR_B                    | DAC_B timer setup                                                   | R/W              | 8           |

| 0x05         | RFFE_REG_0x05            | DUR_C                    | DAC_C timer setup                                                   | R/W              | 8           |

| 0x06         | RFFE_REG_0x06            | DUR_A                    | Used to set up / trigger OUT A                                      | R/W              | 8           |

| 0x07         | RFFE_REG_0x07            | DUR_B                    | Used to set up / trigger OUT B                                      | R/W              | 8           |

| 0x08         | RFFE_REG_0x08            | DUR_C                    | Used to set up / trigger OUT C                                      | R/W              | 8           |

| 0x09         | RFFE_REG_0x09            | All                      | RFFE read mode control                                              | R/W              | 8           |

| 0x09 to 0x17 | SPARE                    | N/A                      | Spare for future product development                                | R/W              | 8           |

| 0x18         | USID_1                   | USID_1<br>&<br>Broadcast | Spare [7:6]<br>[5,4] = Manufacturer ID [9:8]<br>USID_1 [3:0]        | R/W              | 8           |

| 0x19         | USID_2                   | USID_2<br>&<br>Broadcast | Spare [7:6]<br>[5,4] = Manufacturer ID [9:8]<br>USID_2 [3:0]        | R/W              | 8           |

| 0x1A         | RFFE_STATUS              | All                      | RFFE status register                                                | R/W              | 8           |

| 0x1B         | RFFE_GROUP_SID           | All                      | The Group Broadcast ID                                              | R/W              | 8           |

| 0x1C         |                          |                          | Power Mode & Trigger Control<br>PWR_MODE [7:6]<br>TRIG_REG [5:0]    | R/W              | 8           |

| 0x1D         | PID_0, default           | All                      | MIPI Product ID (Note 2)                                            | R                | 8           |

| 0x1E         | Manufacturer ID Register | All                      | MN (10bits long)<br>Manufacturer ID[7:0] (Note 2)                   | R                | 8           |

| 0x1F         | USID_0, default          | USID_0<br>&<br>Broadcast | Spare [7:6]<br>[5,4] = Manufacturer ID [9:8] (Note 3)<br>USID [3:0] | R/W              | 8           |

<sup>2.</sup> The least significant bits from the Product ID register are refined by OTP. The other seven bits of product ID are hardcoded in ASIC.

## **Register Content Details**

| Register RFFE:                                                                             |       | RF    | FE_REG_0x00 | Addr  | ess RFFE A[4: | :0]:     | [0x00]   |          |  |  |

|--------------------------------------------------------------------------------------------|-------|-------|-------------|-------|---------------|----------|----------|----------|--|--|

| Reset Source: nreset_dig or SWR = '1' or PWR_MODE = '01' (transition through STARTUP mode) |       |       |             |       |               |          |          |          |  |  |

|                                                                                            | 7     | 6     | 5           | 4     | 3             | 2        | 1        | 0        |  |  |

| Bits                                                                                       | spare | spare | spare       | spare | spare         | DAC C en | DAC B en | DAC A en |  |  |

|                                                                                            |       |       |             |       |               |          |          |          |  |  |

Bit [2:0] Each DAC is enabled when the corresponding bit is set. The enable or disable occurs immediately without waiting for a trigger. 0: Off (default) 1: enabled

Bit [7]: Register 0 write command excludes this bit. The extended writes to this address ignores bit 7. The bit is not utilized.

<sup>3.</sup> The manufacturer ID is hardcoded in ASIC, mapped in a READ-only register.

| Register RFFE: | RFFE_REG_0x01 | Address RFFE A[4:0]: | 0x01 |

|----------------|---------------|----------------------|------|

|----------------|---------------|----------------------|------|

Reset Source: nreset\_dig or SWR = '1' or PWR\_MODE = '01' (transition through STARTUP mode)

|       | 7   | 6   | 5    | 4       | 3    | 2       | 1    | 0       |

|-------|-----|-----|------|---------|------|---------|------|---------|

| Bits  | spa | are | DUR_ | C [1:0] | DUR_ | B [1:0] | DUR_ | A [1:0] |

| Reset | U-0 | U-0 | W-1  | W-1     | W-1  | W-1     | W-1  | W-1     |

DUR\_x [1:0] (DAC x USID response)

- '00': Responds only to USID 0 in DAC register write. SW trigger0 mask defines the triggering source.

- '01': Responds only to USID\_1 in DAC register write. SW trigger1 mask defines the triggering source.

- '10': Responds only to USID\_2 in DAC register write. SW trigger2 mask defines the triggering source.

- '11': Responds to any 3 USID in DAC register write. Any trigger mask cleared enables the SW triggering.

| Register RFFE: | RFFE_REG_0x02 | Address RFFE A[4:0]: | 0x02 |

|----------------|---------------|----------------------|------|

Reset Source: nreset\_dig or SWR = '1' or PWR\_MODE = '01' (transition through STARTUP mode)

|       | 7            | 6            | 5     | 4        | 3                   | 2   | 1   | 0   |

|-------|--------------|--------------|-------|----------|---------------------|-----|-----|-----|

| Bits  | boost_clk_en | boost_pwm_en | spare | boost_en | Boost voltage value |     |     |     |

| Reset | W-1          | W-1          | U-0   | W-1      | W-1                 | W-0 | W-1 | W-1 |

Bit [7]: Enables the booster clock. The clock should be disabled when the booster is turned off.

Bit [6]: Enables the boost oscillator pwm function. This signal should be turned off in case the booster generates low voltages to reduce the ripple.

Bit [4]: Enable/disable of the booster. Booster must be turned off when the high voltage is provided externally.

Bit [3:0]: **Boost voltage value**. Refer to Table 15 for values

**Table 15. BOOST VOLTAGE SETTING**

| Boost Voltage Value[3:0] | VHV [V] | Note          | Boost Voltage Value[3:0] | VHV [V]      | Note           |

|--------------------------|---------|---------------|--------------------------|--------------|----------------|

| 0000                     | 13      |               | 1000                     | 21           |                |

| 0001                     | 14      | ]             | 1001                     | 22           |                |

| 0010                     | 15      | ]             | 1010                     | 23           |                |

| 0011                     | 16      | Tananturalura | 1011                     | 24 (default) | Tannativalivas |

| 0100                     | 17      | Target values | 1100                     | 25           | Target values  |

| 0101                     | 18      | ]             | 1101                     | 26           |                |

| 0110                     | 19      | 1             | 1110                     | 27           |                |

| 0111                     | 20      | 1             | 1111                     | 28           | 1              |

| Register RFFE: | RFFE_REG_0x03 | Address RFFE A[4:0]: | [0x03] |

|----------------|---------------|----------------------|--------|

|----------------|---------------|----------------------|--------|

Reset Source: nreset\_dig or SWR = '1' or PWR\_MODE = '01' (transition through STARTUP mode)

|       | 7          | 6    | 5      | 4           | 3   | 2   | 1   | 0   |  |

|-------|------------|------|--------|-------------|-----|-----|-----|-----|--|

| Bits  | DAC_TC2X_A | DAC_ | _TCM_A | DAC_TIMER_A |     |     |     |     |  |

| Reset | W-0        | W-0  | W-0    | W-0         | W-0 | W-0 | W-0 | W-0 |  |

Bit [7] If this bit is set, in Turbo mode dac\_timer \* 2 value is loaded into the DAC timer. The glide always sets the step delay to dac\_timer value independent of this bit.

Bit [6:5] It defines the multiplication factor of timer extension when the turbo-down value is below 4 V.

Bit [4:0] For the definition of dac timer field, see Table 10.

NOTE: The read access to this register will return the active content post-trigger, not the shadow register.

| Register RFF | E: | RFFE_REG_0x04 | Address RFFE A[4:0]: | [0x04] |

|--------------|----|---------------|----------------------|--------|

|--------------|----|---------------|----------------------|--------|

<u>Reset Source:</u> nreset\_dig or SWR = '1' or PWR\_MODE = '01' (transition through STARTUP mode)

|       | 7          | 6    | 5     | 4   | 3   | 2   | 1   | 0   |

|-------|------------|------|-------|-----|-----|-----|-----|-----|

| Bits  | DAC_TC2X_B | DAC_ | TCM_B |     |     |     |     |     |

| Reset | W-0        | W-0  | W-0   | W-0 | W-0 | W-0 | W-0 | W-0 |

Bit [7] If this bit is set, in Turbo mode dac\_timer \* 2 value is loaded into the DAC timer. The glide always sets the step delay to dac timer value independent of this bit.

Bit [6:5] Defines the multiplication factor of timer extension when the turbo-down value is below 4 V

Bit [4:0] For definition of dac\_timer field, see Table 10.

NOTE: The read access to this register will return the active content post-trigger, not the shadow register.

| Register RFFE: RFFE_REG_0x05 Address RFFE A[4 | 4:0]: [0x05] |

|-----------------------------------------------|--------------|

|-----------------------------------------------|--------------|

Reset Source: nreset\_dig or SWR = '1' or PWR\_MODE = '01' (transition through STARTUP mode)

|       | 7          | 6    | 5     | 4           | 3   | 2   | 1   | 0   |  |

|-------|------------|------|-------|-------------|-----|-----|-----|-----|--|

| Bits  | DAC_TC2X_C | DAC_ | TCM_C | DAC_TIMER_C |     |     |     |     |  |

| Reset | W-0        | W-0  | W-0   | W-0         | W-0 | W-0 | W-0 | W-0 |  |

Bit [7] If this bit is set, in Turbo mode dac\_timer \* 2 value is loaded into the DAC timer. The glide always sets the step delay to dac\_timer value independent of this bit.

Bit [6:5] Defines the multiplication factor of timer extension when the turbo-down value is below 4 V

Bit [4:0] For definition of dac timer field, see Table 10.

NOTE: The read access to this register will return the active content post-trigger, not the shadow register.

| Register RFFE:     |              | Address RFFE | A[4:0]:     | 0x06  |   |   |

|--------------------|--------------|--------------|-------------|-------|---|---|

| Reset Source: nres | et_dig or SW | tion through | n STARTUP n | node) |   |   |

|                    |              |              |             | _     | - | _ |

|       | 7    | 6   | 6 5 4 3 2 1       |     |     |     |     |     |  |  |

|-------|------|-----|-------------------|-----|-----|-----|-----|-----|--|--|

| Bits  | GL_A |     | DAC A value [6:0] |     |     |     |     |     |  |  |

| Reset | W-0  | W-0 | W-0               | W-0 | W-0 | W-0 | W-0 | W-0 |  |  |

Bit [7] If the GL\_A=1, a non-zero value in DAC timer in starts a glide. If GL\_A =0 and the DAC\_TIMER\_A is not zero, Turbo is started with the new DAC A value.

NOTE: The read access to this register will return the active content post-trigger, not the shadow register. The DAC value read-back is not the actual analog drive, it is the target level.

| Register RFFE: RFFE_REG_0x07                                                               |  |  |  |  |  |  |               | ddress RFFE | A[4:0]: |  | 0x07 |

|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|---------------|-------------|---------|--|------|

| Reset Source: nreset_dig or SWR = '1' or PWR_MODE = '01' (transition through STARTUP mode) |  |  |  |  |  |  |               |             |         |  |      |

|                                                                                            |  |  |  |  |  |  | $\overline{}$ |             |         |  |      |

|       | 7    | 6   | 6 5 4 3 2 1       |     |     |     |     |     |  |

|-------|------|-----|-------------------|-----|-----|-----|-----|-----|--|

| Bits  | GL_B |     | DAC B value [6:0] |     |     |     |     |     |  |

| Reset | W-0  | W-0 | W-0               | W-0 | W-0 | W-0 | W-0 | W-0 |  |

Bit [7] If the GL\_B=1, a non-zero value in DAC timer in starts a glide. If GL\_B =0 and the DAC\_TIMER\_B is not zero, Turbo is started with the new DAC B value.