### **PRODUCT FEATURES**

- USB-IF "Hi-Speed" certified to USB 2.0 electrical specification

- Interface compliant with the UTMI specification (60MHz 8-bit unidirectional interface or 30MHz 16-bit bidirectional interface)

- Supports 480Mbps High Speed (HS) and 12Mbps Full Speed (FS) serial data transmission rates

- Integrated 45Ω and 1.5kΩ termination resistors reduce external component count

- Internal short circuit protection of DP and DM lines

- On-chip oscillator operates with low cost 12MHz crystal

- Robust and low power digital clock and data recovery circuit

- SYNC and EOP generation on transmit packets and detection on receive packets

- NRZI encoding and decoding

- Bit stuffing and unstuffing with error detection

- Supports the USB suspend state, HS detection, HS Chirp, Reset and Resume

- Support for all test modes defined in the USB 2.0 specification

- Draws 72mA (185mW) maximum current consumption in HS mode - ideal for bus powered functions

- On-die decoupling capacitance and isolation for immunity to digital switching noise

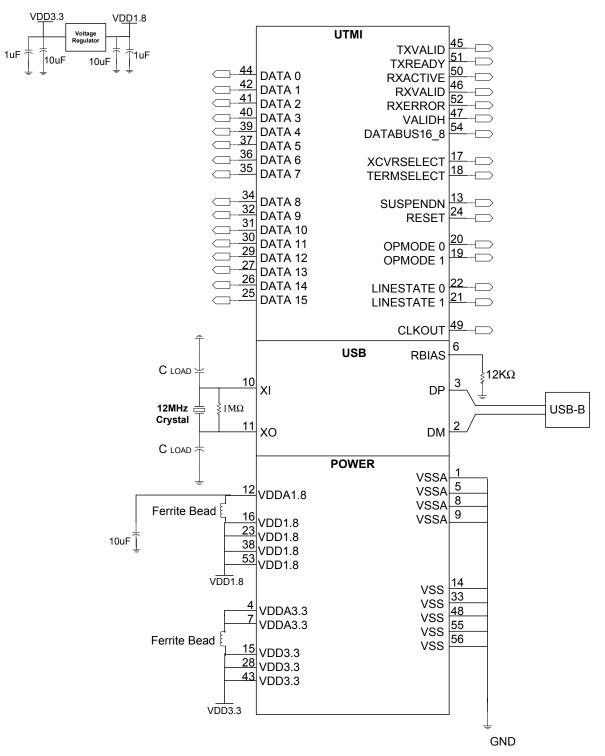

- Available in a 56-pin QFN package

- Full industrial operating temperature range from -40°C to +85°C (ambient)

#### Applications

The Universal Serial Bus (USB) is the preferred interface to connect Hi-Speed PC peripherals.

- Digital Still and Video Cameras

- MP3 Players

- External Hard Drives

- Scanners

- Entertainment Devices

- Printers

- Test and Measurement Systems

- POS Terminals

- Set Top Boxes

Data Brief

#### Ordering Information:

USB3250-ABZJ for 56 pin, QFN lead-free RoHS compliant package, 8 x 8 x 0.85mm

This product meets the halogen maximum concentration values per IEC61249-2-21

For RoHS compliance and environmental information, please visit www.smsc.com/rohs

Copyright © 2013 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

The Microchip name and logo, and the Microchip logo are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

## **General Description**

The USB3250 provides the Physical Layer (PHY) interface to a USB 2.0 Device Controller. The IC is available in a 56 pin QFN.

The USB3250 is a USB 2.0 physical layer transceiver (PHY) integrated circuit. SMSC's proprietary technology results in low power dissipation, which is ideal for building a bus powered USB 2.0 peripheral. The PHY can be configured for either an 8-bit unidirectional or a 16-bit bidirectional parallel interface, which complies with the USB Transceiver Macrocell Interface (UTMI) specification. It supports 480Mbps transfer rate, while remaining backward compatible with USB 1.1 legacy protocol at 12Mbps.

All required termination for the USB 2.0 Transceiver is internal. Internal 5.25V short circuit protection of DP and DM lines is provided for USB compliance.

While transmitting data, the PHY serializes data and generates SYNC and EOP fields. It also performs needed bit stuffing and NRZI encoding. Likewise, while receiving data, the PHY de-serializes incoming data, stripping SYNC and EOP fields and performs bit un-stuffing and NRZI decoding.

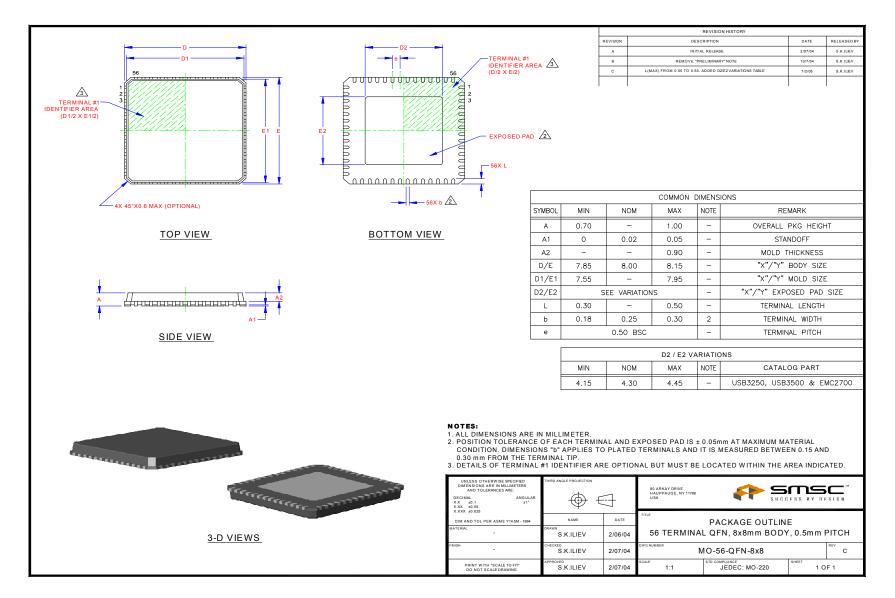

# **Block Diagram**

Figure 1 USB3250 Functional Block Diagram

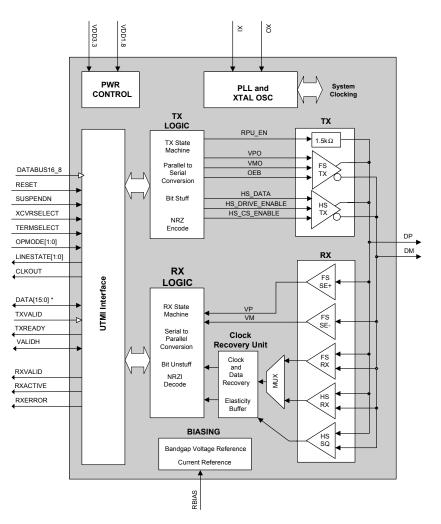

# **Pin Configuration**

Figure 2 56-Pin USB3250 Pin Configuration (Top View)

## **Pin Description Tables**

#### Table 1 System Interface Pins

| NAME           | DIRECTION | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET          | Input     | High            | <b>Reset.</b> Reset all state machines. After coming out of reset, must wait 5 rising edges of clock before asserting TXValid for transmit. Assertion of Reset: May be asynchronous to CLKOUT. De-assertion of Reset: Must be synchronous to CLKOUT unless RESET is asserted longer than two periods of CLKOUT.                                                                         |

| XCVRSELECT     | Input     | N/A             | <b>Transceiver Select.</b> This signal selects between the FS and HS transceivers:<br>0: HS transceiver enabled<br>1: FS transceiver enabled.                                                                                                                                                                                                                                           |

| TERMSELECT     | Input     | N/A             | <b>Termination Select.</b> This signal selects between the FS and HS terminations:<br>0: HS termination enabled<br>1: FS termination enabled                                                                                                                                                                                                                                            |

| SUSPENDN       | Input     | Low             | <b>Suspend.</b> Places the transceiver in a mode that draws minimal power from supplies. Shuts down all blocks not necessary for Suspend/Resume operation. While suspended, TERMSELECT must always be in FS mode to ensure that the 1.5k $\Omega$ pull-up on DP remains powered.<br>0: Transceiver circuitry drawing suspend current 1: Transceiver circuitry drawing normal current    |

| CLKOUT         | Output    | Rising Edge     | <b>System Clock.</b> This output is used for clocking receive and transmit parallel data at 60MHz (8-bit mode) or 30MHz (16-bit mode). When in 8-bit mode, this specification refers to CLKOUT as CLK60. When in 16-bit mode, CLKOUT is referred to as CLK30.                                                                                                                           |

| OPMODE[1:0]    | Input     | N/A             | Operational Mode.These signals select between the various<br>operational modes:[1][0]Description000: Normal Operation011: Non-driving (all terminations removed)102: Disable bit stuffing and NRZI encoding113: Reserved                                                                                                                                                                |

| LINESTATE[1:0] | Output    | N/A             | Line State.These signals reflect the current state of the USB<br>data bus in FS mode, with [0] reflecting the state of DP and [1]<br>reflecting the state of DM. When the device is suspended or<br>resuming from a suspended state, the signals are combinatorial.<br>Otherwise, the signals are synchronized to CLKOUT.[1][0]Description<br>0000: SE0011: J State102: K State113: SE1 |

| DATABUS16_8    | Input     | N/A             | <ul> <li>Databus Select. Selects between 8-bit and 16-bit data transfers.</li> <li>0: 8-bit data path enabled. VALIDH is undefined. CLKOUT = 60MHz.</li> <li>1: 16-bit data path enabled. CLKOUT = 30MHz.</li> </ul>                                                                                                                                                                    |

### **PRODUCT PREVIEW**

| NAME         | DIRECTION | ACTIVE<br>LEVEL |                                                                                                                                                                                                                                                                                                                                                                                             | ſ                                                 | DESCRIPTIO                    | N                                                                                                           |

|--------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------|

| DATA[15:0]   | Bidir     | N/A             | DATA BUS. 16-BIT BIDIRECTIONAL MODE.                                                                                                                                                                                                                                                                                                                                                        |                                                   |                               | CTIONAL MODE.                                                                                               |

|              |           |                 | TXVALID                                                                                                                                                                                                                                                                                                                                                                                     | RXVALID                                           | VALIDH                        | DATA[15:0]                                                                                                  |

|              |           |                 | 0                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                 | Х                             | Not used                                                                                                    |

|              |           |                 | 0                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                 | 0                             | DATA[7:0] output is valid<br>for receive<br>VALIDH is an output                                             |

|              |           |                 | 0                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                 | 1                             | DATA[15:0] output is<br>valid for receive<br>VALIDH is an output                                            |

|              |           |                 | 1                                                                                                                                                                                                                                                                                                                                                                                           | X                                                 | 0                             | DATA[7:0] input is valid<br>for transmit<br>VALIDH is an input                                              |

|              |           |                 | 1                                                                                                                                                                                                                                                                                                                                                                                           | X                                                 | 1                             | DATA[15:0] input is valid<br>for transmit<br>VALIDH is an input                                             |

|              |           |                 | DA                                                                                                                                                                                                                                                                                                                                                                                          | TA BUS. 8-E                                       |                               | CTIONAL MODE.                                                                                               |

|              |           |                 | TXVALID                                                                                                                                                                                                                                                                                                                                                                                     | RXVALID                                           | DATA[15:0]                    |                                                                                                             |

|              |           |                 | 0                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                 | Not used                      |                                                                                                             |

|              |           |                 | 0                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                 | DATA[15:8]                    | output is valid for receive                                                                                 |

|              |           | 1               | Х                                                                                                                                                                                                                                                                                                                                                                                           | DATA[7:0] ii                                      | nput is valid for transmit    |                                                                                                             |

| TXVALID      | Input     | High            | <b>Transmit Valid.</b> Indicates that the TXDATA bus is valid for transmit. The assertion of TXVALID initiates the transmission of SYNC on the USB bus. The negation of TXVALID initiates EOP on the USB.                                                                                                                                                                                   |                                                   |                               |                                                                                                             |

|              |           |                 | must not be o                                                                                                                                                                                                                                                                                                                                                                               | changed on th                                     | e de-assertio                 | ELECT,XCVRSELECT)<br>n or assertion of TXVALID.<br>when these inputs are                                    |

| TXREADY      | Output    | High            | <b>Transmit Data Ready.</b> If TXVALID is asserted, the SIE must<br>always have data available for clocking into the TX Holding<br>Register on the rising edge of CLKOUT. TXREADY is an<br>acknowledgement to the SIE that the transceiver has clocked the<br>data from the bus and is ready for the next transfer on the bus. If<br>TXVALID is negated, TXREADY can be ignored by the SIE. |                                                   |                               |                                                                                                             |

| VALIDH Bidir |           | N/A             | Transmit/Receive High Data Bit Valid (used in 16-bit monly). When TXVALID = 1, the 16-bit data bus direction is changed to inputs, and VALIDH is an input. If VALIDH is as DATA[15:0] is valid for transmission. If deasserted, only DAT is valid for transmission. The DATA bus is driven by the S                                                                                         |                                                   |                               | data bus direction is<br>out. If VALIDH is asserted,<br>deasserted, only DATA[7:0]                          |

|              |           |                 | direction is o<br>VALIDH is a                                                                                                                                                                                                                                                                                                                                                               | changed to ou<br>sserted, the D<br>d, only DATA[7 | tputs, and VA<br>ATA[15:0] ou | , the 16-bit data bus<br>ALIDH is an output. If<br>tputs are valid for receive.<br>or receive. The DATA bus |

| RXVALID      | Output    | High            | valid data. T                                                                                                                                                                                                                                                                                                                                                                               | he Receive Da<br>. The SIE is ea                  | ata Holding R                 | RXDATA bus has received<br>legister is full and ready to<br>ch the RXDATA bus on the                        |

#### Table 2 Data Interface Pins

#### Table 2 Data Interface Pins (continued)

| NAME     | DIRECTION | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                              |

|----------|-----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXACTIVE | Output    | High            | <b>Receive Active.</b> Indicates that the receive state machine has detected Start of Packet and is active.                                                                                              |

| RXERROR  | Output    | High            | <b>Receive Error.</b> 0: Indicates no error. 1: Indicates a receive error has been detected. This output is clocked with the same timing as the RXDATA lines and can occur at anytime during a transfer. |

#### Table 3 USB I/O Pins

| NAME | DIRECTION | ACTIVE<br>LEVEL | DESCRIPTION            |

|------|-----------|-----------------|------------------------|

| DP   | I/O       | N/A             | USB Positive Data Pin. |

| DM   | I/O       | N/A             | USB Negative Data Pin. |

#### Table 4 Biasing and Clock Oscillator Pins

| NAME  | DIRECTION | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                 |

|-------|-----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

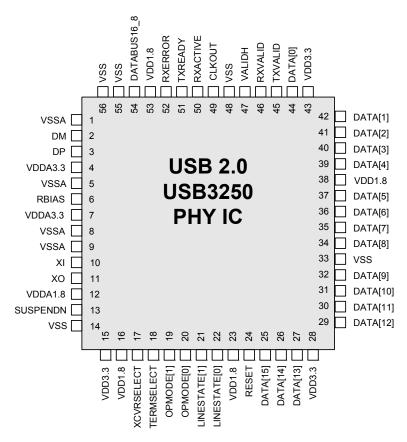

| RBIAS | Input     | N/A             | <b>External 1% bias resistor</b> . Requires a $12K\Omega$ resistor to ground. Used for setting HS transmit current level and on-chip termination impedance. |

| XI/XO | Input     | N/A             | External crystal. 12MHz crystal connected from XI to XO.                                                                                                    |

#### Table 5 Power and Ground Pins

| NAME    | DIRECTION | ACTIVE<br>LEVEL | DESCRIPTION                                                              |

|---------|-----------|-----------------|--------------------------------------------------------------------------|

| VDD3.3  | N/A       | N/A             | 3.3V Digital Supply. Powers digital pads. See Note 2.1                   |

| VDD1.8  | N/A       | N/A             | 1.8V Digital Supply. Powers digital core.                                |

| VSS     | N/A       | N/A             | Digital Ground. See Note 2.2                                             |

| VDDA3.3 | N/A       | N/A             | <b>3.3V Analog Supply</b> . Powers analog I/O and 3.3V analog circuitry. |

| VDDA1.8 | N/A       | N/A             | 1.8V Analog Supply. Powers 1.8V analog circuitry. See Note 2.1           |

| VSSA    | N/A       | N/A             | Analog Ground. See Note 2.2                                              |

- **Note 2.1** A Ferrite Bead (with DC resistance <.5 Ohms) is recommended for filtering between both the VDD3.3 and VDDA3.3 supplies and the VDD1.8 and VDDA1.8 Supplies.

- **Note 2.2** All VSS and VSSA are bonded to the exposed pad under the IC in the package. The exposed pad must be connected to solid GND plane on printed circuit board.

### **PRODUCT PREVIEW**

## **Application Diagram**

Figure 3 Application Diagram for 56-pin QFN Package

### **PRODUCT PREVIEW**

## **Package Outline**

Hi-Speed USB Device Transceiver with UTMI Interface