# **OS81210**

# Intelligent Network Interface Controller for 50 Mbit/s Automotive Networks Product Brief

#### Features

- Complete 50 Mbit/s synchronous network interface

- · Embedded network management functions

- Network protection mode

- Hardware & application watchdog timer

- Intelligent muting

- Diagnostics

- Emergency Response System (eCall)

- IEEE MAC addressing and Ethernet channel

- Universal Serial Bus (USB) Port supports USB 2.0 High-speed upstream data transfers using either:

- USB 2.0 physical layer

- High-Speed Inter-Chip (HSIC) physical layer

- Media Local Bus (MediaLB<sup>®</sup>) Port

- Eases inter-chip communication and streaming

- MediaLB 3-pin interface at speeds up to 1024xFs

- I<sup>2</sup>C<sup>™</sup> Control Port inter-chip message exchange

- Streaming Port supports synchronous, fixed latency data exchange for a variety of serial audio formats including time-division multiplex (TDM) and pulse density modulation (PDM)

- · SPI Port supports asynchronous and control packets

- · General Purpose I/O (GPIO) Port

- Remote control and configuration for operation without a local External Host Controller.

- I<sup>2</sup>C (master) message tunneling

- GPIO port control

- Operating voltages 3.3 V/1.8 V (and 1.2 V for HSIC)

- · Available in 64-pin QFN package with exposed pad

- -40 to +125 °C junction temperature

#### Conformity

This document applies to hardware revision B1A

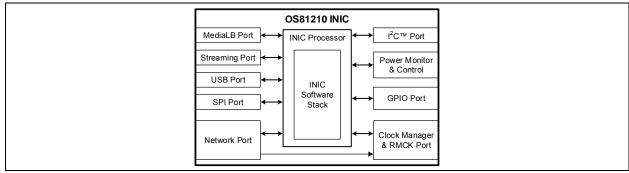

#### FIGURE: OS81210 BLOCK DIAGRAM

#### Applications

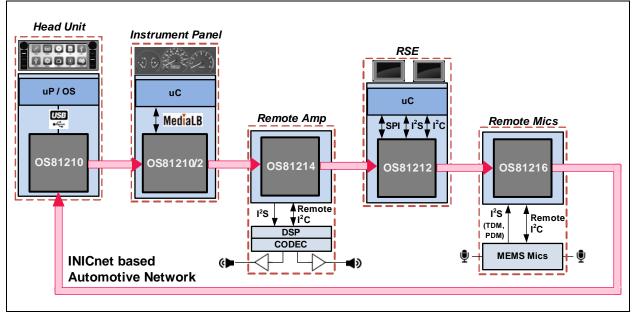

• Automotive infotainment network nodes including head unit, instrument cluster, amplifier, and rear seat entertainment.

#### **General Description**

The OS81210 is a highly integrated *Intelligent Network Interface Controller* (INIC) for 50 Mbit/s INICnet-based automotive networks with a transformer-less balanced media physical layer (bPHY) optimized for unshielded twisted pair (UTP) copper wire.

The INIC provides encapsulation of all low-level functions necessary to develop a network-compliant device, significantly simplifying network implementation in a node. Integration of the *INIC Software Stack* into the INIC provides network-compliant real-time behavior. The *INIC Software Stack* significantly relieves the External Host Controller (EHC) from real-time processing tasks. Supervision of the application is also provided, including a protection mode that is entered when an application is not present (i.e. start-up) or the EHC malfunctions. This protection mode prevents application malfunctions from influencing the integrity of the network and the system.

When the EHC is engaged, a message-based interface, as opposed to a register-based interface, is available for communication with INIC. A unified and centralized network management software stack (UNICENS) is available for the EHC to build a complete, lean, system solution.

The INIC can also support a fully compliant MOST® network.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS300000000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

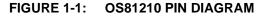

## 1.0 PINOUT

#### TABLE 1-1: OS81210 PIN ALLOCATION TABLE

| Pin | Name                | HW Port | Description                                           |  |  |  |

|-----|---------------------|---------|-------------------------------------------------------|--|--|--|

| 1   | MLBCLK <sup>2</sup> | MediaLB | Singled-ended Clock line for MediaLB 3-pin Interface  |  |  |  |

| 2   | MLBSIG <sup>2</sup> | MediaLB | Singled-ended Signal line for MediaLB 3-pin Interface |  |  |  |

| 3   | MLBDAT <sup>2</sup> | MediaLB | Singled-ended Data line for MediaLB 3-pin Interface   |  |  |  |

| 4   | VDDP1               |         | 3.3 V periphery power supply (digital)                |  |  |  |

| 5   | SDIN                | SPI     | Data In (MOSI - Master Out, Slave In)                 |  |  |  |

| 5   | GP3                 | GPIO    | General Input/Output 3                                |  |  |  |

| 6   | SDOUT               | SPI     | Data Out (MISO - Master In, Slave Out)                |  |  |  |

| 0   | GP4                 | GPIO    | General Purpose Input/Output 4                        |  |  |  |

| 7   | SCLK                | SPI     | Clock                                                 |  |  |  |

|     | GP5                 | GPIO    | General Purpose Input/Output 5                        |  |  |  |

| 8   | SINT                | SPI     | Interrupt (active low)                                |  |  |  |

| 0   | GP6                 | GPIO    | General Purpose Input/Output 6                        |  |  |  |

| 9   | CS                  | SPI     | Chip Select (active low)                              |  |  |  |

| 9   | GP7                 | GPIO    | General Purpose Input/Output 7                        |  |  |  |

| 10  | VDDC1               |         | 1.8 V core power supply (digital)                     |  |  |  |

| 11  | TMS <sup>1</sup>    | JTAG    | Test Mode Select                                      |  |  |  |

**Note 1:** Pull-up resistor required.

**2:** Pull-down resistor required.

| Pin Name |                     | HW Port | Description                                                                                                                                                                                                                                                         |  |  |  |  |

|----------|---------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 12       | TDO <sup>1</sup>    | JTAG    | Test Data Output                                                                                                                                                                                                                                                    |  |  |  |  |

|          | DINT <sup>1</sup>   |         | Debug Interrupt (active low)                                                                                                                                                                                                                                        |  |  |  |  |

| 13       | TDI <sup>1</sup>    | JTAG    | Test Data Input                                                                                                                                                                                                                                                     |  |  |  |  |

|          | DSDA <sup>1</sup>   |         | Debug Data                                                                                                                                                                                                                                                          |  |  |  |  |

|          | TCK <sup>1</sup>    | JTAG    | Test Clock Input                                                                                                                                                                                                                                                    |  |  |  |  |

| 14       | DSCL <sup>1</sup>   |         | Debug Clock                                                                                                                                                                                                                                                         |  |  |  |  |

| 15       | RST                 |         | Hardware Reset Input (active low). (Pull-up resistor to <b>VDDPn</b> supply should be used when not driven high by an external device. A series resistor should be used in lieu of the pull-up when always driven by an external device.)                           |  |  |  |  |

| 16       | GP10                | GPIO    | General Purpose Input/Output 10                                                                                                                                                                                                                                     |  |  |  |  |

| 17       | GP13                | GPIO    | General Purpose Input/Output 13                                                                                                                                                                                                                                     |  |  |  |  |

| 18       | PWROFF <sup>1</sup> |         | External Power Management Power-Down Indicator. This pin is driven low by INIC after initialization. When high, indicates that the INIC Processor is ready to be shut down. A pull-up resistor is required when used. If not used, this pin ma be left unconnected. |  |  |  |  |

| 19       | MUTE <sup>1</sup>   |         | Mute Indicator Output. A pull-up resistor is required when used. If not used, this pin may be left unconnected.                                                                                                                                                     |  |  |  |  |

|          | GP8                 | GPIO    | General Purpose Input/Output 8                                                                                                                                                                                                                                      |  |  |  |  |

|          | ERR                 | Network | Network Error Indicator Output. This pin is driven high when the network is unlocked. When low, this pin indicates the INIC is locked to the network.                                                                                                               |  |  |  |  |

| 20       | BOOT <sup>1</sup>   |         | Configuration Pin. This pin is attached to the configuration/debug header and used by the Microchip <i>INICkit Tool</i> to load initial configuration data into INIC. Ma also be connected to the EHC to allow in-system configuration of the INIC.                 |  |  |  |  |

| 21       | VDDC2               |         | 1.8 V core power supply (digital)                                                                                                                                                                                                                                   |  |  |  |  |

| 22       | VDDP2               |         | 3.3 V periphery power supply (digital)                                                                                                                                                                                                                              |  |  |  |  |

| 23       | BTXP                | Network | Positive (differential) bPHY network transmitter output                                                                                                                                                                                                             |  |  |  |  |

| 24       | BTXN                | Network | Negative (differential) bPHY network transmitter output                                                                                                                                                                                                             |  |  |  |  |

| 25       | VDDAU1              |         | 3.3 V continuous power supply (analog)                                                                                                                                                                                                                              |  |  |  |  |

| 26       | VDDE18              |         | 1.8 V bPHY power supply (analog)                                                                                                                                                                                                                                    |  |  |  |  |

| 27       | VDDE33              |         | 3.3 V bPHY power supply (analog)                                                                                                                                                                                                                                    |  |  |  |  |

| 28       | BRST                | Network | Hardware Reset Input (active low) for the Balanced Media Physical Layer. Whe asserted, the transmitter output is disabled.                                                                                                                                          |  |  |  |  |

| 29       | BRXN                | Network | Negative (differential) bPHY network receiver input                                                                                                                                                                                                                 |  |  |  |  |

| 30       | BRXP                | Network | Positive (differential) bPHY network receiver input                                                                                                                                                                                                                 |  |  |  |  |

| 31       | NC                  |         | No Connect. This pin must be left open and floating.                                                                                                                                                                                                                |  |  |  |  |

| 32       | VDDAU2              |         | 3.3 V continuous power supply (analog)                                                                                                                                                                                                                              |  |  |  |  |

| 33       | VDDA33              |         | 3.3 V power supply (analog)                                                                                                                                                                                                                                         |  |  |  |  |

| 34       | VDDA18              |         | 1.8 V power supply (analog)                                                                                                                                                                                                                                         |  |  |  |  |

| 35       |                     |         | bPHY Network Activity Status Output:                                                                                                                                                                                                                                |  |  |  |  |

|          | BSTATUS             | Network | - Driven low when a valid signal is detected                                                                                                                                                                                                                        |  |  |  |  |

|          |                     |         | - Driven high to VDDAUn when a qualified signal is not present                                                                                                                                                                                                      |  |  |  |  |

| 36       | ХТО                 |         | Crystal Oscillator Output                                                                                                                                                                                                                                           |  |  |  |  |

| 37       | XTI                 |         | Crystal Oscillator Input or External CMOS Clock Input                                                                                                                                                                                                               |  |  |  |  |

|          | PS0                 | 1       | External Power Management Status Bit 0                                                                                                                                                                                                                              |  |  |  |  |

| 38       | GP1                 | GPIO    | General Purpose Input/Output 1                                                                                                                                                                                                                                      |  |  |  |  |

# TABLE 1-1: OS81210 PIN ALLOCATION TABLE (CONTINUED)

**Note 1:** Pull-up resistor required.

2: Pull-down resistor required.

| TABLE 1 | -1: OS812          | 10 PIN ALL       | OCATION TABLE (CONTINUED)                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin     | Name               | HW Port          | Description                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 39      | PS1                |                  | External Power Management Status Bit 1                                                                                                                                                                                                                                                                                                                  |  |  |  |

|         | GP2                | GPIO             | General Purpose Input/Output 2                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 40      | GP12               | GPIO             | General Purpose Input/Output 12                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 41      | GP14               | GPIO             | General Purpose Input/Output 14                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 42      | VDDC3              |                  | 1.8 V core power supply (digital)                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 43      | VDDP3              |                  | 3.3 V periphery power supply (digital)                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 44      | STROBE             | USB              | Strobe line for HSIC physical interface. Connect to GND when HSIC is not used.                                                                                                                                                                                                                                                                          |  |  |  |

| 45      | DATA               | USB              | Data line for HSIC physical interface. Connect to GND when HSIC is not used.                                                                                                                                                                                                                                                                            |  |  |  |

| 46      | VDD12              |                  | 1.2 V power supply for HSIC physical interface transceiver. Connect to GND through a 1 k $\Omega$ resistor when HSIC is not used.                                                                                                                                                                                                                       |  |  |  |

| 47      | DM                 | USB              | Negative (differential) data line for USB physical interface. Connect to GND when the USB physical interface is not used.                                                                                                                                                                                                                               |  |  |  |

| 48      | DP                 | USB              | Positive (differential) data line for USB physical interface. Connect to GND when the USB physical interface is not used.                                                                                                                                                                                                                               |  |  |  |

| 49      | VDDUSB33           |                  | 3.3 V USB power supply (analog)                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 50      | RBIAS <sup>2</sup> | USB              | Connect to GND through a 12 k $\Omega$ resistor (0.5 %, 1/16 W, $\leq \pm$ 100 ppm). This pi may be left unconnected when both the USB and HSIC physical interfaces are not used.                                                                                                                                                                       |  |  |  |

| 51      | VDDUSB18           |                  | 1.8 V USB power supply (analog)                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 52      | VBUS               | USB              | USB Bus Power State Indicator Input. The application should drive this pin high when an external USB Host Controller is present. Note that this pin is not 5 V to erant and must not be connected directly to USB bus power. This signal is ignored when using the HSIC physical interface. Connect to GND when the USI physical interface is not used. |  |  |  |

| 53      | RMCK               | RMCK             | Recovered Master Clock Output                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 54      | INT <sup>1</sup>   | l <sup>2</sup> C | Interrupt (active low). Indicates a service request from the EHC when the Contro<br>Port is operating as an $I^2C$ slave.                                                                                                                                                                                                                               |  |  |  |

|         | GP0                | GPIO             | General Purpose Input/Output 0                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 55      | SCL <sup>1</sup>   | l <sup>2</sup> C | Clock                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 56      | SDA <sup>1</sup>   | l <sup>2</sup> C | Data                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 57      | VDDC4              |                  | 1.8 V core power supply (digital)                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 58      | VDDP4              |                  | 3.3 V periphery power supply (digital)                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 59      | FSYA               | Streaming        | Frame Sync for Streaming Port A and B                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 60      | SCKA               | Streaming        | Bit Clock for Streaming Port A and B                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 61      | SRXA0              | Streaming        | Data I/O Signal 0 for Streaming Port A                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 62      | SRXA1              | Streaming        | Data I/O Signal 1 for Streaming Port A                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 63      | SRXB0              | Streaming        | Data I/O Signal 0 for Streaming Port B                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 64      | SRXB1              | Streaming        | Data I/O Signal 1 for Streaming Port B                                                                                                                                                                                                                                                                                                                  |  |  |  |

| ePAD    | GND                |                  | The exposed paddle on the bottom side of the QFN package is the primary ground for the OS81210 and must be connected to ground on the PCB for proper operation.                                                                                                                                                                                         |  |  |  |

Note 1: Pull-up resistor required.

2: Pull-down resistor required.

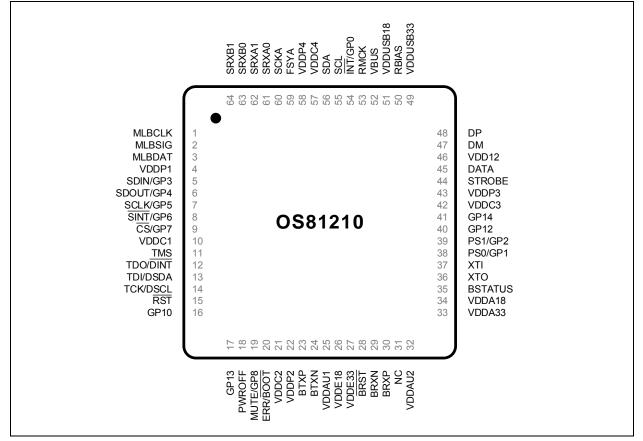

# 2.0 BASIC APPLICATION INFORMATION

The OS81210 and OS81212/4/6 INICs are part of the OS8121x 50 Mbit/s INICnet product family that support point-topoint, simplex daisy chain, and ring topologies through an integrated balanced media physical layer (bPHY). The integrated *INIC Software Stack* can independently run the network and manage the low-level protocols such as startup, shutdown, error reporting, or Plug-and-Play node positioning. Alternatively, INIC can operate in conjunction with an External Host Controller (EHC) managing the mid- and high-level functions. Additionally the OS81210 provides power management capabilities and industry standard application interfaces such a USB 2.0, MediaLB 3-Pin, Streaming Port, I<sup>2</sup>C Port, SPI port, and GPIOs.

The OS81210 is optimized for high performance head unit applications with USB 2.0 or HSIC high-speed communication.

The OS81212 is targeted for audio / video streaming data applications with the dual Streaming Ports and MediaLB interface. It can operate with an EHC or it can exist remotely on the network.

The OS81214 is targeted for audio data applications using the Streaming Port or packets over the SPI Port. It can operate with an EHC or it can exist remotely on the network.

The OS81216 INIC is targeted for remotely configured microphone applications (without a local EHC).

#### FIGURE 2-1: OS8121x PRODUCT FAMILY OVERVIEW

Figure 2-2 depicts an example 50 Mbit/s INICnet application. Using a combination of OS81210 and OS81212/4/6 INICs, a system supporting audio, video, and packet data applications can be easily configured. The Head Unit INIC can communicate with an operating system (such as a GNU/Linux, QNX, Android Auto, etc.) to manage the network and control the remote nodes. The asynchronous channel on the INIC can be used for high-speed routing of application packet data such as graphics images, system information, or software downloads. The EHC can access both synchronous and packet data through the OS81210 USB interface. An Instrument Panel can be implemented with control and Ethernet packets sent over the OS81210/2 MediaLB Port. Without a local EHC, the microphones are configured remotely over I<sup>2</sup>C. Only a single INIC streaming pin is used to source a mono PDM bit stream from a MEMS microphone to the network. As shown in the Remote Amp, the amplifier is remotely controlled and configured. Synchronous audio data is routed over the network and is sourced/sinked through I<sup>2</sup>S to CODECs or DSPs. The Rear Seat Entertainment (RSE) can route synchronous streams or asynchronous data such a IP packets over the network Ethernet Channel.

## FIGURE 2-2: BASIC APPLICATION DIAGRAM

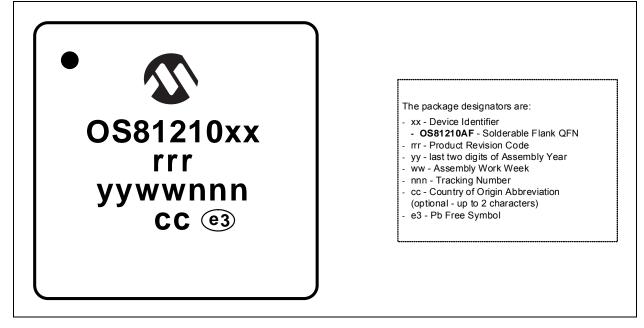

# 3.0 PACKAGING INFORMATION

## 3.1 Package Marking

#### FIGURE 3-1: OS81210 TOP MARKING

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO. X<br>   <br>Device Grade      | <u>X</u><br> <br>Package<br>Type | [X] -<br> <br>Tape and<br>Reel Flag | rrr<br> <br>Product<br>Revision<br>Code | VVVVV<br>Firmware<br>Revision<br>Code | [ss]<br> <br>Firmware<br>Service<br>Release | - [xxx]<br> <br>Special<br>Feature<br>Code |  |

|----------------------------------------|----------------------------------|-------------------------------------|-----------------------------------------|---------------------------------------|---------------------------------------------|--------------------------------------------|--|

| Device                                 | OS81210                          | = 50 Mbi<br>Contro                  | t/s Automo                              | tive Intellige<br>B                   | nt Network I                                | nterface                                   |  |

| Grade                                  | A                                | = All Fea                           | atures                                  |                                       |                                             |                                            |  |

| Package Type                           | F                                | = QFN w                             | vith soldera                            | ble flanks                            |                                             |                                            |  |

| Tape and Reel<br>Flag (optional)       | Blank<br>R                       | = Standa<br>= Tape a                |                                         | ng (Tube/Tr                           | ay)                                         |                                            |  |

| Product Revision<br>Code               | rrr                              | = 3 char                            | acter code                              | specifying p                          | roduct revisi                               | ion                                        |  |

| Firmware Revision<br>Code              | vvvvv                            | = 6 char                            | acter code                              | specifying fi                         | rmware revi                                 | sion                                       |  |

| Firmware Service<br>Release (optional) | SS                               | = 2 char                            | acter code                              | specifying s                          | ervice releas                               | se                                         |  |

| Special Feature<br>Code (optional)     | ххх                              | = 3 char                            | acter code                              | for special re                        | equirements                                 | i                                          |  |

# OS81210

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL00® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV — ISO/TS 16949—

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELoo, KEELoo logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2017-19, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-4061-1

# Worldwide Sales and Service

#### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

#### Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston** Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733 China - Beijing

Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138 China - Zhuhai Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

Japan - Osaka Tel: 81-6-6152-7160

Japan - Tokyo Tel: 81-3-6880- 3770

Korea - Daegu Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore Tel: 65-6334-8870

Taiwan - Hsin Chu Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

Taiwan - Taipei Tel: 886-2-2508-8600 Thailand - Bangkok

Tel: 66-2-694-1351 Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Spain - Madrid

Sweden - Gothenberg

Sweden - Stockholm Tel: 46-8-5090-4654

UK - Wokingham Tel: 44-118-921-5800 Fax: 44-118-921-5820

EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

Germany - Haan Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

Germany - Munich Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Romania - Bucharest Tel: 40-21-407-87-50

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Tel: 46-31-704-60-40