# InGaP HBT 5GHz 802.11ac Power Amplifier

### Description

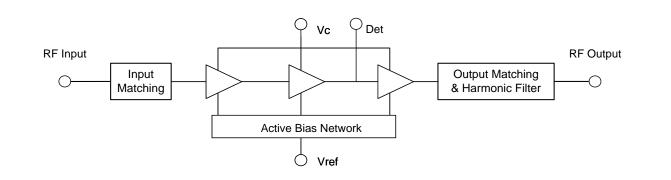

The LX5531 is a power amplifier optimized for 802.11ac/a/n applications in the 5.15-5.85GHz frequency range. The LX5531 includes a three-stage PA, active bias, input/output matching, and a harmonic filter.

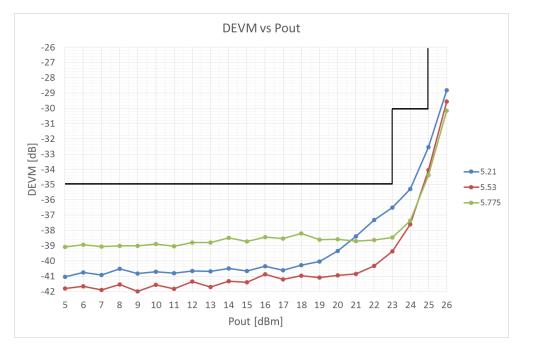

The power amplifier operates with a single positive voltage supply of 5V, and provides power gain of 32dB and output powers of 23 and 25dBm at 5V across the frequency band for -35 and -30dB dynamic EVM (DEVM), respectively. It is fully matched to 50 Ohms on both the input and output ports.

The 2nd and 3rd harmonics are below -45dBm/MHz over the frequency band due to an integrated harmonic filter. The LX5531 also features an on-chip power detector to help reduce BOM cost and PCB space for implementation of power control in a typical wireless system.

The LX5531 is available in a 20-pin 4mm x 4mm quad flat no lead package (QFN  $4\times4-20L$ ). The compact footprint, low profile, and excellent thermal capability make the LX5531 an ideal solution for 802.11ac/a/n applications.

#### Features

- 5.15-5.85GHz Operation

- Single-Polarity 5V Supply

- Power Gain ~ 32dB

- 23dBm @ -35dB DEVM for 802.11ac

- 25dBm @ -30dB DEVM for 802.11a

- <-45dBm/MHz for 2nd Harmonic at 23 dBm</p>

- <-45dBm/MHz for 3rd Harmonic at 23 dBm</li>

- Complete Input and Output Match

- On-Chip Output Power Detector

- Small Footprint: 4mm x 4mm

- Low Profile: 0.9mm

- RoHS Compliant & Halogen Free

### Applications

802.11ac/a/n Access Points, Media Gateways, Set-top Boxes, and other Tripleplay Multimedia Devices.

## **Block Diagram**

Figure 1 - Functional Block Diagram

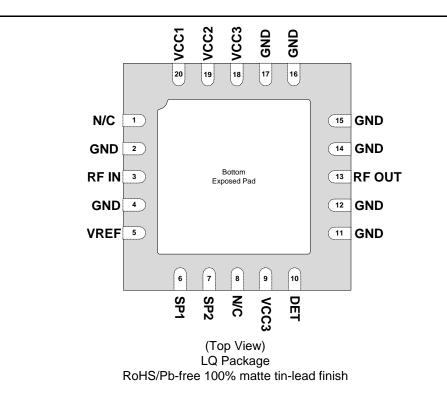

# **Pin Configuration**

| Figure 2 · Pinout (Top View) |                                     |    |                     |  |

|------------------------------|-------------------------------------|----|---------------------|--|

| Top mark                     | •MSC                                |    | •MSC                |  |

|                              | 5531                                | OR | 5531                |  |

|                              | YYWWA = Year/Week/Lot<br>Identifier |    | YWWNNN = Trace code |  |

# **Ordering Information**

| Ambient<br>Temperature | Туре                        | Package        | Ordering Part Number | Packaging Type |

|------------------------|-----------------------------|----------------|----------------------|----------------|

| 0°C to 70°C            | RoHS2 compliant,<br>Pb-free | QFN 4x4<br>20L | LX5531LQ-TR          | Tape and Reel  |

# Pin Description

| Pin Number                | Pin Designator | Description                                                                                                                                                              |  |  |

|---------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 8                      | N/C            | These pins are unused and not connected to the device inside the package.<br>They can be treated either as open pins, or connected to ground for better heat dissipation |  |  |

| 2,4,11,12,<br>14,15,16,17 | GND            | Ground.                                                                                                                                                                  |  |  |

| 3                         | RF IN          | RF input into the power amplifier. This pin is RF-matched to 50 Ohm, and shorted to ground at DC.                                                                        |  |  |

| 5                         | VREF           | PA enable voltage.                                                                                                                                                       |  |  |

| 6                         | SP1            | Port for optional resistor and capacitor for DEVM optimization.                                                                                                          |  |  |

| 7                         | SP2            | Port for optional resistor and capacitor for DEVM optimization.                                                                                                          |  |  |

| 9, 18                     | VCC3           | Power supply for the third stage of the amplifier.                                                                                                                       |  |  |

| 10                        | DET            | Detector output.                                                                                                                                                         |  |  |

| 13                        | RF OUT         | RF output of the power amplifier. This pin is RF-matched to 50 Ohm, and shorted to ground at DC.                                                                         |  |  |

| 19                        | VCC2           | Power supply for the second stage of the amplifier.                                                                                                                      |  |  |

| 20                        | VCC1           | Power supply for the first stage of the amplifier.                                                                                                                       |  |  |

| Center<br>Metal           | GND            | The center metal base of the QFN package provides DC and RF ground as well as the heat sink for the power amplifier.                                                     |  |  |

## Absolute Maximum Ratings

| Parameter                                                         | Value          | Units |

|-------------------------------------------------------------------|----------------|-------|

| DC Supply Voltage, RF off                                         | -0.3 to 6      | V     |

| Collector Current                                                 | 900            | mA    |

| Total Power Dissipation                                           | 5.5            | W     |

| CW or OFDM RF Input Power (With 50 Ohm Load at Output)            | +9             | dBm   |

| Maximum Junction Temperature (T <sub>J MAX</sub> )                | 150            | °C    |

| Operation Ambient Temperature (T <sub>A</sub> )                   | 0 to 70        | °C    |

| Storage Temperature                                               | -65 to 150     | °C    |

| Peak Package Temp. for Solder Reflow<br>(40 seconds max exposure) | +260°C (+0,-5) | °C    |

| Electrostatic Discharge<br>Human Body Model(HBM), Class 1A        | 500            | V     |

Note: Although this device is designed to be as robust as possible, Electrostatic Discharge (ESD) can damage this device. This device must be protected at all times from ESD. Static charges may easily produce potentials of several kilovolts on the human body or equipment, which can discharge without detection. Industry-standard ESD precautions should be used at all times.

Exceeding any Absolute Maximum ratings could cause damage to the device. All voltages are with respect to GND. Currents are positive into, negative out of specified terminal. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" are not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

## **Thermal Properties**

| Thermal Resistance                    | Тур  | Units |

|---------------------------------------|------|-------|

| $\theta_{JP}$ Junction to exposed pad | 35.5 | °C/W  |

| $\theta_{JA}$ Junction to ambient     | 68.0 | °C/W  |

Note: The  $\theta$ Jx numbers assume no forced airflow. Junction Temperature is calculated using  $T_J = T_A + (Power dissipation x \theta_{JA})$ .  $\theta_{JA}$  is a function of the PCB construction. The stated number above is calculated with a four-layer board in accordance with JESD-51 (JEDEC). Note that an external heat sink will be required at elevated temperatures and at high output powers to ensure that the maximum junction temperature of 150°C is not exceeded.

## **Recommended Operating Conditions**

|                            | Min | Мах | Units |

|----------------------------|-----|-----|-------|

| VCC                        | 3.0 | 5.5 | V     |

| Case Operating Temperature | 0   | 70  | °C    |

## **Electrical Characteristics**

| Symbol                             | Parameter                                                            | Test Condition                                                                                                | Min         | Тур       | Max        | Units   |

|------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------|-----------|------------|---------|

|                                    | se specified under conditions, all<br>85V, as measured on the evalua | ratings stated below apply at 25C over the tion board.                                                        | e entire fr | equency b | oand, with | VCC=5V  |

| 802.11ac/a/n                       | Data                                                                 |                                                                                                               |             |           |            |         |

| F                                  | Frequency Range                                                      |                                                                                                               | 5.15        |           | 5.85       | GHz     |

| S11                                | Input Return Loss                                                    |                                                                                                               |             | -25       | -12        | dB      |

| S22                                | Output Return Loss                                                   |                                                                                                               |             | -14       | -7.5       | dB      |

| S12                                | Reverse Isolation                                                    |                                                                                                               |             | -50       |            | dB      |

| S21                                | Small Signal Gain                                                    |                                                                                                               | 30          | 33        | 37         | dB      |

| ∆G80                               | Gain flatness over channel                                           | Across 80MHz                                                                                                  |             | 0.2       | 0.5        | dB      |

| ΔG                                 | Gain flatness over band                                              | Across the entire band                                                                                        |             | +/-1.5    |            | dB      |

| lcq                                | Quiescent Current                                                    |                                                                                                               |             | 160       |            | mA      |

| Iref                               | Bias Control Reference<br>Current                                    | @ Icq=160mA                                                                                                   |             | 16        | 18         | mA      |

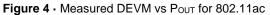

| lc                                 | Total Current<br>@Pout=23dBm                                         | 802.11ac, 256QAM MCS9, VHT80, 59 symbols, 50% duty cycle                                                      |             | 290       | 320        | mA      |

|                                    | Total Current<br>@Pout=25dBm                                         | 802.11a, 64QAM, 54Mbps, 59<br>symbols, 50% duty cycle                                                         |             | 350       | 380        | mA      |

|                                    | Idle current                                                         | Vref=0V, No RF                                                                                                |             | 0.1       |            | μA      |

| DEVM                               | DEVM at 23 dBm output<br>power                                       | 802.11ac, 256QAM MCS9, VHT80, 59 symbols, 50% duty cycle                                                      |             | -38       | -35        | dB      |

|                                    | DEVM at 25 dBm output<br>power                                       | 802.11a, 64QAM, 54Mbps, 59<br>symbols, 50% duty cycle                                                         |             | -36       | -30        | dB      |

| 2Fo                                | Second Harmonic                                                      | P <sub>OUT</sub> =25dBm, 802.11a, 64QAM,<br>6Mbps, 100% duty cycle                                            |             | -50       | -45        | dBm/MHz |

| 3Fo                                | Third Harmonic                                                       | Pout =25dBm, 802.11a, 64QAM,<br>6Mbps, 100% duty cycle                                                        |             | -50       | -45        | dBm/MHz |

| t <sub>on</sub> / t <sub>off</sub> | Turn on or turn-off Time                                             | 10-90% / 90-10% of final power                                                                                |             | 0.5       |            | μs      |

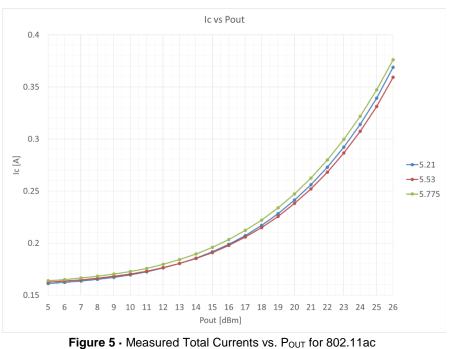

|                                    | Detector RMS output<br>voltage with no RF input<br>signal applied.   | No RF input signal.                                                                                           | 75          | 200       | 325        | mV      |

| Vdet <sub>rms</sub>                | Detector RMS output<br>voltage with 27dBm output<br>power.           | Detector voltage is measured<br>during the first 16us of the<br>preamble using the L-STF and<br>L-LTF fields. | 500         | 625       | 750        | mV      |

| PDZout                             | Detector output impedance                                            |                                                                                                               |             | 2.6       |            | kOhms   |

| Ruggedness                         |                                                                      | P <sub>IN</sub> =-2dBm, CW, VSWR 6:1, all phases                                                              | No damage   |           |            |         |

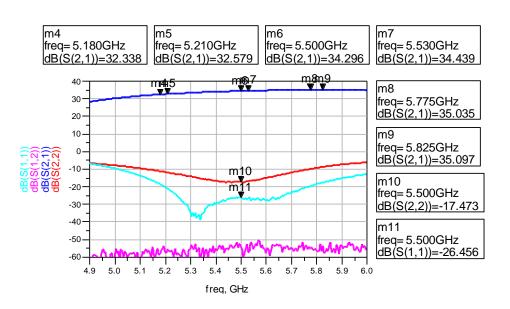

## **Application Performance Curves**

Figure 3 · Measured S-Parameters

VCC1=VCC2=VCC3=5V, VREF=2.85V, and Icq=155mA, 59 symbols, and duty cycle =50%

## **Application Performance Curves**

(VCC1=VCC2=VCC3=5V, VREF=2.85V, and Icq=155mA

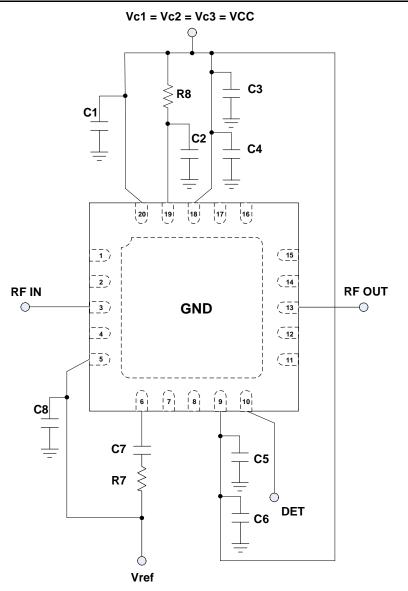

# **Typical Application**

Figure 7 - Typical Application

$$\begin{split} & \text{VCC} = 5\text{V}.\\ & \text{C1} = \text{C2} = 1\mu\text{F} (0402)\\ & \text{C3} = \text{C6} = 10\mu\text{F} (0603)\\ & \text{C4} = \text{C5} = 4.7\mu\text{F} (0402)\\ & \text{C7} = 33n\text{F} (0402)\\ & \text{C8} = 1n\text{F} (0402)\\ & \text{R7} = 845 \text{ Ohms} (0402)\\ & \text{R8} = 15 \text{ Ohms} (0402) \end{split}$$

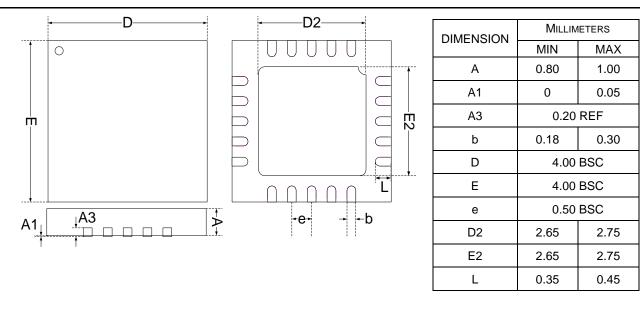

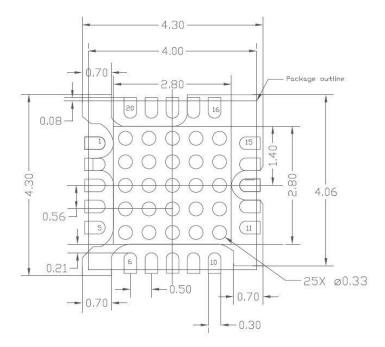

## **Package Outline Dimensions**

The package is halogen free and meets RoHS2 and REACH standards.

Figure 8 · 20L Plastic QFN 4x4mm Exposed Pad Package Dimensions

Figure 9 - PCB Layout Footprint (Top View)

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

© 2019 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.