# Dual Subscriber Line Interface Circuit VE580 Series

#### **FEATURES**

- Dual-Channel SLIC device with small footprint

- Loop start and Ground start support

- +5 V and battery supply required

- Optional dual battery operation

- -39 to -60 V battery operation

- Supplies more than 20 mA into 2000 Ω from -48 V

- Programmable current limit

- On-chip Thermal Management (TMG) feature in all Active states

- Low standby power (24 mW per channel)

- Supports 2.0 Vrms metering applications

- Control states: Active and Active Metering (Normal and Reverse Polarity), Standby, Tip Open and Disconnect

- 3.3-V compatible to logic control inputs

- Power up in Disconnect state

- On-hook transmission in Active states

- Per-channel fault detection and indication

- Per-channel thermal shutdown

- Programmable Off Hook and Ground Start thresholds.

- Programmable ring-trip detect threshold

- Footprint compatible with Microsemi's Le5711 SLIC

#### **APPLICATIONS**

- Ideal for low-cost, high performance line card applications (CO, DLC)

- Meets requirements for countries such as: India, China, Korea, Japan, Taiwan, and Australia

- Meets requirements for North America DLC applications (TR-57-CORE)

### RELATED LITERATURES

- 081110 Thermal Management for the Le5711 and Le5712 SLIC Devices Application Note

- 080900 Le5711 and Le5712 Comparison Brief Application Note

- 080753 Le58QL02/021/031 QLSLAC<sup>TM</sup> Data Sheet

- 080754 Le58QL061/063 QLSLAC<sup>TM</sup> Data Sheet

- 080921 Le58083 Octal SLAC<sup>™</sup> Data Sheet

- 080676 Le5711 Dual SLIC Data Sheet

Document ID#: 081047 Version 8 April 2013

## ORDERING INFORMATION

| Device      | Package Type <sup>1</sup>                         | Packing <sup>2</sup> |

|-------------|---------------------------------------------------|----------------------|

| Le57D121BTC | 44-pin eTQFP (Green),<br>-53 dB, Reverse Polarity | Tray                 |

| Le57D122BTC | 44-pin eTQFP (Green),<br>-63 dB, Reverse Polarity | Hay                  |

- The green package meets RoHS Directive 2002/95/EC of the European Council to minimize the environmental impact of electrical equipment.

- 2. For delivery using a tape and reel packing system, add a "T" suffix to the OPN (Ordering Part Number) when placing an order.

## **DESCRIPTION**

The innovative Le5712 dual-channel SLIC device is designed for high-density POTS applications requiring a small-footprint, low-power SLIC device. By combining a fully featured line interface of two channels into one SLIC device, the Le5712 device enables the design of a low-cost, high performance, and fully programmable line interface for multiple country applications worldwide, including Ground Start and metering capability. The on-chip Thermal Management (TMG) feature allows for significantly reduced power dissipation on the device. Optional dual battery operation to reduce total power consumption is also available. The device is offered in a thermally efficient, space-saving 44-pin eTQFP package. The 12 x 12 mm footprint allows designers to make a dramatic increase in the density of lines on a board. The Le5712 device is also designed to significantly reduce the number of external components required for line card design.

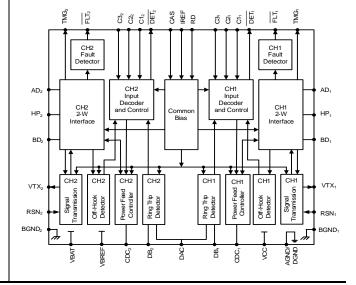

### **BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| Features                                                  |

|-----------------------------------------------------------|

| Applications1                                             |

| Related Literatures1                                      |

| Ordering Information1                                     |

| Description1                                              |

| Block Diagram                                             |

| Table of Contents                                         |

| Product Description                                       |

| Block Descriptions                                        |

| Two-Wire Interface                                        |

| Signal Transmission                                       |

| Power Feed Controller and Common Bias4                    |

| Input Decoder and Control                                 |

| Device State Decoding                                     |

| Off-Hook Detector (OHD)                                   |

| Ground Start Detector (GSD)                               |

| Ring-Trip Detector                                        |

| Fault Detector                                            |

| Thermal Shutdown                                          |

| Connection Diagram                                        |

| Pin Descriptions                                          |

| Absolute Maximum Ratings                                  |

| Operating Ranges                                          |

| Environmental Ranges                                      |

| Electrical ranges                                         |

| Electrical Characteristics                                |

| Summary of Test Conditions                                |

| Supply Currents and Power Dissipation (on-hook)           |

| Specifications9                                           |

| Device specifications                                     |

| DC Feed Characteristics                                   |

| Test Circuits                                             |

| POTS Application Circuit (POTS with no metering)18        |

| Application Circuit Parts List (Pots with no metering)19  |

| Pulse Metering Application Circuit (Pots with metering)20 |

| Application Circuit Parts List (Pots with metering)       |

| Physical Dimensions                                       |

| Revision History                                          |

| Revision C1 to D1                                         |

| Revision D1 to E1                                         |

| Revision E1 to F1                                         |

| Revision F1 to G1                                         |

| Revision G1 to G2                                         |

| Revision G2 (version 7) to Version 8                      |

## PRODUCT DESCRIPTION

The Le5712 device is designed for long loop high-density POTS applications requiring a low power, small footprint SLIC device. The Le5712 device increases line card density by integrating two SLIC devices into a single 44-pin package. This reduction in board space permits a higher density line card, which allows for amortizing common hardware across more channels. The Le5712 device gives line card designers a simple control interface that supports seven states: Active, Active Metering, Reverse Polarity, Reverse Polarity Metering, Standby, Tip Open and Disconnect (Ringing). The low cost and high performance Le5712 device provides the key features for POTS markets requiring loop start, loop start and metering, or ground start. The device includes a thermal management feature for minimizing power dissipation on the SLIC. Alternatively, the device can be operated in a dual battery configuration to reduce overall power consumption.

### **BLOCK DESCRIPTIONS**

### **Two-Wire Interface**

The two-wire interface provides DC current and sends voice and signalling information to a customer premise equipment. The two-wire interface also receives the returning signals from the customer premise equipment.

This block implements the thermal management feature, which allows power that would otherwise be dissipated within the package to be off loaded into an external resistor when the line is Off Hook. R<sub>TMGi</sub> is connected from TMG<sub>i</sub> to the VBAT pin and limits power within the SLIC device (Note: "i" denotes channel number).

The minimum value of R<sub>TMGi</sub> is given by:

$$R_{TMG} \ge \frac{\left|BAT_{MAX}\right| - 6 - I_{LIMITMIN} \cdot (2 \bullet R_F + R_{LMIN} + 40\Omega)}{I_{LIMITMIN} - 3 \text{ mA}}$$

where  $I_{LIMITMIN}$  is the minimum programmed loop current limit and  $R_{LMIN}$  is the minimum loop resistance. The tolerance of  $R_{TMG}$  should be taken into account when selecting a value that meets this requirement. For example, if  $BAT_{MAX} = -56 \text{ V}$ ,  $I_{LOOPMIN} = 30 \text{ mA}$  and  $R_{LMIN} = 200 \Omega$  then  $R_{TMG} = 1.5 \text{ k}\Omega$  is the minimum recommended value. A value of 1.8 k $\Omega$  with 5% accuracy will keep the power in  $R_{TMG}$  below 1.0 W, and the total worst case SLIC power dissipation with both channels active below 1.6 W.

The power dissipated in the TMG resistor is given by:

$$\mathsf{P}_{\mathsf{RTMG}} = \frac{\left(\left|\mathsf{BAT}\right| - 5 - \mathsf{I}_{\mathsf{L}} \bullet \left(\mathsf{R}_{\mathsf{L}} + 2\mathsf{R}_{\mathsf{F}} + 40\right)\right)^{2}}{\mathsf{R}_{\mathsf{TMG}}}$$

where  $I_L$  is the loop current, and  $R_L$  is the loop resistance.

The maximum power on R<sub>TMG</sub> is given by:

$$\mathsf{P}_{\mathsf{RTMGmax}} = \frac{\left(\left|\mathsf{BAT}\right|_{\mathsf{max}} - 5 - \mathsf{I}_{\mathsf{LIMITmin}} \left(\mathsf{R}_{\mathsf{Lmin}} + 2\mathsf{R}_{\mathsf{F}} + 40\right)\right)^2}{\mathsf{R}_{\mathsf{TMGmin}}}$$

And the power dissipated per channel in the SLIC device while in the Active states is given by:

$$\mathsf{P_{SLICi}} = 0.003 |BAT| + (|BAT| - 3 - I_L(R_L + 2R_F + 40)) \Big( I_L - \frac{I}{R_{TMG}} (|BAT| - 5 - I_L(R_L + 2R_F + 40)) \Big)$$

The maximum power dissipated per channel in the SLIC device while in the Active states is given by:

$$\mathsf{P}_{\mathsf{SLIC}\mathsf{max}i} = 0.003 \big| \mathsf{BAT} \big|_{\mathsf{max}} + \left( 1 + \frac{\mathsf{I}_{\mathsf{LIMIT}\mathsf{max}}}{2} \mathsf{R}_{\mathsf{TMG}\mathsf{max}} \right) \left( \frac{\mathsf{I}_{\mathsf{LIMIT}\mathsf{max}}}{2} + \frac{1}{\mathsf{R}_{\mathsf{TMG}\mathsf{max}}} \right)$$

Refer to the *Thermal Management for the Le5711 and Le7512 Dual SLIC Devices Application Note* for further analysis and for dual battery condition.

The AC signal swing supported by the two-wire interface is controlled by the SLIC state. For standard voice transmission, the Active and Reverse Polarity states are used. To support voice plus meter pulses, the Active Metering and Reverse Polarity Metering states are provided which have increased overhead to support 2.0 Vrms metering.

## **Signal Transmission**

The RSN<sub>i</sub> input current controls the receive current sent to the two-wire interface. The AC line voltage is sensed by a differential amplifier between the AD<sub>i</sub> and HP<sub>i</sub> leads. The output of this amplifier is equal to the AC metallic components of the line voltages and is output at VTX<sub>i</sub>.

The desired two-wire AC input impedance, Z<sub>2WIN</sub>, is defined by the fuse resistors, R<sub>F</sub>, and an impedance connected from VTX<sub>i</sub> to RSN<sub>i</sub>, Z<sub>Ti</sub>. When computing Z<sub>Ti</sub>, the internal current amplifier pole and any external stray capacitance between VTX and RSN must be taken into account.

$$Z_{Ti} = \frac{500}{3} \cdot (Z_{2WIN} - 2R_F)$$

To set the desired receive gain (G<sub>42L</sub>) into a load Z<sub>L</sub> from VRX<sub>i</sub>, Z<sub>RXi</sub> is connected from VRX<sub>i</sub> to RSN<sub>i</sub>, where

$$Z_{RXi} = \frac{Z_L}{G_{42L}} \bullet \frac{500 \bullet Z_T}{Z_T + \frac{500}{3}(Z_L + 2R_F)}$$

The transmission block also contains a longitudinal feedback circuit to shunt longitudinal signals to a DC bias voltage. The longitudinal feedback does not affect metallic signals.

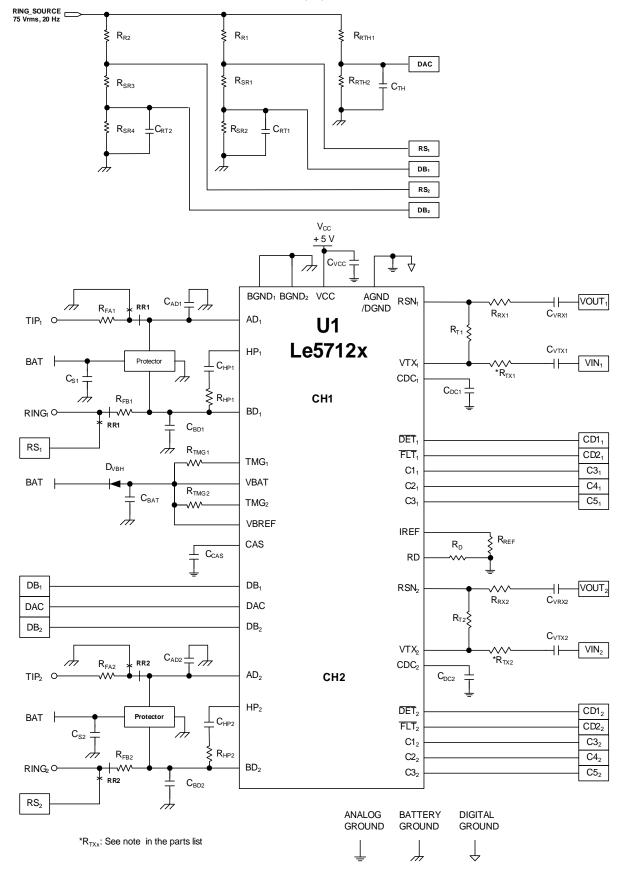

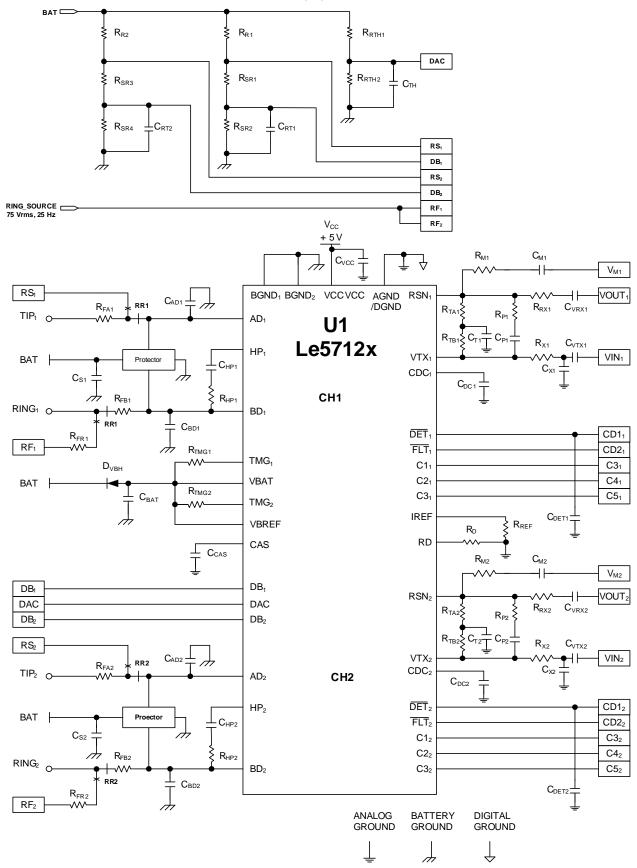

Two application circuits, provided at the end of this data sheet, show how the Le5712 device can connect directly to pins of a QLSLAC codec.

The POTS Application Circuit (POTS with no metering), on page 18 shows an application providing Loop Start and Ground Start capability. The components selected for the transmission network allow a wide range of market transmission requirements to be met when combined with the programmable QLSLAC device. In addition, transmit relative levels of Li = +4 to -4 dBr and receive relative levels of Lo = 0 to -8dBr can be supported using only the digital gain within the QLSLAC device for all markets. This configuration will meet ITU Q.552 and GR57 requirements.

The Pulse Metering Application Circuit (Pots with metering), on page 20 shows a configuration for use in a 12 or 16 kHz pulse metering application with the QLSLAC device. The design allows 2 Vrms into 200 Ω, and supports gain ranges of at least Li = 0 to +4dBr, and Lo = 0 to -8 dBr. This configuration will meet ITU Q.552 requirements over these gain ranges for markets such as India and China.

The relationship between metering source  $V_M$ , the feeding resistance,  $R_M$ , and the output voltage at tip-ring,  $V_{TR}$ , is given in the following equation. The load at tip-ring is R<sub>M</sub>. R<sub>F</sub> is the protection and other, if any, front-end resistances. Z<sub>T</sub> is the impedance between VTX and RSN at metering frequency.

$$V_{TR} = \frac{Z_{M}}{R_{M}} \bullet \frac{500}{1 + \frac{500}{3} \bullet \frac{Z_{M} + 2R_{F}}{Z_{T}}} V_{M}$$

Metering signal at VTX needs to be filtered to prevent from overloading the codec. This has been realized in the applications circuitry in this document.

### **Power Feed Controller and Common Bias**

The power feed controllers have three sections: (1) the common bias circuit, (2) the battery feed circuit, and (3) the reverse polarity circuit which operate in all Active states.

The bias circuit provides a signal which sets the current limit and creates a voltage related to V<sub>BAT</sub>, filtered by a capacitor connected to the CAS pin, to the battery feed circuit.

The nominal current limit is set by the following equation:  $I_{LIMIT} = \frac{470}{R_{RFF}}$

$$I_{LIMIT} = \frac{470}{R_{RFF}}$$

A recommended 3 Hz filter pole frequency (f<sub>c</sub>) can be implemented from:  $C_{CAS} = \frac{1}{RI_{\Delta S} \cdot 2 \cdot \pi \cdot f_{c}}$

$$C_{CAS} = \frac{1}{RI_{AS} \cdot 2 \cdot \pi \cdot f_0}$$

The battery feed circuit regulates the amount of DC current and voltage supplied to the telephone over a wide range of loop resistance. It is designed to operate over a nominal 22 to 33 mA range of programmed current limit. It produces a filtered reference voltage offset from the subscriber line voltage which is applied to the two-wire interface.

In addition, a low pass filter is implemented with a capacitor connected to the CDC<sub>i</sub> pin.

In the low power Standby state, an alternative feed is implemented via two current limited on chip  $200-\Omega$  resistors. The nominal loop current below current limit in the Standby state is given by:

$$I_{STANDBY} = \frac{|V_{BAT}| - 4 V}{600 \Omega + R_{I}}$$

## **Input Decoder and Control**

The input decoder and control block provides a means for a microprocessor or SLAC device IC to control such system states as Active, Active Metering, Reverse Polarity, Reverse Polarity Metering, Standby, Tip Open and Disconnect (Ringing). The input decoder and control block has TTL-compatible inputs, permitting interfacing to 5 or 3.3 V VCC controllers which set the operating states of the SLIC device. It also provides the loop supervision signal sent back to the controller.

From power up, the device is in disconnect state unless over-written by external control inputs.

## **Device State Decoding**

(For channel i = 1 or 2)

| State | C3 <sub>i</sub> | C2 <sub>i</sub> | C1 <sub>i</sub> | Two-Wire state            | DET <sub>i</sub> output |

|-------|-----------------|-----------------|-----------------|---------------------------|-------------------------|

| 0     | 0               | 0               | 0               | Reserved                  | N/A                     |

| 1     | 0               | 0               | 1               | Active Metering           | OHD                     |

| 2     | 0               | 1               | 0               | Tip Open                  | GSD                     |

| 3     | 0               | 1               | 1               | Reverse Polarity Metering | OHD                     |

| 4     | 1               | 0               | 0               | Disconnect                | RTD                     |

| 5     | 1               | 0               | 1               | Active                    | OHD                     |

| 6     | 1               | 1               | 0               | Standby                   | OHD                     |

| 7     | 1               | 1               | 1               | Reverse Polarity          | OHD                     |

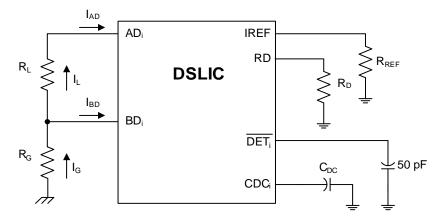

## Off-Hook Detector (OHD)

The On-to-Off-hook and Off-to-On-hook detections are based on loop current and are defined as  $|I_{AD} - I_{BD}| / 2$ . The On-to-Off-hook (OHD) and Off-to-On-hook (OND) thresholds are programmed with the  $R_D$  resistor and the threshold applies to all Active and Standby states.

$$I_{OHD} = \frac{935 \text{V}}{\text{R}_{D}}$$

$$I_{OHD} = I_{OND} + \text{Hysteresis}$$

Upon the loss of battery the DET pin will be HIGH.

Off-hook detection or DET state should be ignored during on-hook metering.

## **Ground Start Detector (GSD)**

This detector is active in the Tip Open state. The threshold, I<sub>GSD</sub>, is defined by the same equation used for the OHD.

For ground start lines, the device is in the Tip Open state between calls. When a ring ground condition is detected, the device should be switched to the Active state. During this period, the DET pin will be active if the ring to ground current is greater than twice the I<sub>OHD</sub> threshold. The DET pin will go active once the ring ground is removed and a loop is applied. It is recommended that a firmware time-out period is applied in case the call attempt is abandoned and DET never goes low. The time-out is reset once an active DET is seen in the Active state.

# **Ring-Trip Detector**

In the Disconnect state, the ring-trip detector is active. While the  $DB_i$  pin is more negative than the DAC pin, the  $\overline{DET}$  pin will be High to indicate on hook. When an off hook condition occurs, the  $DB_i$  pin becomes more positive than the DAC pin, and the  $\overline{DET}$  pin will go Low to indicate off hook during ringing (ring-trip) has been detected. The system implements the Ringing state using external control of a ring relay in combination with the Disconnect SLIC device state, which enables the ring-trip detector.

The <u>POTS Application Circuit (POTS with no metering)</u>, on page 18 shows a ring trip bridge configured and components are selected for a typical battery-backed ringing applications such as for the US (TR-57) and China (GF002).

The <u>Pulse Metering Application Circuit (Pots with metering)</u>, on page 20 shows a ring trip bridge configured and components are selected for a typical earth-backed ringing applications such as in India (G/LLT and G/MLT).

### **Fault Detector**

The DSLIC device provides a fault detection function in the Active states on each channel. <u>Under a fault condition the detector senses longitudinal voltage at tip and ring and flags a fault by pulling the FLT<sub>i</sub> pin Low. The FLT<sub>i</sub> pins are compatible with logic outputs, and may be monitored to clearly identify a fault condition from a loop condition.</u>

In case of low level longitudinal AC induction the FLT<sub>i</sub> may pulse at twice the frequency of the induction signal.

Upon the loss of battery the FLT pin will be LOW.

## Thermal Shutdown.

Thermal shutdown is provided on a per channel basis to protect the die from excessive temperature. Persistent faults will produce high power dissipation, and may result in the affected channel triggering its thermal shutdown detector (Minimum > 145° C). At this point the power amplifiers are turned off and the device is in a disconnect like state, FLT and DET will be active. The thermal shutdown detector has approximately 10° C of hysteresis. Thermal shutdown on one channel will not affect the operation of the other channel.

The thermal performance of a thermally enhanced package is assured through optimized printed circuit board layout. The thermal pad at the bottom of the package should be soldered down to printed circuit board. Refer to the *Thermal Management for the Le5711 and Le7512 Dual SLIC Devices Application Note* for details.

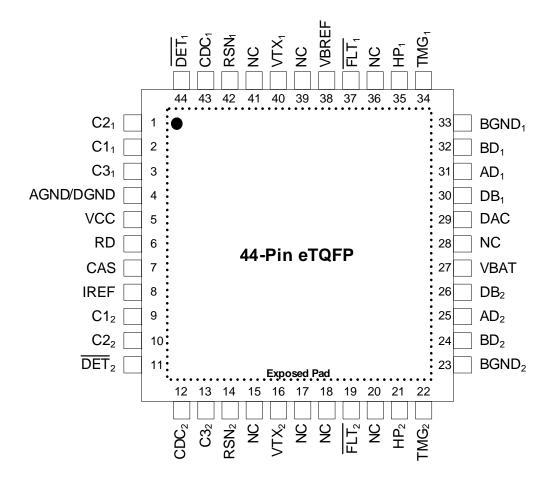

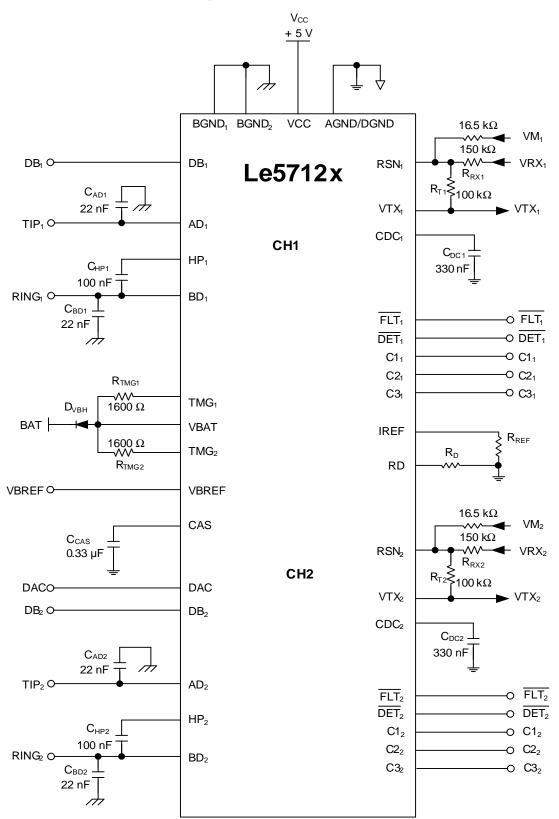

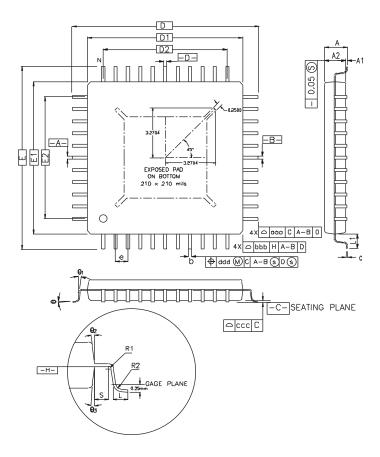

## **CONNECTION DIAGRAM**

#### Note:

- 1. Pin 1 is marked for orientation.

- 2. NC = No Connect

- 3. The exposed heat sink pad on the bottom of the eTQFP package should be connected to VBAT pin the SLIC side of the diode from battery supply. Do not connect it to GND.

# **PIN DESCRIPTIONS**

| Pin Name                                          | Туре      | Description                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD <sub>1</sub>                                   | Output    | Output of AD power amplifier of channel 1.                                                                                                                                                                                                                                                            |

| AD <sub>2</sub>                                   | Output    | Output of AD power amplifier of channel 2.                                                                                                                                                                                                                                                            |

| AGND/DGND                                         | Ground    | Analog and digital ground.                                                                                                                                                                                                                                                                            |

| BD <sub>1</sub>                                   | Output    | Output of BD power amplifier of channel 1.                                                                                                                                                                                                                                                            |

| BD <sub>2</sub>                                   | Output    | Output of BD power amplifier of channel 2.                                                                                                                                                                                                                                                            |

| BGND <sub>1</sub>                                 | Ground    | Battery (power) ground of channel 1                                                                                                                                                                                                                                                                   |

| BGND <sub>2</sub>                                 | Ground    | Battery (power) ground of channel 2.                                                                                                                                                                                                                                                                  |

| C1 <sub>1</sub> /C2 <sub>1</sub> /C3 <sub>1</sub> | Input     | State decoder inputs of channel 1.                                                                                                                                                                                                                                                                    |

| C1 <sub>2</sub> /C2 <sub>2</sub> /C3 <sub>2</sub> | Input     | State decoder inputs of channel 2.                                                                                                                                                                                                                                                                    |

| CAS                                               | Capacitor | Pin for capacitor to filter reference voltage when operating in anti-saturation region.                                                                                                                                                                                                               |

| CDC <sub>1</sub>                                  | Capacitor | DC feed filter capacitor of channel 1.                                                                                                                                                                                                                                                                |

| CDC <sub>2</sub>                                  | Capacitor | DC feed filter capacitor of channel 2.                                                                                                                                                                                                                                                                |

| FLT <sub>1</sub>                                  | Output    | Channel 1 fault detector output <sup>1</sup> .                                                                                                                                                                                                                                                        |

| FLT <sub>2</sub>                                  | Output    | Channel 2 fault detector output <sup>1</sup> .                                                                                                                                                                                                                                                        |

| DAC                                               | Input     | Ring-trip negative of both channels. Negative input to ring-trip comparator.                                                                                                                                                                                                                          |

| DB <sub>1</sub>                                   | Input     | Ring-trip positive of channel 1. Positive input to ring-trip comparator.                                                                                                                                                                                                                              |

| DB <sub>2</sub>                                   | Input     | Ring-trip positive of channel 2. Positive input to ring-trip comparator.                                                                                                                                                                                                                              |

| DET <sub>1</sub>                                  | Output    | Off Hook / Ring-trip detector output of channel1. Logic low indicates that a detector is tripped.                                                                                                                                                                                                     |

| DET <sub>2</sub>                                  | Output    | Off Hook / Ring-trip detector output of channel 2. Logic low indicates that a detector is tripped.                                                                                                                                                                                                    |

| HP <sub>1</sub>                                   | Capacitor | Connect a High-Pass filter capacitor in series with a resistor from HP <sub>1</sub> to BD <sub>1</sub> .                                                                                                                                                                                              |

| HP <sub>2</sub>                                   | Capacitor | Connect a High-Pass filter capacitor in series with a resistor from HP <sub>2</sub> to BD <sub>2</sub> .                                                                                                                                                                                              |

| IREF                                              | Resistor  | Connection for reference resistor that programs Off Hook Detector threshold and DC feed current limit of both channels.                                                                                                                                                                               |

| NC                                                | _         | No Connect. This pin is not internally connected.                                                                                                                                                                                                                                                     |

| RD                                                | Resistor  | Connection for resistor that programs off hook detector threshold of both channels.                                                                                                                                                                                                                   |

| RSN <sub>1</sub>                                  | Input     | Receive Summing Node of channel 1. In the Active and Reverse Polarity states, the current (both AC and DC) between $AD_1$ and $BD_1$ is equal to 500 times the current into this pin. The networks that program receive gain, metering gain and two-wire impedance of Channel 1 connect to this node. |

| RSN <sub>2</sub>                                  | Input     | Receive Summing Node of channel 2. In the Active and Reverse Polarity states, the current (both AC and DC) between $AD_2$ and $BD_2$ is equal to 500 times the current into this pin. The networks that program receive gain, metering gain and two-wire impedance of Channel 2 connect to this node. |

| TMG <sub>1</sub>                                  | Output    | Thermal management of channel 1. External resistor connects from TMG <sub>1</sub> to VBAT to off-load power from the SLIC device.                                                                                                                                                                     |

| TMG <sub>2</sub>                                  | Output    | Thermal management of channel 2. External resistor connects from TMG <sub>2</sub> to VBAT to off-load power from the SLIC device.                                                                                                                                                                     |

| VBAT                                              | Battery   | Battery supply and connection to substrate. Connect to highest negative supply with a diode on a per line base.                                                                                                                                                                                       |

| VBREF                                             | Input     | This is a Microsemi reserved pin and must always be connected to the VBAT pin.                                                                                                                                                                                                                        |

| VCC                                               | Power     | +5 V power supply.                                                                                                                                                                                                                                                                                    |

| VTX <sub>1</sub>                                  | Output    | Transmit audio signal of channel 1. This output is a scaled version of the A and B metallic voltage. VTX <sub>1</sub> also sources the two-wire input impedance programming network.                                                                                                                  |

| VTX <sub>2</sub>                                  | Output    | Transmit audio signal of channel 2. This output is a scaled version of the A and B metallic voltage. VTX <sub>2</sub> also sources the two-wire input impedance programming network.                                                                                                                  |

| EPAD                                              | Battery   | The exposed heat sink pad on the bottom of the eTQFP package should be connected to VBAT pin - the SLIC side of the diode from battery supply. This thermal pad should also be soldered down to printed circuit board to achieve the desired package thermal performance.                             |

## Note:

1. Consult Microsemi representatives for proper handling when not in use.

## **ABSOLUTE MAXIMUM RATINGS**

Stresses greater than those listed under *Absolute Maximum Ratings* can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods can affect device reliability

| Storage temperature                                                                                       | −55 to +150° C                  |

|-----------------------------------------------------------------------------------------------------------|---------------------------------|

| V <sub>CC</sub> with respect to AGND / DGND                                                               | -0.4 to +7.0 V                  |

| V <sub>BAT</sub> with respect to AGND / DGND                                                              | +0.4 to -63 V                   |

| BGND <sub>1</sub> , BGND <sub>2</sub> with respect to AGND / DGND                                         | +3 to -3 V                      |

| AD <sub>1</sub> , AD <sub>2</sub> , BD <sub>1</sub> , BD <sub>2</sub> with respect to BGND:               |                                 |

| Continuous                                                                                                | V <sub>BAT</sub> to + 1 V       |

| 10 ms (F = 0.1 Hz)                                                                                        | –70 to +5 V                     |

| 1 μs (F = 0.1 Hz)                                                                                         | -80 to +8 V                     |

| 250 ns (F = 0.1 Hz)                                                                                       | -90 to +12 V                    |

| Current from AD <sub>1</sub> , AD <sub>2</sub> , BD <sub>1</sub> , BD <sub>2</sub>                        | ±150 mA                         |

| DB <sub>1</sub> , DB <sub>2</sub> , and DAC inputs:                                                       |                                 |

| Voltage on ring-trip inputs                                                                               | V <sub>BAT</sub> to 0 V         |

| Current into ring-trip inputs                                                                             | ±10 mA                          |

| C1 <sub>1</sub> , C2 <sub>1</sub> , C3 <sub>1</sub> , C1 <sub>2</sub> , C2 <sub>2</sub> , C3 <sub>2</sub> |                                 |

| Input Voltage                                                                                             | -0.4 to V <sub>CC</sub> + 0.4 V |

| Maximum power dissipation in 44-pin eTQFP                                                                 |                                 |

| $T_A = 70^{\circ} C$ , continuous                                                                         | (see note 1)                    |

| Thermal Data in 44-pin eTQFP package                                                                      |                                 |

| Junction to Ambient, $	heta_{JA}$                                                                         | (see note 2)                    |

| ESD Immunity (Human Body Model)                                                                           | JESD22 Class 1C compliant       |

#### Notes:

- Thermal limiting circuitry on chip will shut down the circuit at a junction temperature of about 165° C. Continuous operation above 145° C junction temperature may degrade device reliability. Refer to the Thermal Management for the Le5711 and Le7512 Dual SLIC Devices Application Note for details.

- The thermal performance of a thermally enhanced package is assured through optimized printed circuit board layout. Refer to the Thermal Management for the Le5711 and Le5712 Dual SLIC Devices Application Note for details.

## Package Assembly

Green package devices are assembled with enhanced, environmental compatible lead-free, halogen-free, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes. The peak soldering temperature should not exceed 245°C during printed circuit board assembly.

Refer to IPC/JEDEC J-Std-020B Table 5-2 for the recommended solder reflow temperature profile.

## **OPERATING RANGES**

The operating ranges specified below define those limits between which the device operates and is guaranteed under the noted test conditions. (Refer to <u>Summary of Test Conditions</u>, on page 9.)

## **Environmental Ranges**

Microsemi guarantees the performance of this device over commercial (0 to 70° C) and industrial (–40 to 85° C) temperature ranges by conducting electrical characterization, production testing, and periodic sampling over each range. These characterization and test procedures comply with section 4.6.2 of Bellcore GR-357-CORE Component Reliability Assurance Requirements for Telecommunications Equipment.

| ĺ | Ambient Temperature       | –40° to 85°C |

|---|---------------------------|--------------|

|   | Ambient Relative Humidity | 15% to 85%   |

## **Electrical ranges**

| V <sub>CC</sub>                                                  | 4.75 to 5.25 V           |

|------------------------------------------------------------------|--------------------------|

| VBAT                                                             | −39 to −60 V             |

| DB1, DB2, and DAC                                                | V <sub>BAT</sub> to –2 V |

| AGND                                                             | 0 V                      |

| BGND <sub>1</sub> , BGND <sub>2</sub> with respect to AGND/DGND  | -100 to + 100 mV         |

| Load resistance on VTX <sub>1</sub> , VTX <sub>2</sub> to ground | 8 kΩ minimum             |

## **ELECTRICAL CHARACTERISTICS**

# **Summary of Test Conditions**

Unless otherwise noted, the test conditions are defined by the Le5712 device test circuit shown in Figure 7, on page 17 with: VCC=5 V, BAT = -52 V,  $R_L = R_{LAC} = 600~\Omega$ ,  $R_{REF} = 14.3~k\Omega$ ,  $R_D = 82.5~k\Omega$ .

# **Supply Currents and Power Dissipation (on-hook)**

|                                        | Icc  | mA (Note | : <u>1.</u> ) | I <sub>VBA</sub> | <sub>T</sub> mA (Not | te <u>1.</u> ) | SLIC D | evice Pow | er mW |      |

|----------------------------------------|------|----------|---------------|------------------|----------------------|----------------|--------|-----------|-------|------|

| Operational State                      | Min. | Тур      | Max           | Min.             | Тур                  | Max            | Min.   | Тур       | Max   | Note |

| Disconnect                             |      | 3.2      | 5.5           |                  | 0.5                  | 0.8            |        | 42        | 62    |      |

| Standby                                |      | 3.2      | 6.5           |                  | 0.6                  | 1.0            |        | 46        | 70    |      |

| Tip Open                               |      | 3.1      | 6.5           |                  | 0.6                  | 1.0            |        | 46        | 70    |      |

| Active                                 |      | 9.0      | 13            |                  | 6.0                  | 10.0           |        | 353       | 540   |      |

| Reverse Polarity                       |      | 9.0      | 13            |                  | 6.0                  | 10.0           |        | 353       | 540   |      |

| Active Metering                        |      | 9.3      | 13            |                  | 6.0                  | 10.0           |        | 355       | 540   |      |

| Reverse Polarity<br>Metering           |      | 9.3      | 13            |                  | 6.0                  | 10.0           |        | 355       | 540   | 2    |

| One channel Standby One channel Active |      | 6.1      | 10            |                  | 3.3                  | 5.5            |        | 200       | 305   |      |

## **SPECIFICATIONS**

## **Device specifications**

| Specification                                    | Condition                                                                       | Min.              | Тур  | Max               | Unit                 | Note |

|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------|------|-------------------|----------------------|------|

| Line Characteristics                             |                                                                                 |                   |      |                   |                      |      |

|                                                  | Active Forward                                                                  | 42.75             | 45.7 | 48                |                      |      |

|                                                  | Active Reverse                                                                  | 42.5              | 40.7 | 40                |                      |      |

| VAB, Open Circuit                                | Standby                                                                         | 46.75             |      | 52                | V                    |      |

|                                                  | Metering Forward                                                                | 38                | 41.5 | 42.5              |                      |      |

|                                                  | Metering Reverse                                                                | 37.5              | 71.5 | 72.0              |                      |      |

| I <sub>L</sub> , Long Loops, Active state        | R <sub>LDC</sub> = 2000 Ω, BAT = -48 V                                          | 19.8              | 20.5 |                   | mA                   |      |

| I <sub>LIMIT</sub> , Short Loops, Active state   | $R_{LDC}$ = 100 Ω to 1100 Ω                                                     | 30                | 33   | 36                | mA                   | 3    |

| I <sub>L</sub> , Long Loops, Active state        | R <sub>LDC</sub> = 2125 Ω                                                       | 20                | 21.1 |                   | mA                   |      |

| I <sub>L</sub> , Long Loops, Active state        | R <sub>LDC</sub> = 2125 Ω, BAT = -46.5 V                                        | 18                | 18.5 |                   | mA                   |      |

| I <sub>L</sub> , Accuracy, Standby state         | $I_{L} = \left(\frac{ BAT  - 4V}{(R_{L} + 600)}\right), R_{LDC} \ge 2000\Omega$ | 0.9I <sub>L</sub> | IL   | 1.11 <sub>L</sub> | 1.1I <sub>L</sub> mA |      |

|                                                  | Current Limited Region                                                          | 20                | 30   | 45                | 1                    |      |

| I <sub>L</sub> LIM, AD and BD to BGND            | Active, I <sub>AD</sub> + I <sub>BD</sub>                                       |                   | 85   | 120               | mA                   |      |

| I <sub>L</sub> , Loop current, Disconnect state  | $R_L = 0 \Omega$                                                                |                   |      | 100               | μA                   |      |

| I <sub>AD</sub> leakage, Tip Open state          | $R_L = 0 \Omega$                                                                |                   |      | 100               | μΑ                   |      |

| I <sub>BD</sub> current, Tip Open state          | BD to BGND                                                                      | 20                | 30   | 45                | mA                   |      |

| V <sub>AD</sub> Active and Standby states        | AD to BAT=7 k $\Omega$ , BD to GND=100 $\Omega$                                 | -7.5              | -5   |                   | V                    |      |

| V <sub>IREF</sub> , IREF pin output voltage      |                                                                                 | 1.2               | 1.25 | 1.3               | V                    |      |

| K1, Incremental RSN current gain                 |                                                                                 | 490               | 500  | 510               | A/A                  |      |

| Power Supply Rejection Ratio at the              | ne Two-Wire Interface (Active states, Or                                        | n or Off Ho       | ook) | u .               |                      | 1    |

| V <sub>CC</sub>                                  | 50 Hz to 3.4 kHz<br>V <sub>RIPPLE</sub> = 100 mVrms                             | 30                | 40   |                   |                      |      |

|                                                  | V <sub>RIPPLE</sub> = 100 mVrms                                                 | 29                | 50   |                   | dB                   | 4    |

| $V_{BAT}$                                        | 300 Hz to 3.4 kHz                                                               | 28                | 30   |                   |                      |      |

|                                                  | 50 Hz to 60 Hz                                                                  | 20                |      |                   | 1                    |      |

| RI <sub>AS</sub> , Effective internal resistance | CAS pin to AGND                                                                 | 90                | 150  | 210               | kΩ                   | 2    |

| Specification                                                      | Condition                                                                                                                                                          | Min.                 | Тур  | Max | Unit  | Note  |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|-----|-------|-------|

| Longitudinal Capability (See Figure 4                              | . on page 16.)                                                                                                                                                     |                      |      |     |       |       |

| Longitudinal to metallic L-T balance                               | Normal polarity                                                                                                                                                    | -60                  | -64  |     | dB    |       |

| 200 Hz to 1.0 kHz, Le57122                                         | 0° C to +70° C                                                                                                                                                     | 00                   | 04   |     | ub.   |       |

| Longitudinal to metallic L-T balance                               | Normal polarity                                                                                                                                                    | <b>–</b> 57          | -61  |     | dB    |       |

| 3.0 kHz, Le57122                                                   | 0° C to +70° C                                                                                                                                                     |                      |      |     |       |       |

| Longitudinal to metallic L-T balance                               | Normal polarity                                                                                                                                                    | <b>-</b> 57          | -64  |     | dB    | 2     |

| 200 Hz to 1.0 kHz, Le57122                                         | -40° C to +85° C                                                                                                                                                   |                      |      |     |       |       |

| Longitudinal to metallic L-T balance                               | Normal polarity -40° C to +85° C                                                                                                                                   | -54                  | -61  |     | dB    | 2     |

| 3.0 kHz, Le57122  Longitudinal to metallic L-T balance             | -40° C 10 +65° C                                                                                                                                                   |                      |      |     |       |       |

| 200 Hz to 3.0 kHz, Le57121                                         | 0° C to +70° C                                                                                                                                                     | <del>-</del> 53      |      |     | dB    |       |

| Longitudinal to metallic L-T balance<br>200 Hz to 3.0 kHz, Le57121 | -40° C to +85° C                                                                                                                                                   | <b>-</b> 50          |      |     |       | 2     |

| Longitudinal signal generation 4-L                                 | 200 Hz to 3.4 kHz                                                                                                                                                  | 40                   |      |     | dB    |       |

| Longitudinal current per pin (AD <sub>i</sub> or BD <sub>i</sub> ) | Active state (off hook)                                                                                                                                            | 8.5                  |      |     | mArms | 5     |

| Longitudinal impedance at AD <sub>i</sub> or BD <sub>i</sub>       | 0 to 100 Hz                                                                                                                                                        |                      | 18.5 |     | Ω/pin |       |

| RFI Rejection (See Figure 6, on page                               | 1<br>e 16.)                                                                                                                                                        |                      |      |     | 1     |       |

| VTX <sub>1</sub> or VTX <sub>2</sub>                               | $ f = .01 \text{ to } 100 \text{ MHz} $ $ HF \text{ gen. output} = 1.5 \text{ Vrms} $ $ C_{AXi} = C_{BXi} = 33 \text{ nF} $ $ C_{AXi} = C_{BXi} = 2.2 \text{ nF} $ |                      |      | 1 3 | mVrms | 2     |

| Transmission Performance                                           | OAXI — OBXI — 2.2 III                                                                                                                                              |                      |      | 3   |       |       |

| Transmission renormance                                            | 200 Hz to 3.4 kHz (See Figure 5, on                                                                                                                                |                      | 1    |     | 1     |       |

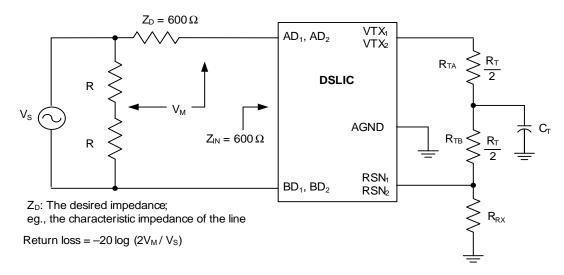

| 2-wire return loss                                                 | page 16)                                                                                                                                                           | 26                   |      |     | dB    | 2, 6  |

| Analog output (VTX) impedance                                      |                                                                                                                                                                    |                      | 3    | 25  | Ω     | 2     |

| Analog (VTX) output offset voltage                                 |                                                                                                                                                                    | -50                  |      | +50 | mV    |       |

| Overload level, 2-wire                                             | Active or Reverse Polarity state                                                                                                                                   | 2.5                  |      |     |       | 7     |

| Overload level, 2-wire                                             | On hook, Active or Reverse Polarity state                                                                                                                          | 1.1                  |      |     | Vpk   | 8     |

| Overload level, 2-wire                                             | Metering states                                                                                                                                                    | 5.5                  |      |     | 1 '   | 7     |

| Overload level, 2-wire                                             | On hook, Metering states                                                                                                                                           | 5.5                  |      |     |       | 8     |

|                                                                    | 0 dBm                                                                                                                                                              |                      | -64  | -50 |       |       |

| THD (Total Harmonic Distortion)                                    | +7 dBm                                                                                                                                                             |                      | -55  | -40 | -ID   | 4     |

|                                                                    | +9 dBm, Metering states                                                                                                                                            |                      | -55  | -40 | dB    | 4     |

| THD, On hook                                                       | 0 dBm, $R_{LAC} = 600 \Omega$                                                                                                                                      |                      |      | -36 |       |       |

| THD with metering                                                  | $R_L = 300 \Omega$                                                                                                                                                 |                      |      | -35 |       | 2, 9  |

| Jalla Ohannal Naiss                                                | C-Message, $R_L = 600 \Omega$                                                                                                                                      |                      | 7    | 12  | dBrnC | 2     |

| Idle Channel Noise                                                 | Psophometric, $R_L = 600 \Omega$                                                                                                                                   |                      | -83  | -78 |       |       |

|                                                                    | Psophometric, $R_L = 300 \Omega$ ,                                                                                                                                 | $R_1 = 300 \Omega$ , |      |     | dBmp  |       |

| Idle Channel Noise with Metering                                   | Metering states                                                                                                                                                    |                      |      | -46 |       | 2, 10 |

| Crosstalk Between Channels                                         |                                                                                                                                                                    |                      |      |     |       |       |

| Crosstalk coupling loss                                            | Averaged over 200 Hz to 3.4 kHz, 0dBm                                                                                                                              |                      | 80   |     | dB    | 11    |

Le5712 Data Sheet

| Specification                                                                                       | Condition                                                                                        | Min.                 | Тур   | Max            | Unit     | Note |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------|-------|----------------|----------|------|

| Insertion Loss (See Figure 2 and Fig                                                                | ure 3, on page 15.)                                                                              |                      |       |                |          |      |

| Gain, 4-to-2-wire                                                                                   | 0 dBm, 1 kHz                                                                                     | -0.25                | 0     | +0.20          |          |      |

| Gain K <sub>TX</sub> , 2-to-4-wire                                                                  | 0 dBm, 1 kHz                                                                                     | -9.74                | -9.54 | -9.32          |          |      |

| Gain, 4-to-4-wire                                                                                   | 0 dBm, 1 kHz                                                                                     | -9.74                | -9.54 | -9.34          |          |      |

| Gain, 4-to-2-wire                                                                                   | On hook                                                                                          | -0.35                |       | +0.35          | dB       |      |

| Gain over frequency                                                                                 | 300 to 3400 Hz, relative to 1 kHz                                                                | -0.15                |       | +0.15          |          |      |

| Gain tracking                                                                                       | +3 to -55 dBm, relative to 0 dBm                                                                 | -0.15                |       | +0.15          |          |      |

| Gain tracking, On hook                                                                              | 0 dBm to -37 dBm<br>+3 dBm to 0 dBm                                                              | -0.15<br>-0.35       |       | +0.15<br>+0.35 |          | 2    |

| Metering Gain, 4-to-2-wire                                                                          | $V_{M} = 0.5 \text{ vrms}, 16 \text{ kHz}, R_{L} = 300 \Omega$                                   | 15.1                 | 15.6  | 16.1           | dB       | 12   |

| Logic Interface                                                                                     | l                                                                                                | 1                    |       | l              | I        | 1    |

| Inputs (C1 <sub>1</sub> , C1 <sub>2</sub> , C2 <sub>1</sub> , C2 <sub>2</sub> , C3 <sub>1</sub> and | C3 <sub>2</sub> )                                                                                |                      |       |                |          |      |

| V <sub>IH</sub> , Input High voltage                                                                |                                                                                                  | 2.0                  |       |                | .,       |      |

| V <sub>IL</sub> , Input Low voltage                                                                 |                                                                                                  |                      |       | 0.8            | V        |      |

| I <sub>IH</sub> , Input High current                                                                | V <sub>IH</sub> =2.0V                                                                            | -110                 |       | 90             |          |      |

| I <sub>IL</sub> , Input Low current                                                                 | V <sub>IL</sub> =0.8V                                                                            | -400                 |       |                | μΑ       |      |

| Outputs (DET <sub>1</sub> and DET <sub>2</sub> )                                                    |                                                                                                  | <u> </u>             |       |                | <u> </u> |      |

| V <sub>OL</sub> , Output Low voltage                                                                | I <sub>OUT</sub> = 0.3 mA                                                                        |                      |       | 0.40           | V        |      |

| V <sub>OH</sub> , Output High voltage                                                               | I <sub>OUT</sub> = -0.1 mA                                                                       | 2.4                  |       |                | V        |      |

| Outputs (FLT <sub>1</sub> and FLT <sub>2</sub> )                                                    |                                                                                                  | · L                  |       |                | I        |      |

| V <sub>OL</sub> , Output Low voltage                                                                | I <sub>OUT</sub> = 0.06 mA                                                                       |                      |       | 0.40           |          |      |

| V <sub>OH</sub> , Output High voltage                                                               | I <sub>OUT</sub> = -0.01 mA                                                                      | 2.4                  |       |                | V        |      |

| Ring-Trip Detector Input (Applies to                                                                | DAC, DB <sub>1</sub> and DB <sub>2</sub> .)                                                      | <u> </u>             |       |                | <u>I</u> |      |

| Bias Current                                                                                        |                                                                                                  | -50                  | -10   | 0              | nA       | 2    |

| Offset voltage                                                                                      | Source resistance = 2 M $\Omega$                                                                 | -50                  | 0     | +50            | mV       | 13   |

| Common Mode Voltage Range                                                                           |                                                                                                  | V <sub>BAT</sub> + 1 |       | -2             | V        | 2    |

| Fault Detector (See Figure 1, on page                                                               | <u>e 15</u> .)                                                                                   |                      |       |                |          | •    |

| $I_{FAULT} =  I_{AD} + I_{BD} $                                                                     |                                                                                                  | 8                    | 11.5  | 22             | mA       |      |

| Off-Hook and Ground Start Detecto                                                                   | rs (See Figure 1, on page 15.)                                                                   | ч                    | I.    | II.            |          |      |

| I <sub>OHD</sub> On-to-Off hook Detection<br>Threshold                                              | Active and Standby states                                                                        | 9.8                  | 11.5  | 13.2           |          |      |

| Hysteresis                                                                                          | The difference between On-to-Off hook detection threshold and Off-to-On hook Detection threshold | 1.3                  | 2.0   | 2.7            | . mA     |      |

| I <sub>GSD</sub> , Ground Start Detect threshold (On-to-Off hook detection threshold)               | Tip Open state                                                                                   | 11.8                 | 13.5  | 16.0           | ША       |      |

| Hysteresis (Ground Start)                                                                           | The difference between On-to-Off hook detection threshold and Off-to-On hook detection threshold | 2.6                  | 4.0   | 5.4            |          |      |

#### Notes:

- 1. Total current measured with both channels in the same state, unless otherwise specified.

- 2. Not tested in production. This parameter is guaranteed by characterization or correlation to other tests.

- 3. Typical current limit range is designed to be between 22 mA and 33 mA.

- 4. This parameter is tested at 1 kHz in production. Performance at other frequencies is guaranteed by characterization.

- 5. Minimum current level guaranteed not to cause a false loop detect. The fault detector may activate with longitudinal currents above 2.8 mA rms, and may pulse at twice the frequency of the interfering signal.

- 6. Group delay can be greatly reduced by using a  $Z_T$  network such as that shown in Figure 5. on page 16 where  $C_T = 120$  pF,  $R_{TA} = R_{TB} = 50$  k $\Omega$ . The network reduces the group delay to less than 2  $\mu$ s and increases 2WRL. The effect of group delay on line card performance also may be compensated by synthesizing complex impedance with the QLSLAC<sup>TM</sup> or Octal SLAC<sup>TM</sup> devices.

- 7. Overload level is defined as THD = 1%,

- 8. Overload level is defined as THD = 1.5%.

- 9. Total Harmonic distortion with metering is specified with a metering signal of 3.0 Vrms at the two-wire output, and a transmit signal of +3 dBm or receive signal of -4 dBm. The transmit or receive signals are single frequency inputs, and the distortion is measured as the highest in band harmonic at the two-wire or the four-wire output relative to the input signal.

- 10. Noise with metering is measured by applying a 3.0 Vrms metering signal (measured at the two-wire output) and measuring the psophometric noise at the two-wire outputs over a 200 ms time interval

- 11. This is test at 1 kHz in production

- 12. In the test set up,  $Z_T = 100 \text{ k}\Omega$ ,  $R_M = 16.5 \text{ k}\Omega$ , and  $R_F = 0 \Omega$ . The output voltage at tip/ring is expected to be 3 Vrms, into a load of 300  $\Omega$ , with 0.5 Vrms source. The typical gain is 15.6 dB.

- 13. Tested with  $0 \Omega$  source impedance. 2  $M\Omega$  is specified for system design only.

# **User-Programmable Components Summary**

| Equation                                                                                                                                                                      | Description                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $Z_{Ti} = \frac{500}{3}(Z_{2WIN} - 2R_F)$                                                                                                                                     | $Z_{\text{TI}}^{\star}$ is connected between the VTX and RSN pins. The fuse resistors are R <sub>F</sub> , and $Z_{\text{2WIN}}$ is the desired 2-wire AC input impedance. When computing $Z_{\text{TI}}$ , the internal current amplifier pole and any external stray capacitance between VTX and RSN must be taken into account. |

| $Z_{RXi} = \frac{Z_L}{G_{42L}} \bullet \frac{500 \bullet Z_T}{Z_T + \frac{500}{3} \cdot (Z_L + 2R_F)}$                                                                        | $Z_{RXi}^{*}$ is connected from VRX to RSN. $Z_{Ti}$ is defined above, and $G_{42L}$ is the desired receive gain.                                                                                                                                                                                                                  |

| $R_{REF} = \frac{470 \cdot V}{I_{LIMIT}}$                                                                                                                                     | I <sub>LIMIT</sub> is the desired loop current limit in the constant-current region.                                                                                                                                                                                                                                               |

| $C_{CAS} = \frac{1}{RI_{AS} \cdot 2\pi \cdot f_{c}}$                                                                                                                          | $C_{CAS}$ is the regulator filter capacitor and $f_c$ is the desired filter cut-off frequency.                                                                                                                                                                                                                                     |

| $I_{OHD} = I_{GSD} = \frac{935 \cdot V}{R_D}$                                                                                                                                 | Off Hook Detect (I <sub>OHD</sub> ) and Ground Start<br>Detect (I <sub>GSD</sub> ) thresholds are typically set at<br>10 to 12 mA.                                                                                                                                                                                                 |

| $I_{STANDBY} = \frac{ V_{BAT}  - 4 V}{600 \Omega + R_{L}}$                                                                                                                    | Standby loop current (resistive region).                                                                                                                                                                                                                                                                                           |

| Thermal Management Equations (All Active states for one channel) (Please refer to the The SLIC Devices Application Note for details about dual battery operation.)            | ermal Management for the Le5711 and Le7512 Dual                                                                                                                                                                                                                                                                                    |

| $R_{TMG} \ge \frac{\left  BAT_{MAX} \right  - 6 - I_{LIMITMIN} \cdot (2 \cdot R_F + R_{LMIN} + 40\Omega)}{I_{LIMITMIN} - 3 \text{ mA}}$                                       | R <sub>TMG</sub> is connected from TMG to VBAT and limits power within the SLIC device in Active, Off-Hook states.                                                                                                                                                                                                                 |

| $P_{RTMGmax} = \frac{\left(\left BAT\right _{max} - 5 - I_{LIMITmin} \left(R_{Lmin} + 2R_{F} + 40\right)\right)^2}{R_{TMGmin}}$                                               | Maximum power dissipated in the TMG resistor, R <sub>TMG</sub> , during Active, Off-Hook states.                                                                                                                                                                                                                                   |

| $P_{SLICmaxi} = \left. 0.003 \middle  BAT \middle _{max} + \left( 1 + \frac{I_{LIMITmax}}{2} R_{TMGmax} \right) \left( \frac{I_{LIMITmax}}{2} + \frac{1}{R_{TMGmax}} \right)$ | Maximum power dissipated per channel in the SLIC device while in Active, Off-Hook states.                                                                                                                                                                                                                                          |

<sup>\* &</sup>quot;i" denotes channel number

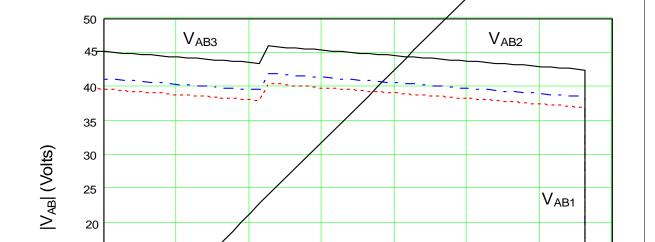

## **DC Feed Characteristics**

15

Load Line (Active) (Typical)

BAT = -46.5 V

BAT = -48 V

BAT = -52 V

RL = 2125 ohm

On-Hook

10

## Regions:

1. Constant current region:

15

10

5

$$V_{AB1} = I_{LOOP}R_L = \frac{470}{R_{REF}}R_L$$

, where,  $R_L = R_L' + 2R_F$

-Off-Hook-

Loop Current (mA)

In Active and Reverse Polarity states

- 2. Battery tracking anti-sat (Off-hook):

- $V_{AB2} = |BAT| 7 V + \frac{47 \cdot k\Omega \cdot V}{R_{REF}} I_{L} \cdot 160 \Omega$   $V_{AB2} = |BAT| 7 V + \frac{10 \cdot k\Omega \cdot V}{R_{REF}} I_{L} \cdot 160 \Omega$

- 3. Battery tracking anti-sat (On-hook):

$$V_{AB3} = |BAT| - 7 V + \frac{10 \cdot k\Omega \cdot V}{R_{REF}} - I_{L} \cdot 160 \Omega$$

In Active Metering and Reverse Polarity Metering states

4. Battery tracking anti-sat (Off-hook):

$$V_{\text{AB2}} = \left| \text{BAT} \right| - 10.7 \text{ V} + \frac{47 \cdot k\Omega \cdot V}{R_{\text{REF}}} - I_{\text{L}} \cdot 160 \Omega$$

5. Battery tracking anti-sat (On-hook):

$$V_{\text{AB3}} = |BAT| - 10.7 \text{ V} + \frac{10 \cdot k\Omega \cdot V}{R_{\text{REF}}} - I_{L} \cdot 160 \Omega$$

# **Test Circuits**

Figure 1. Feed Programming

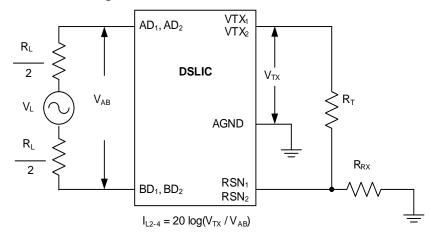

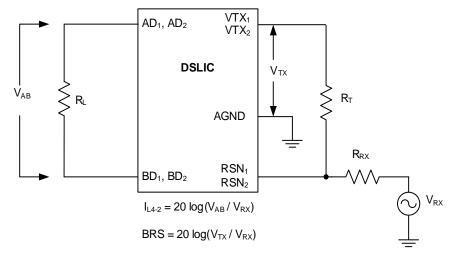

Figure 2. Two-to-Four Wire Insertion Loss

Figure 3. Four-to-Two Wire Insertion Loss and Balance Return Signals

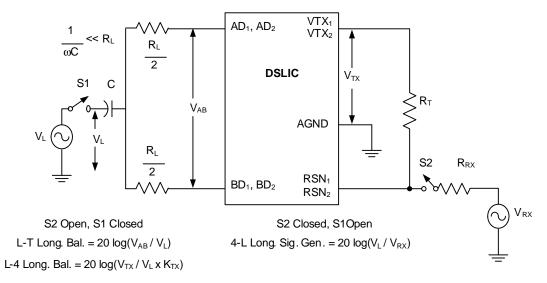

Figure 4. Longitudinal Balance

Figure 5. Two-Wire Return Loss Test Circuit

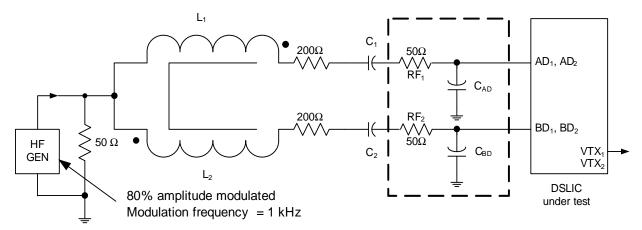

Figure 6. RFI Test Circuit

Figure 7. Le5712 Test Circuit

# POTS APPLICATION CIRCUIT (POTS WITH NO METERING)

For use with a Quad or Octal SLAC device; battery-backed ringing.

# **APPLICATION CIRCUIT PARTS LIST (POTS WITH NO METERING)**

The following list defines the parts and part values required to meet target specification limits for channel i of the line card (i = 1,2).