Power Matters."

# FEATURES

- VDSL2 30a profile, 14.5 dBm Line Driver

- Very low power dissipation

Class AB operation

- Up to 8 programmable states

- No external gain resistors required

- Small footprint package

- 16-pin (4 mm x 4 mm) QFN

- RoHS compliant

# **APPLICATIONS**

- VDSL2 Line Driver

- ADSL2+ CPE Line Driver

### DESCRIPTION

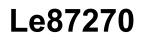

The Le87270 is a single channel differential amplifier designed to drive full rate VDSL2, as well as ADSL2+ signals with very low power dissipation. The Le87270 contains a pair of wideband amplifiers designed with Microsemi's HV15 Bipolar SOI process for low power consumption.

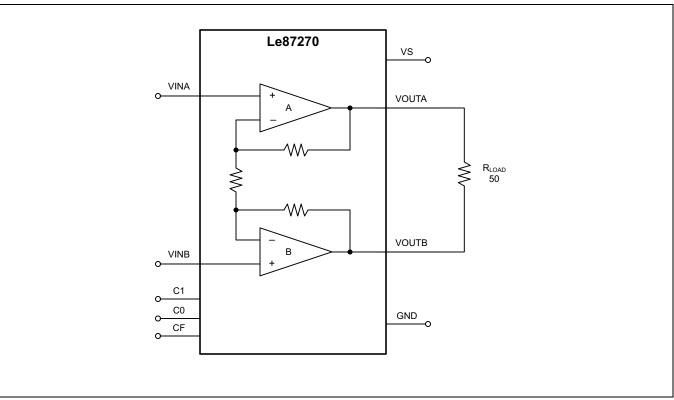

#### **BLOCK DIAGRAM**

Preliminary Data Sheet

| Document ID# 1464                                                                                                                               | 30 Version 6                                         | January 2016          |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------|--|--|--|--|

| ORDERING INFORMATION                                                                                                                            |                                                      |                       |  |  |  |  |

| Le87270NQC<br>Le87270NQCT                                                                                                                       | 16-pin QFN Green Package<br>16-pin QFN Green Package | Tray<br>Tape and Reel |  |  |  |  |

| The green package meets RoHS 2 Directive 2011/65/EU of the<br>European Council to minimize the environmental impact of electrical<br>equipment. |                                                      |                       |  |  |  |  |

| The line driver gain is fixed internally. The amplifiers are powered from a single supply.                                                      |                                                      |                       |  |  |  |  |

| Control pins can be used to adjust the supply current to one-of-three or one-of-seven preset Bias level states and                              |                                                      |                       |  |  |  |  |

a Standby state. The control pins respond to input levels that can be generated with a standard tri-state GPIO. The Le87270 is available in a 16-pin (4 mm x 4 mm) QFN

package with exposed pad for enhanced thermal conductivity.

# TABLE OF CONTENTS

| Features                    | l |

|-----------------------------|---|

| Applications 1              |   |

| Description                 | l |

| Ordering Information        | l |

| Block Diagram 1             |   |

| Connection Diagram          | 3 |

| Pin Descriptions            | 3 |

| Absolute Maximum Ratings 4  | ŀ |

| Thermal Resistance          | ŀ |

| Package Assembly.           | ŀ |

| Operating Ranges            | ŀ |

| Device Specifications       | ; |

| State Control               | ' |

| Applications                | 3 |

| Typical Application Circuit | 3 |

| Line Driver Protection.     | 3 |

| Physical Dimensions         | ) |

| 16-pin QFN                  | ) |

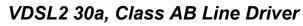

# **CONNECTION DIAGRAM**

#### Notes:

Pin 1 is marked for orientation. 1.

The Le87270 device incorporates an exposed die pad on the underside of its package. The pad acts as a heat sink and must be connected to a copper plane through thermal vias, for proper heat dissipation. It is electrically isolated and maybe connected to GND. 2.

#### **PIN DESCRIPTIONS**

| Pin # | Pin Name    | Туре   | Description                                                   |  |

|-------|-------------|--------|---------------------------------------------------------------|--|

| 1     | NC          |        | No internal connection                                        |  |

| 2     | NC          |        |                                                               |  |

| 3     | VINA        | Input  | Non-inverting input of amplifier A                            |  |

| 4     | GND         | Ground | Reference ground                                              |  |

| 5     | NC          |        | No internal connection                                        |  |

| 6     | CF          | Input  | Digital mode control - Fine Bias steps                        |  |

| 7     | GND         | Ground | Reference ground                                              |  |

| 8     | C0          | Input  | Digital mode control 0                                        |  |

| 9     | C1          | Input  | Digital mode control 1                                        |  |

| 10    | VINB        | Input  | Non-inverting input of amplifier B                            |  |

| 11    | NC          |        | No internal connection                                        |  |

| 12    | NC          |        |                                                               |  |

| 13    | VOUTB       | Output | Amplifier B output                                            |  |

| 14    | VS          | Power  | Power supply, +12 V                                           |  |

| 15    | NC          |        | No internal connection                                        |  |

| 16    | VOUTA       | Output | Amplifier A output                                            |  |

|       | Exposed pad |        | Electrically isolated thermal conduction pad, can be grounded |  |

### ABSOLUTE MAXIMUM RATINGS

Stresses above the values listed under Absolute Maximum Ratings can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods can affect device reliability.

| Storage Temperature                        | $-65 \le T_A \le +150^{\circ}C$ |

|--------------------------------------------|---------------------------------|

| Operating Junction Temperature<br>(Note 1) | $T_A \le +150^{\circ}C$         |

| VS with respect to GND                     | –0.3 V to +16 V                 |

| Driver inputs (VINA, VINB)                 | GND to VS                       |

| Control inputs with respect to GND         | -0.3 V to 4 V                   |

| Continuous Driver Output Current           | 75 mA                           |

| ESD Immunity (Human Body Model)            | JESD22 Class 2 compliant        |

| ESD Immunity (Charge Device Model)         | JESD22 Class IV compliant       |

Note:

1. Continuous operation above 145°C junction temperature may degrade device reliability.

#### Thermal Resistance

The thermal performance of a thermally enhanced package is assured through optimized printed circuit board layout. Specified performance requires that the exposed thermal pad be soldered to an equally sized exposed copper surface, which, in turn, conducts heat through multiple vias to larger internal copper planes.

#### Package Assembly

The green package devices are assembled with enhanced, environmental compatible lead-free, halogen-free, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes.

Refer to IPC/JEDEC J-Std-020 Table 4 for recommended peak soldering temperature and Table 5-2 for the recommended solder reflow temperature profile.

#### **OPERATING RANGES**

Microsemi guarantees the performance of this device over the industrial (-40°C to 85°C) temperature range by conducting electrical characterization over each range and by conducting a production test with single insertion coupled with periodic sampling. These characterization and test procedures comply with the Telcordia GR-357-CORE Generic Requirements for Assuring the Reliability of Components Used in Telecommunications Equipment.

| Ambient temperature | T <sub>A</sub>         | -40°C to +85°C |

|---------------------|------------------------|----------------|

| Power Supply        | VS with respect to GND | +12 V ± 5%     |

# **DEVICE SPECIFICATIONS**

*Typical Conditions:* As shown in the basic test circuit (<u>Figure 1</u>) with VS = +12 V and  $T_A = 25^{\circ}C$ .

*Min/Max Parameters:* T<sub>A</sub> = -40 to +85°C

#### Table 1. Electrical Specifications

| Symbol                                       | Parameter<br>Description                                                                                                              | Condition                                                                                                                                                                                                                                              | Min      | Тур                                    | Max  | Unit                | Notes |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------|------|---------------------|-------|--|

| Supply C                                     | urrent Characteristics                                                                                                                |                                                                                                                                                                                                                                                        |          |                                        |      |                     |       |  |

| I <sub>VS</sub> Tota                         | Total Supply Current                                                                                                                  | High Bias                                                                                                                                                                                                                                              | 30       | 40                                     | 50   | mA                  |       |  |

|                                              |                                                                                                                                       | Medium Bias                                                                                                                                                                                                                                            | 23       | 33                                     | 38   | mA                  | 1     |  |

|                                              |                                                                                                                                       | Low Bias                                                                                                                                                                                                                                               | 11       | 15                                     | 19   | mA                  |       |  |

|                                              |                                                                                                                                       | Standby                                                                                                                                                                                                                                                | 400      | 500                                    | 650  | μA                  | 1     |  |

| Control I                                    | nput (C0, C1, CF) Level                                                                                                               | Specifications                                                                                                                                                                                                                                         |          |                                        |      |                     |       |  |

| V <sub>IH</sub>                              | Input High Voltage                                                                                                                    |                                                                                                                                                                                                                                                        | 2.0      |                                        |      | V                   |       |  |

| V <sub>IL</sub>                              | Input Low Voltage                                                                                                                     |                                                                                                                                                                                                                                                        |          |                                        | 0.8  | V                   |       |  |

| I                                            | Input High Current                                                                                                                    | C0/1 = 3.3 V                                                                                                                                                                                                                                           | 10       | 66                                     | 100  | μA                  | 2     |  |

| IIH                                          |                                                                                                                                       | CF = 3.3 V                                                                                                                                                                                                                                             | 0        | 0.02                                   | 10.0 | μA                  |       |  |

| IIL                                          | Input Low Current                                                                                                                     | C0/1 = 0 V                                                                                                                                                                                                                                             | 0        | 0.1                                    | 10.0 | μA                  | 3     |  |

| ١L                                           |                                                                                                                                       | CF = 0 V                                                                                                                                                                                                                                               | 10       | 50                                     | 100  | μA                  | 3     |  |

| Amplifier                                    | <b>Output Characteristics</b>                                                                                                         | ;<br>;                                                                                                                                                                                                                                                 |          |                                        | •    | •                   |       |  |

|                                              | Differential Gain                                                                                                                     | VOUT/VIN                                                                                                                                                                                                                                               | 5.35     | 5.50                                   | 5.60 | V/V                 |       |  |

| V <sub>O</sub>                               | Output Voltage                                                                                                                        |                                                                                                                                                                                                                                                        | 9.5      | 10                                     |      | V                   |       |  |

| I <sub>O</sub>                               | Output Current                                                                                                                        |                                                                                                                                                                                                                                                        | 300      |                                        |      | mA                  | 4     |  |

| Amplifier                                    | Dynamic Characteristi                                                                                                                 | cs                                                                                                                                                                                                                                                     |          |                                        |      |                     |       |  |

| BW                                           | -3 dB Bandwidth                                                                                                                       | Default bias state                                                                                                                                                                                                                                     |          | 80                                     |      | MHz                 |       |  |

| SR                                           | Slew rate                                                                                                                             | Default bias state                                                                                                                                                                                                                                     |          | 1100                                   |      | V/µs                |       |  |

| Noise                                        | Output Voltage Noise                                                                                                                  | Differential, Default bias state                                                                                                                                                                                                                       |          |                                        | 90   | nV/ <sub>√</sub> Hz | 4     |  |

| MTPR                                         | Multi Tone Power<br>Ratio                                                                                                             | ADSL2, 25 – 138 kHz<br>VDSL2 17a US0 band, 25 – 138 kHz<br>VDSL2 17a US1 band, 3.75 – 5.2 MHz<br>VDSL2 17a US2 band, 8.5 – 12.0 MHz<br>VDSL2 30a US1 band, 3.75 – 5.2 MHz<br>VDSL2 30a US2 band, 8.5 – 12.0 MHz<br>VDSL2 30a US3 band, 22.8 – 30.0 MHz |          | 85<br>80<br>74<br>66<br>65<br>60<br>55 |      | dBc                 |       |  |

| THD                                          | Total Harmonic<br>Distortion                                                                                                          | Default bias state<br>200 kHz,<br>10 MHz<br>20 MHz<br>30 MHz                                                                                                                                                                                           |          | -89<br>-75<br>-72<br>-71               |      | dBc                 |       |  |

| <ol> <li>Current</li> <li>Current</li> </ol> | tates as selected from <u>Table</u><br>nt going into the control pins<br>nt coming out of the control<br>sted in production. Guarante | <u>2</u> .                                                                                                                                                                                                                                             | <u> </u> | <u>  ··</u>                            | 1    | <u> </u>            |       |  |

Figure 1. Basic Test Circuit

## STATE CONTROL

C1, C0, and CF pins are used as combinatorial logic inputs to control the line driver operating states. The device can be programmed for 4-state or 8-state operation by controlling two or all three of these inputs.

<u>Table 2</u> shows the four states that are available when programming the device using Control 0 and Control 1 pins, a Standby state and three bias states can be programmed.

<u>Table 3</u> shows the eight states that are available with the addition of the fine state control, CF. 8-state operation provides the user with finer bias current steps, including bias steps above and below the 4-state matrix levels. Bias levels increment higher in a linear fashion from step 1 up to step 7. The comparable 4-state matrix states are shown in red.

C0 and C1 have internal pull-down resistors and CF has an internal pull-up resistor to force the default state (as shown in the tables) when no inputs are driven and to allow 4-state control when CF is not used.

| C1 | C0 | State                     | Application |

|----|----|---------------------------|-------------|

| 0  | 0  | High Bias (Default state) | VDSL2 30a   |

| 0  | 1  | Medium Bias               | VDSL2 17a   |

| 1  | 0  | Low Bias                  | ADSL2+      |

| 1  | 1  | Standby                   | —           |

#### Table 2. 4-State Control Matrix

#### Table 3. 8-State Control Matrix

| C1 | C0 | CF | State                        | Application |

|----|----|----|------------------------------|-------------|

| 0  | 0  | 0  | Bias Level 7 (Full bias)     | —           |

| 0  | 0  | 1  | Bias Level 6 (Default state) | VDSL2 30a   |

| 0  | 1  | 0  | Bias Level 5                 | _           |

| 0  | 1  | 1  | Bias Level 4                 | VDSL2 17a   |

| 1  | 0  | 0  | Bias Level 3                 | _           |

| 1  | 0  | 1  | Bias Level 2                 | ADSL2+      |

| 1  | 1  | 0  | Bias Level 1 (Lowest bias)   | —           |

| 1  | 1  | 1  | Standby                      | —           |

**Standby State:** Amplifiers are disabled. Output port presents the impedance of the internal feedback resistors (several kilohms). Device draws lowest current from VS supply.

**Bias States:** Line Driver is active for transmission. States are different only in the amount of bias current to the amplifiers, and therefore power consumption. There is a trade-off between bias current and bandwidth.

# APPLICATIONS

The Le87270 integrates a set of high-power line driver amplifiers that can be connected for full duplex differential line transmissions. The amplifiers are designed to be used with signals up to 30 MHz with low signal distortion.

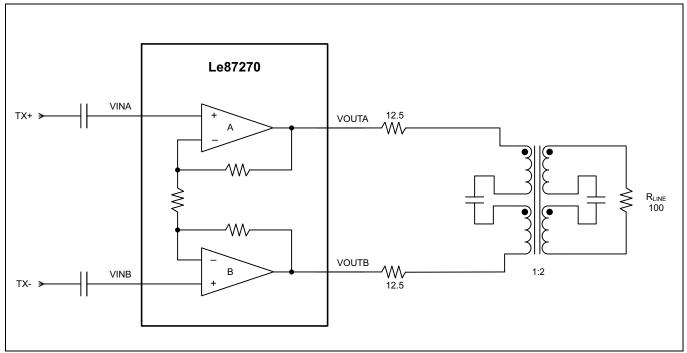

# **Typical Application Circuit**

A typical VDSL2 application interface circuit is shown in Figure 2.

Figure 2. Typical Application Circuit

#### Input Considerations

The driving source impedance should be less than 100 nH to avoid any ringing or oscillation.

#### **Output Driving Considerations**

The internal metallization is designed to carry up to about 75 mA of steady DC current and there is no current limit mechanism. Driving lines with no series resistor is not recommended.

If a DC current path exists between the two outputs, a large DC current can flow. To avoid DC current flow, the most effective solution is to place a DC blocking capacitor in series at the output, as shown in <u>Figure 2</u>.

#### **Power Supplies and Component Placement**

The power supplies should be well by passed close to the Le87270 device. A 2.2  $\mu$ F tantalum capacitor and a 0.1  $\mu$ F ceramic capacitor for the VS supply is recommended.

### **Line Driver Protection**

High voltage transients such as lightning can appear on the telephone lines. Transient protection devices should be used to absorb the transient energy and clamp the transient voltages. The series output termination resistors limit the current going into the line driver and internal clamps. The protection scheme depends on the type of data transformer used and the line protection components used in the front of the data transformer.

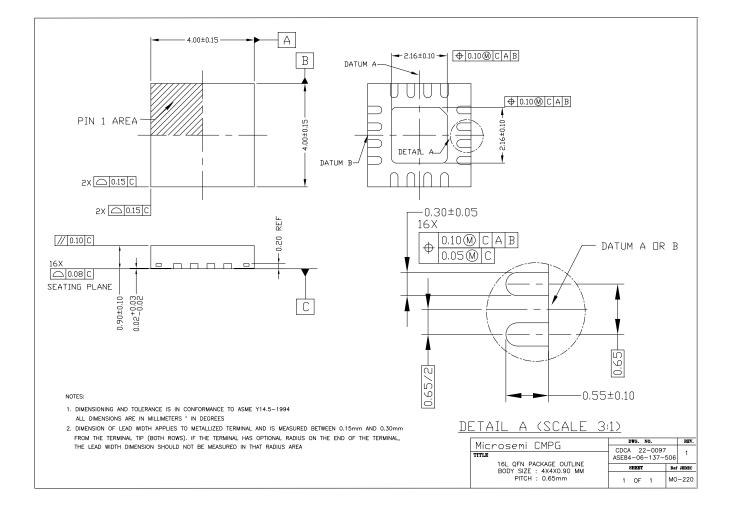

### PHYSICAL DIMENSIONS

### 16-pin QFN

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

#### E-mail: sales.support@microsemi.com

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; Enterprise Storage and Communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at **www.microsemi.com**.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.