#### Octal External Ringing Subscriber Line Audioprocessing Circuit, Next Generation Carrier Chipset (NGCC)

#### **POTS Features**

- Ideal for high density, medium and large line count applications

- · Wideband 16 kHz sampling mode capability

- · API-compatible with VE790 Series designs

- High performance digital signal processor provides programmable control of all major line card functions

- A-law/µ-law and linear codec/filter

- Transmit and receive gain, Two-wire AC impedance, Transhybrid balance, Equalization

- · DC loop feeding

- External battery-backed or earth-backed ringing

- Internal ringing generation

- · Loop supervision and ring-trip detection

- Metering generation and shaping (12 kHz and 16 kHz)

- · Enhanced line control

- DTMF and Modem Tone Detection

- Tone generation (DTMF, FSK, and arbitrary tone)

- Test Tool Box as part of integrated FXS test routines

- Standard PCM and MPI digital interfaces

- General purpose I/O pins, can be used as relay drivers or for control of the Microsemi Driver Test Access Switch Device (DTAS) in a MeLT application

#### **MeLT Features**

- Driver and Multiplexor Control for up to 128 Channels

- Current Sense and Voltage Driver to implement Microsemi's Metallic Line Test Algorithms

- Generation of Wetting Current on dry-DSL or g.fast lines

- Test Tool Box for data capture and manipulation

Document ID#:136868

Version 6

April 2016

### **Ordering Information**

ZL792588GDG2 196-pin BGA<sup>1</sup> Tray

The 196-Pin BGA is a green package that meets RoHS

Directive 2002/95/EC of the European Council to minimize the

environmental impact of electrical equipment.

## **Description**

The ZL79258 Next Generation Octal External Ringing Subscriber Line Audio-processing Circuit (SLAC) device is used in both the FXS or POTS application and in the Metallic Loop Test or MeLT application.

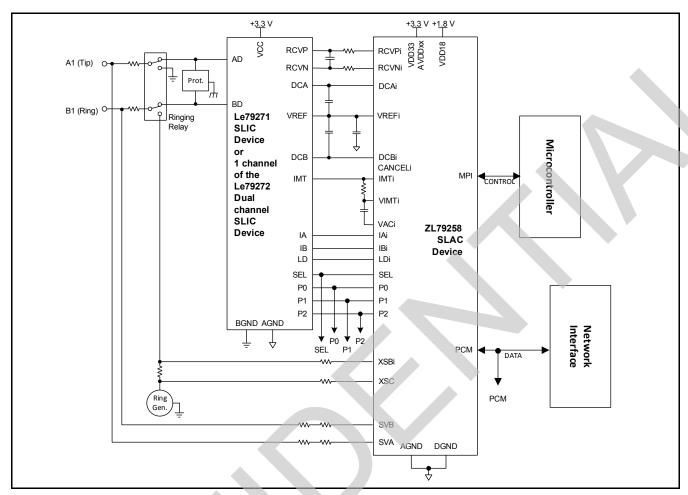

In the POTS application, in combination with the Le79271 SLIC device or Le79272 dual SLIC, the SLAC implements a high density eight-channel universal telephone line interface with wideband capability for internal or external ringing applications. This enables the design of a low cost, high performance, fully software programmable line interface with worldwide applicability. All AC, DC, and signaling parameters are programmable via a microprocessor interface.

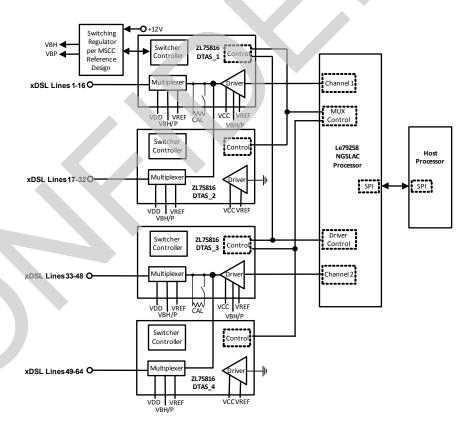

In the MeLT application, in combination with the ZL75816 Driver Test Access Switch (DTAS), implements a complement MeLT test head for up-to 128 channels.

There are different firmware loads for the SLAC for the POTS or MeLT application that are available from Microsemi.

# **Applications**

- POTS

- DSLAM

- DLC, CO

- PBX/KTS

- MeLT

- ADSL or VDSL DSLAM

- VDSL2 or G.Fast DPU

# **Block Diagram - POTS**

# **Block Diagram - MeLT**

# **Change Summary**

Below are the changes from the November 2011 version to April 2016 version.

| Page  | Section | Description                                                                                            |

|-------|---------|--------------------------------------------------------------------------------------------------------|

| All   |         | Latest Microsemi branding.                                                                             |

| 1     |         | Added high level description of MeLT Application                                                       |

| 2     |         | Added MeLT Block Diagram                                                                               |

| 12-14 |         | Added MeLT Description                                                                                 |

| 17    | 3.0     | Changed description of DCA [5:8] and DCB [5:8] to include functionality associated with MELT firmware. |

# **Table of Contents**

| 1.0 Product Description - POTs Application                     | 6  |

|----------------------------------------------------------------|----|

| 1.1 Wideband Codec Mode                                        | 8  |

| 1.2 Features of the ZL79258 SLAC and Le79271/2 SLIC Devices    |    |

| 2.0 Product Description - MeLT Application                     |    |

| 2.1 Features of the ZL79258 SLAC and Le75816 DTAS Device       |    |

| 3.0 Connection Diagrams                                        | 14 |

| 4.0 Pin Descriptions                                           | 16 |

| 5.0 Absolute Maximum Ratings                                   | 19 |

| 5.1 Green Package Assembly                                     |    |

| 6.0 Operating Ranges                                           | 20 |

| 7.0 Programming of the SLAC Parameters in the POTS Application |    |

| 8.0 Electrical Characteristics                                 |    |

| 8.1 Transmission Specifications in the POTS Application        |    |

| 8.2 Transmit and Receive Paths                                 |    |

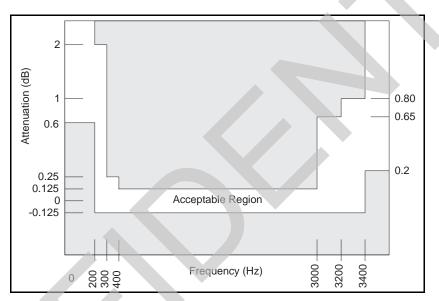

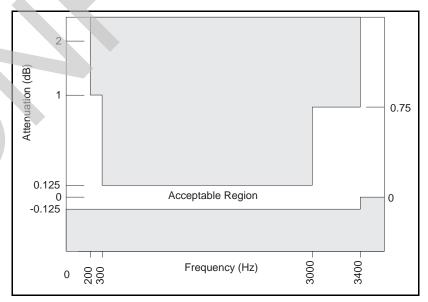

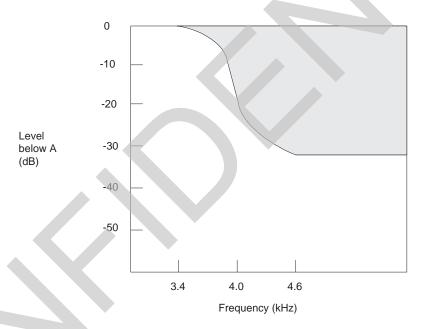

| 8.3 Attenuation Distortion                                     | 24 |

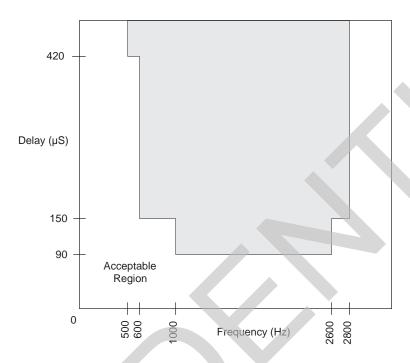

| 8.4 Group Delay Distortion                                     |    |

| 8.5 Single Frequency Distortion                                |    |

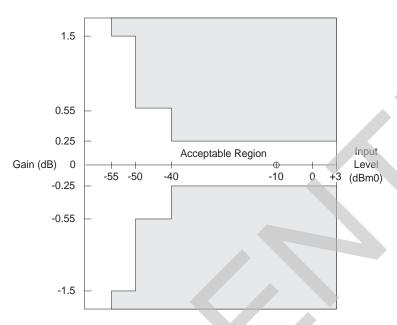

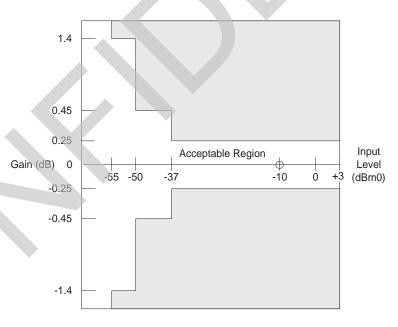

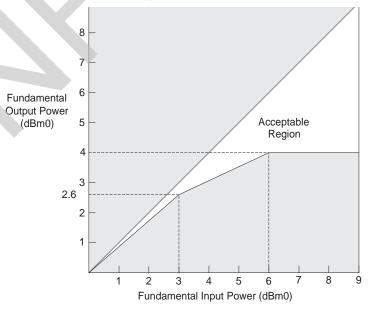

| 8.6 Gain Linearity                                             |    |

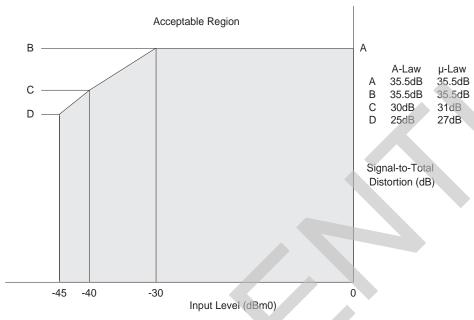

| 8.7 Total Distortion Including Quantizing Distortion           |    |

| 8.8 Overload Compression                                       | 28 |

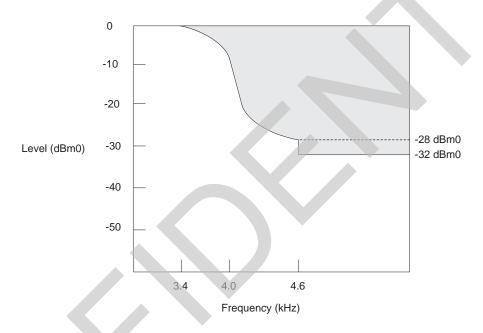

| 8.9 Discrimination Against Out-of-Band Input Signals           |    |

| 8.10 Spurious Out-of-Band Signals at the Analog Output         |    |

| 9.0 Reset at Power-Up                                          |    |

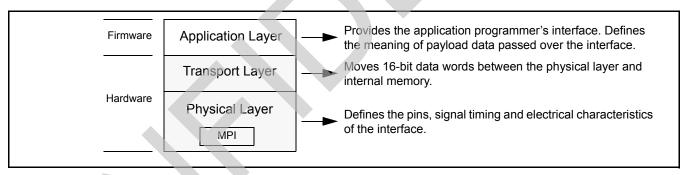

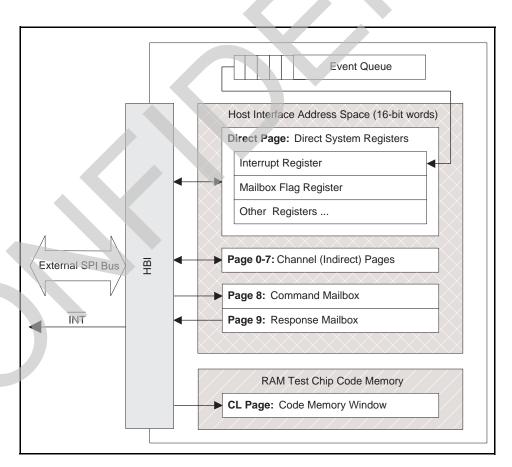

| 10.0 Host Bus Control Interface (HBI) Overview                 |    |

| 10.1 Transport Layer                                           |    |

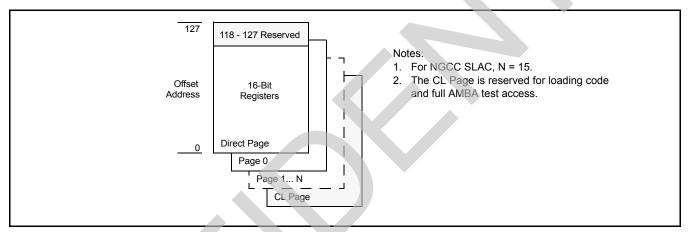

| 10.1.1 Interface Addressing                                    |    |

| 10.1.2 Command Structure                                       |    |

| 10.2.1 Code Load Integrity                                     | 38 |

| 10.2.2 Host Boot Procedure                                     |    |

| 10.2.3 Partial Code Load Procedure                             |    |

| 10.3 Application Layer                                         |    |

| 10.4 Physical Layer                                            |    |

| 10.4.1 Microprocessor Interface (MPI)                          | 40 |

| 11.0 PCM Highway                                               | 46 |

| 11.1 PCM Transmit Interface                                    | 46 |

| 11.2 PCM Receive Interface                                     |    |

| 11.3 PCM Interface Timing4                                     | 49 |

| 12.0 P-Bus and GPIO Interfaces                                 |    |

| 12.1 SLIC Device Bus Timing Specifications                     |    |

| 12.2 Relay Drivers                                             |    |

| 13.0 Physical Dimensions                                       |    |

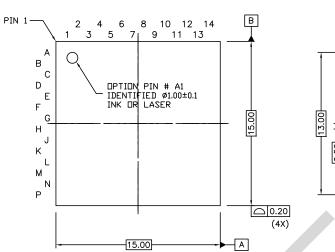

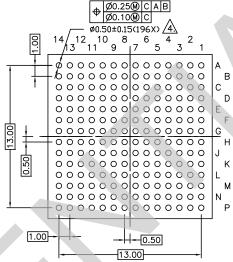

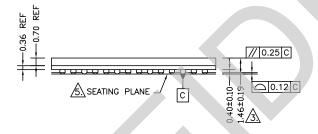

| 13.1 196-Pin BGA                                               | 57 |

# **List of Figures**

| Figure 2 - NGCC System with External Ringing                               | . 8 |

|----------------------------------------------------------------------------|-----|

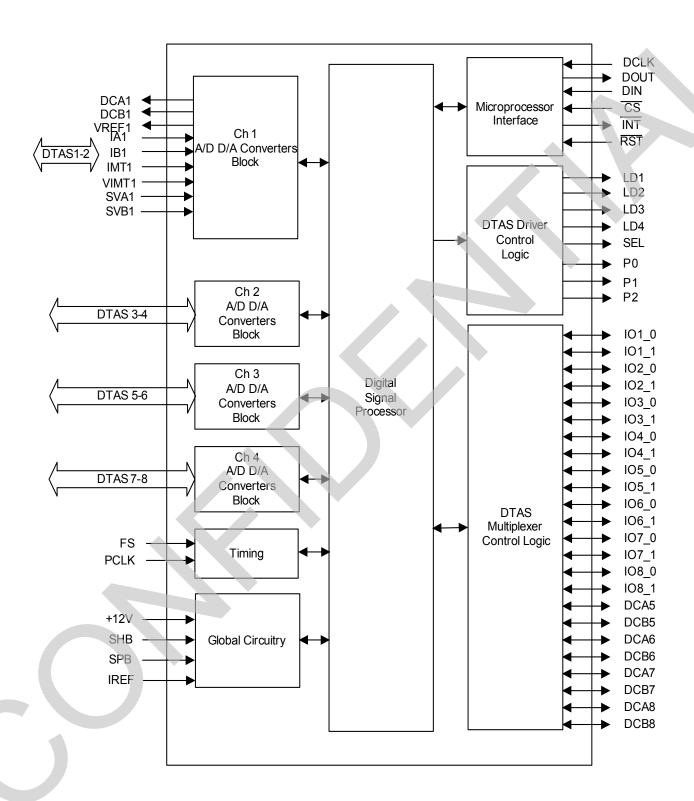

| Figure 3 - ZL79258 Device Internal Block Diagram - POTS Application        | . 9 |

| Figure 4 - 64 Channel MeLT System                                          |     |

| Figure 5 - ZL79258 Device Internal Block Diagram - MeLT Application        | 12  |

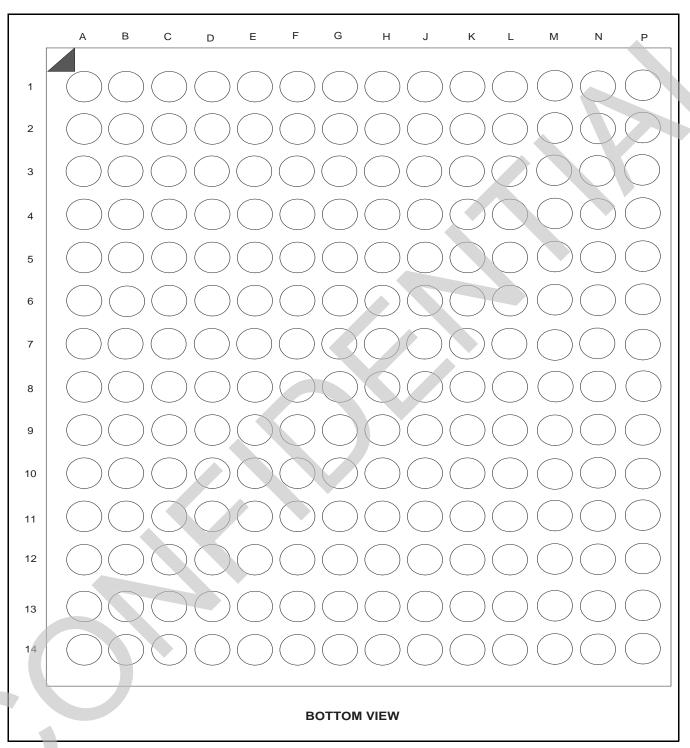

| Figure 6 - 196-Pin BGA Diagram                                             |     |

| Figure 7 - Narrowband Transmit Path Attenuation vs. Frequency              |     |

| Figure 8 - Narrowband Receive Path Attenuation vs. Frequency               | 24  |

| Figure 9 - Group Delay Distortion                                          |     |

| Figure 10 - A-law Gain Linearity with Tone Input (Both Paths)              |     |

| Figure 11 - μ-law Gain Linearity with Tone Input (Both Paths)              |     |

| Figure 12 - Total Distortion with Tone Input, Both Paths                   |     |

| Figure 13 - A/A Overload Compression                                       |     |

| Figure 14 - Discrimination Against Out-of-Band Signals                     |     |

| Figure 15 - Spurious Out-of-Band Signals                                   |     |

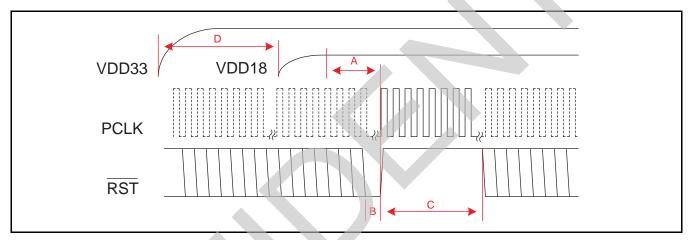

| Figure 16 - Reset Sequence when VDD33 and VDD18 are Powered Up Separately  |     |

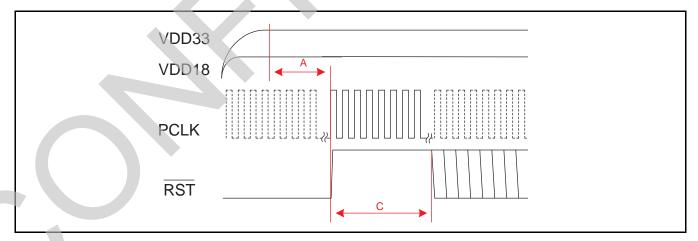

| Figure 17 - Reset Sequence when VDD33 and VDD18 are Powered Up Together    |     |

| Figure 18 - Host Bus Interface Layers                                      |     |

| Figure 19 - Host Bus Interface Address Model                               |     |

| Figure 20 - NGCC SLAC Programmer's Model                                   |     |

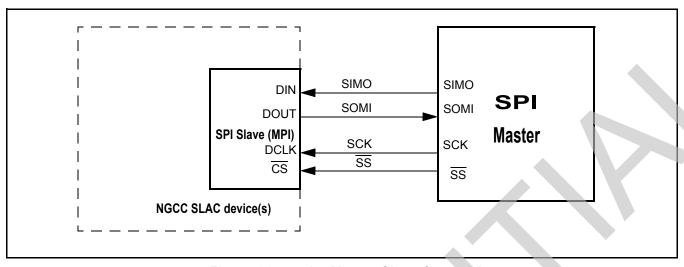

| Figure 21 - 4-wire Master-Slave Connections                                | 41  |

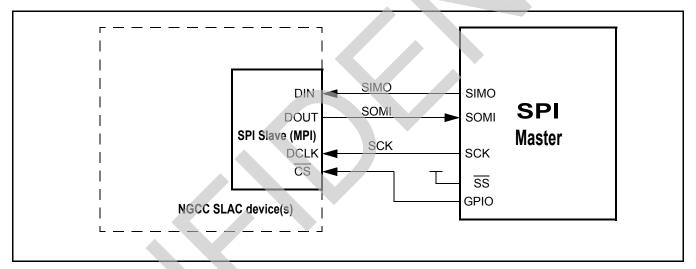

| Figure 22 - 3-wire Master-Slave Connections                                |     |

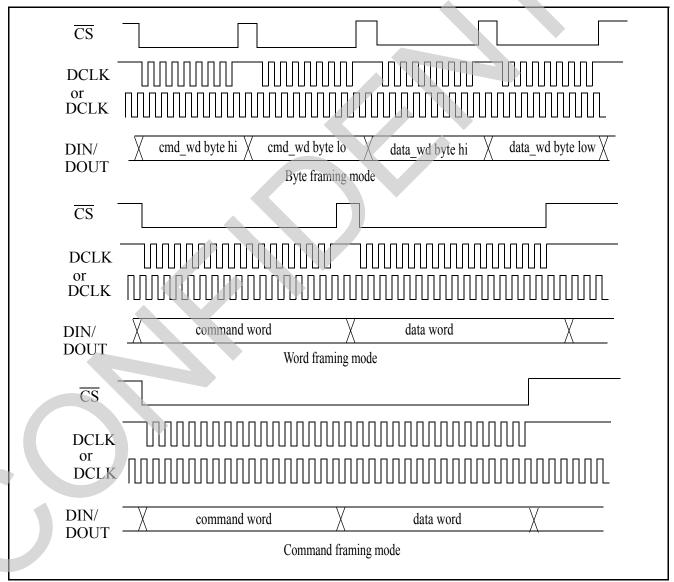

| Figure 23 - CS Framing Modes                                               |     |

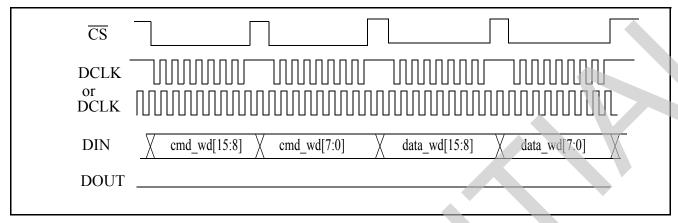

| Figure 24 - One Data Word Write in Byte Framing Mode                       |     |

| Figure 25 - One Data Word Read in Word Framing Mode                        |     |

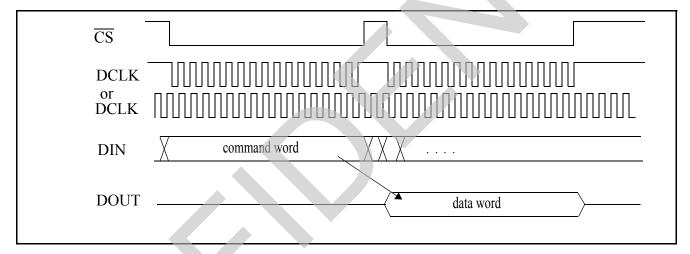

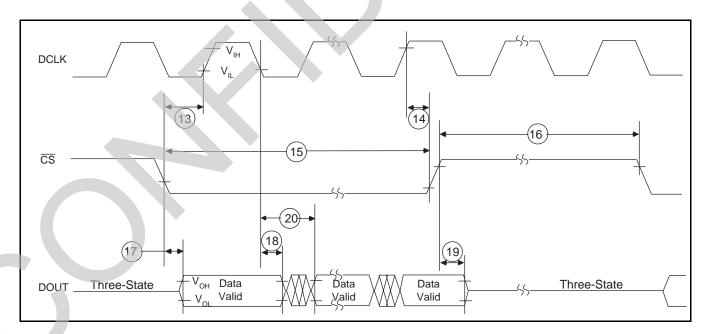

| Figure 26 - Microprocessor Interface (Input Mode)                          |     |

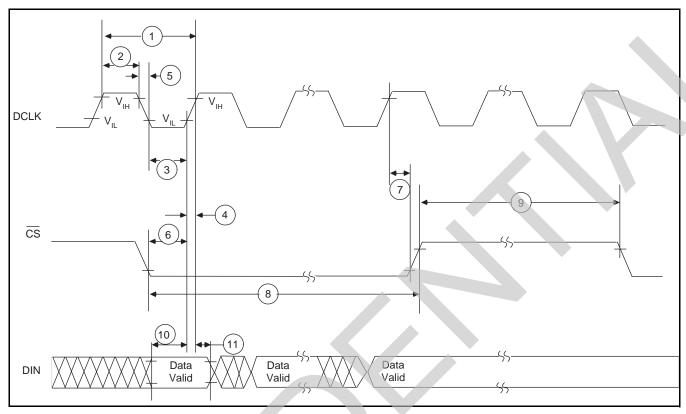

| Figure 27 - Microprocessor Interface (Output Mode)                         |     |

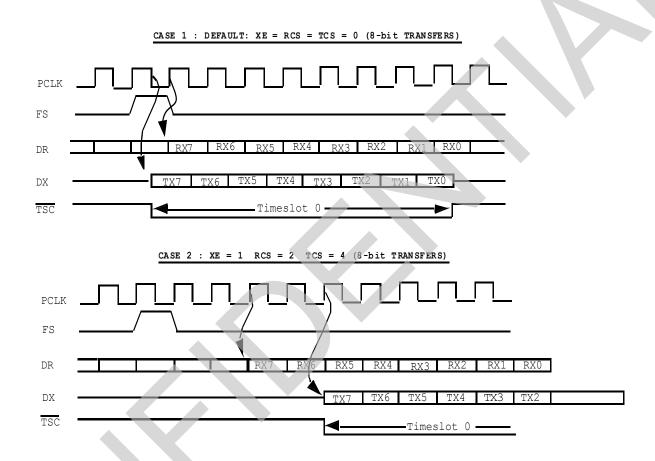

| Figure 28 - PCM Highway 8-bit Transfers                                    |     |

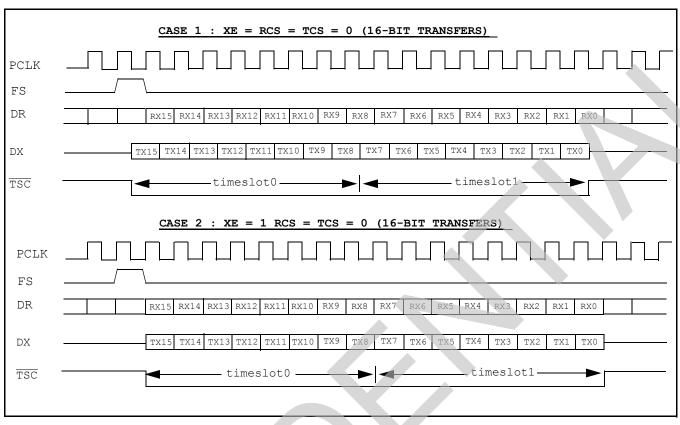

| Figure 29 - PCM Highway 16-bit Transfers                                   |     |

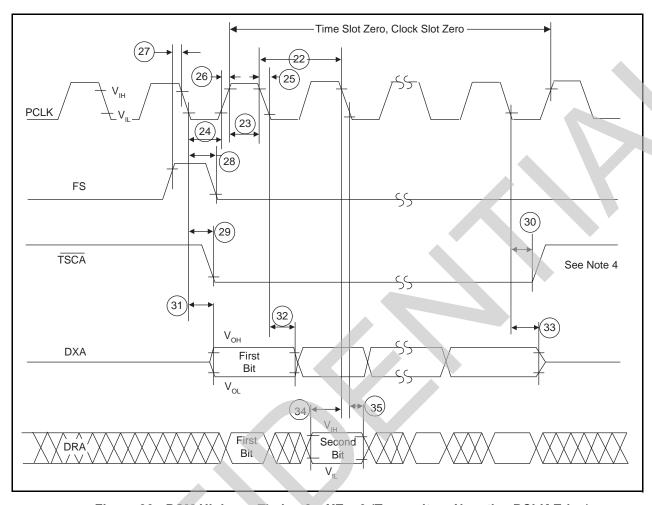

| Figure 30 - PCM Highway Timing for XE = 0 (Transmit on Negative PCLK Edge) |     |

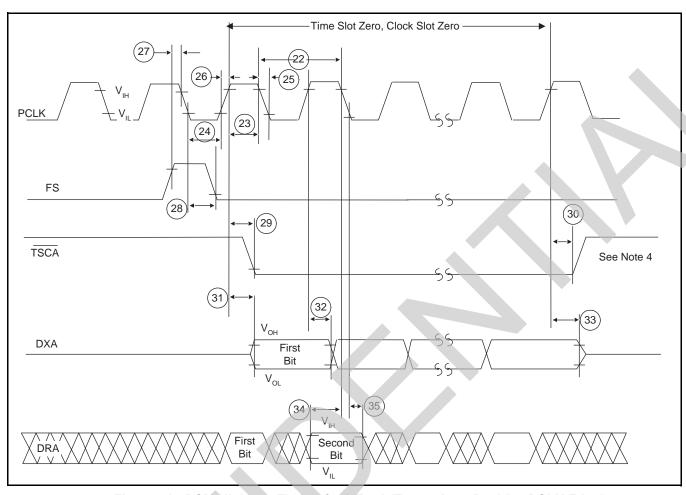

| Figure 31 - PCM Highway Timing for XE = 1 (Transmit on Positive PCLK Edge) |     |

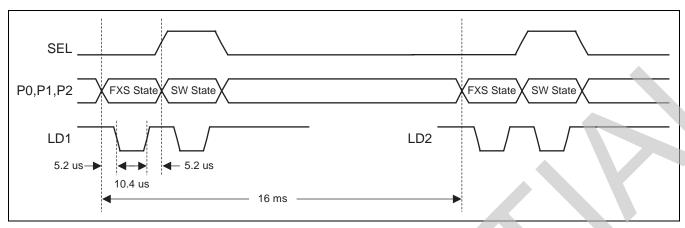

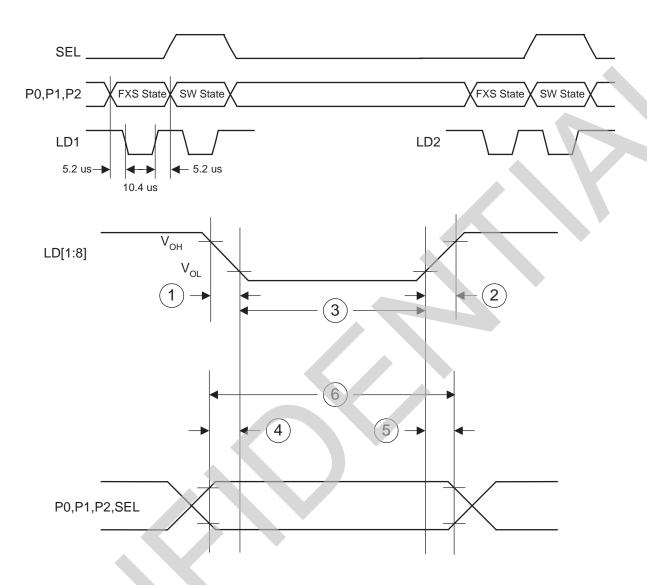

| Figure 32 - Channel Timing for P-Bus SLIC Interface                        |     |

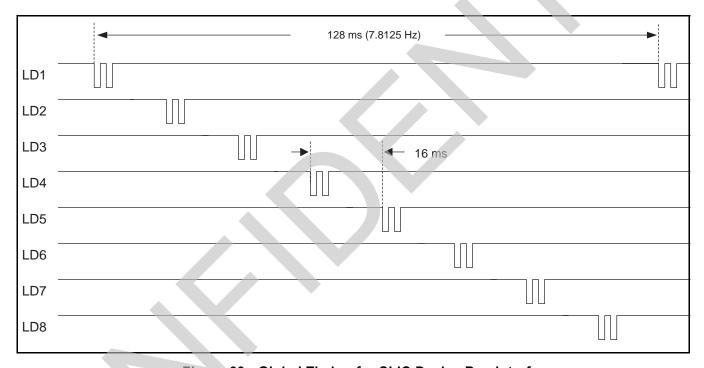

| Figure 33 - Global Timing for SLIC Device Bus Interface                    |     |

| Figure 34 - SLIC Device Bus Timing Waveform                                |     |

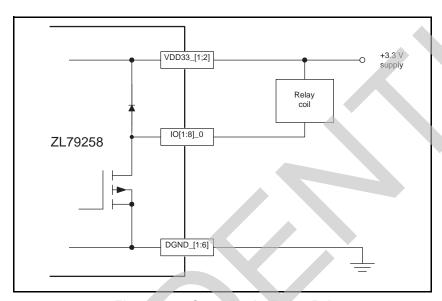

| Figure 35 - Open Drain Relay Drivers                                       | 56  |

# 1.0 Product Description - POTs Application

The Next Generation Carrier Chipset integrates all the functions of eight voice subscriber lines. Eight Le79271 SLIC devices or 4 Le79272 dual DSLIC devices and one ZL79258 Octal SLAC device make up the chipset.

- The Le79271 SLIC single channel device or Le79272 dual channel device is a high voltage, bipolar IC that

drives the subscriber line and senses line conditions.

- The ZL79258 SLAC device is a low voltage CMOS IC that provides conversion and DSP functions for eight channels and senses line conditions.

The SLIC device is built with a high voltage bipolar technology to provide the power necessary to drive a wide variety of subscriber lines. It can be programmed by the SLAC device to operate in eight different modes that control power consumption and signaling. The SLIC design is based on a voltage feed, current sense architecture.

The SLAC device processes information regarding line voltage and loop current from the SLIC device. The SLIC device senses the A and B lead currents, computes the metallic loop current and feeds it in analog form to the SLAC device. The SLAC device also senses A and B lead voltages and external ringing voltages and monitors battery voltage levels.

The output signals supplied by the SLAC device to the SLIC device are:

- A lead (DCA) and B lead (DCB) DC voltages for DC feed or internal ringing.

- AC transmission and 12 or 16 kHz metering signals (on the RCVN, RCVP pins).

The SLAC device controls the SLIC device mode via the SLIC control bus P0-P2, SEL and the load signal LD.

The SLAC device contains high-performance circuits that provide A/D and D/A conversion for voice (codec/filter), DC-feed control, ringing, and supervision signals. The SLAC device contains a DSP core that handles signaling, DC-feed, and supervision for all eight channels. The DSP core also interfaces to a standard PCM/MPI backplane. These functions involve converting an analog voice signal into digital PCM samples and converting digital PCM samples back into an analog signal. During conversion, digital filters are used to band-limit the voice signals. The PCM codes can be:

- · 8-bit companded A-law with 8 kHz sampling

- 8-bit companded µ-law with 8 kHz sampling

- 16-bit linear two's-complement with 8 kHz sampling

- 16-bit linear two's-complement with 16 kHz sampling (wideband mode)

The SLAC device provides a software configurable solution to the BORSCHT functions as well as complete programmable control over subscriber line DC-feed characteristics, such as current limit and feed resistance. In addition, the SLAC device provides extensive loop supervision capability including off-hook, ring-trip and ground-key detection. Detection thresholds for these functions are programmable. A programmable debounce timer is available that eliminates false detection due to contact bounce.

For external ringing the SLAC device provides a relay driver to operate an electromechanical relay. Advanced algorithms in the SLAC device controls ringing entry and exit in a manner to minimize transients. Ringing entry occurs at DC feed levels and ringing exit occurs at zero current, whether due to ring-trip or the end of the ringing cadence. Battery-backed and earth-backed ringing architectures are supported. An integrated ring-trip detection circuit supports both architectures.

User-programmable filters include receive and transmit gain, transhybrid balance, two-wire termination impedance, and frequency attenuation (equalization) of the receive and transmit signals. All programmable digital filter coefficients can be calculated using WinSLAC™ software. This PC software allows the designer to enter a description of system requirements, WinSLAC™ then computes the necessary coefficients and plots the predicted system results.

The main functions that can be observed and/or controlled through the SLAC device backplane interface are:

- Narrowband 3.4 kHz or wideband 7.0 kHz codec modes

- DC-feed characteristics

- · Ground-key detection

- Off-hook detection

- DTMF tone detection

- · Modem tone detection

- Metering signal

- DC voltages on A and B leads

- · Subscriber line voltage and currents

- Ring-trip detection

- · Abrupt and smooth reversal

- Subscriber line impedance matching

- · Ringing signal generation

- · External ringing control

These functions are all handled in a manner to limit voice service transients.

The SLAC device requires two power supplies. Low power consumption is achieved by use of a separate +1.8 VDC supply for the DSP core; the analog and digital I/O circuitry is powered from a +3.3 VDC supply.

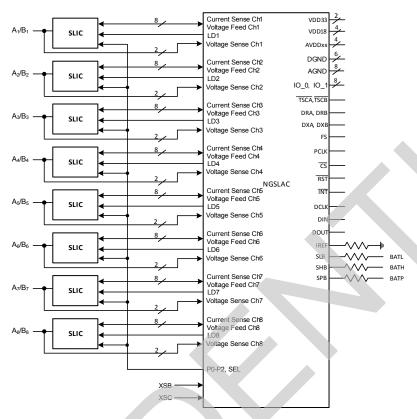

Figure 2 presents an overview of the NGCC system with the ZL79258 External Ringing SLAC device. Refer to the Next Generation Carrier Chipset Hardware Design Guide (Document ID 126583) for detailed Application Circuits and a Parts List.

Figure 2 - NGCC System with External Ringing

#### 1.1 Wideband Codec Mode

The ZL79258 device can be operated in a wideband mode to provide better voice quality. Wideband mode is intended to be used with a packet based processor with an adaptive echo canceller algorithm.

When wideband mode is selected, the nominal voice bandwidth is doubled to 7000 Hz. The wideband mode can be selected on a per channel basis. In this mode, internal clocks are doubled, increasing the sampling rates of the internal digital filters. Narrowband and wideband modes require their own unique set of coefficients. Therefore if switching between PCM operating modes on a given channel, the coefficients must be reprogrammed.

In wideband mode the PCM interface transmits and receives two evenly spaced sets of 16-bit timeslots in each frame. The user selects one timeslot during the first 62.5  $\mu$ S of the frame. The first set of 16-bits will transmit or receive starting in this timeslot. The timeslot for the second set of 16-bits is generated automatically and placed 125/2  $\mu$ S from the first timeslot.

Figure 3 - ZL79258 Device Internal Block Diagram - POTS Application

#### 1.2 Features of the ZL79258 SLAC and Le79271/2 SLIC Devices

- Performs all battery feed, ringing, signalling, and hybrid functions

- Two chip solution supports high density, multi-channel architecture

- Supports two negative batteries

- Single hardware design meets multiple country requirements through software programming of:

- Ringing waveform and frequency

- · DC loop-feed characteristics and current-limit

- · Loop-supervision detection thresholds

- Off-hook debounce circuit

- Ground-key and ring-trip filters

- · Off-hook detect de-bounce interval

- · Two-wire AC impedance

- Transhybrid balance impedance

- · Transmit and receive gains

- Equalization

- Digital I/O pins

- A-law/µ-law and linear selection

- Supports wideband 7.0 kHz codec mode

- Supports internal ringing with DC bias

- Programmed ringing cadence

- Self-contained ringing generation and control

- Integrated ring-trip filter and software enabled manual or automatic ring-trip mode

- Supports external ringing

- Controlled ringing entry and exit

- · Integrated ring-trip filter

- · Integrated relay driver

- Supports metering generation with envelope shaping

- · Programmable metering cadencing

- Smooth polarity reversal

- Supports both loop-start and ground-start signalling

- · SPI and PCM interfaces

- Exceeds LSSGR and CCITT central office requirements

- On-hook transmission

- Power/service denial mode

- Line-feed characteristics independent of battery voltage

- Low idle-power per line

- Compatible with inexpensive protection networks

- Can monitor and/or drive A and B lead independently

- Automatic CID and Signalling and FSK and DTMF modes

- Tone generation

- Howler

- Call Progress

- DTMF

- Modem support

- DTMF tone detection

- · Dial Pulse and Flash detection

- · Power-cross, fault, and foreign voltage detection

- Small physical size

# 2.0 Product Description - MeLT Application

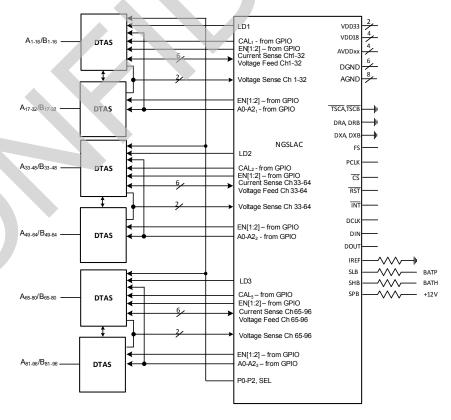

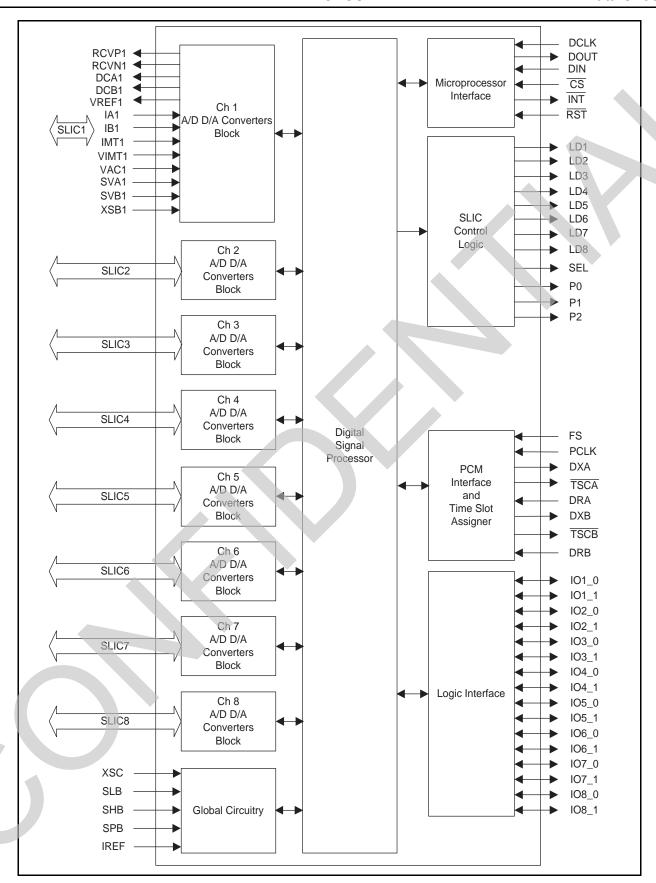

The Microsemi MeLT solution is based on the ZL75816 Driver and Test Access Switch (DTAS) and the Le79258 NGSLAC Processor. The ZL75816 Driver, Test Access Switch (DTAS) multiplexes 16 G.Fast or DSL lines to a single MeLT test channel. The DTAS is comprised of 16 channels of access switches multiplexed to a single high voltage driver connected to a SLAC port. It is also possible to expand the line count to 32 DSL/G.Fast channels per SLAC port by connecting two DTAS devices together, as shown in Figure 4. The device has integrated secondary protection so no per channel secondary protection device is required. The DTAS also includes a switching power supply controller circuit that can generate the positive and negative battery voltages used by the line testing function. Only one DTAS device needs to be fitted with the external power supply components and will generate those voltages with enough current to support up to 128 DSL channels.

The NGSLAC Processor provides low level processing, control functions, and the required A/D and D/A communication channels. One channel of the NGSLAC Processor is required for each driver. This solution is a highly integrated chip set that address the requirement of consuming a very small PCB area with a minimal number of devices.

Microsemi's MeLT solution is supported by the Le71SK7920THM firmware. This firmware package consists of the VoicePath™ Application Program Interface (VP-API-II) and VoicePath™ Host Test Library (HTL). Test diagnostics are comprehensive and are intended to be consistent with ITU-T G.996.2, BBF TR298 and Deutsche Telecom 183TR20 requirements

Figure 4 - 64 Channel MeLT System

Figure 5 - ZL79258 Device Internal Block Diagram - MeLT Application

### 2.1 Features of the ZL79258 SLAC and Le75816 DTAS Device

- Cost-effective, highly-integrated, highly-featured, G.Fast and xDSL line test solution for worldwide applications

- · Extremely small PCB area required

- Comprehensive test diagnostics that are consistent with ITU-T G.996.2 and Deutsche Telecom 183TR20 requirements

- Simplified programming interface

- · Fully validated test routines

- · Software data sheet with published accuracies

# 3.0 Connection Diagrams

Figure 6 - 196-Pin BGA Diagram

| BGA<br>Pin# | Pin Name      | BGA<br>Pin# | Pin Name      | BGA<br>Pin# | Pin Name | BGA<br>Pin# | Pin Name | BGA<br>Pin# | Pin Name |

|-------------|---------------|-------------|---------------|-------------|----------|-------------|----------|-------------|----------|

| A1          | VAC1          | D1          | CANCEL2       | G1          | VAC2     | K1          | VIMT3    | N1          | IMT4     |

| A2          | VIMT1         | D2          | SVB2          | G2          | DCA2     | K2          | DCB3     | N2          | SVA4     |

| A3          | IMT1          | D3          | VREF1         | G3          | VREF2    | K3          | VREF3    | N3          | VREF4    |

| A4          | CANCEL1       | D4          | XSB1          | G4          | IA2      | K4          | XSB3     | N4          | IA4      |

| A5          | VDD18_4A      | D5          | AVDD12A       | G5          | AGND2    | K5          | AVDD34A  | N5          | DGND_2A  |

| A6          | TSCB          | D6          | DEBUG_<br>CLK | G6          | IO1_1    | K6          | DGND_2   | N6          | LD3      |

| A7          | DRA           | D7          | TSCA          | G7          | IO2_0    | K7          | 104_0    | N7          | P2       |

| A8          | PCLK          | D8          | DCLK          | G8          | IO8_1    | K8          | IO5_0    | N8          | SEL      |

| A9          | DIN           | D9          | RST           | G9          | IO7_1    | K9          | DGND_3   | N9          | LD6      |

| A10         | VDD18_3       | D10         | AVDD78A       | G10         | SLB      | K10         | AVDD56   | N10         | DGND_4   |

| A11         | DCB8          | D11         | XSB8          | G11         | IB7      | K11         | XSB6     | N11         | IB5      |

| A12         | DCA8          | D12         | RCVN8         | G12         | RCVN7    | K12         | RCVN6    | N12         | RCVN5    |

| A13         | VAC8          | D13         | DCA7          | G13         | SVB7     | K13         | SVA6     | N13         | SVB5     |

| A14         | VIMT8         | D14         | VAC7          | G14         | CANCEL7  | K14         | IMT6     | N14         | DCA5     |

| B1          | DCA1          | E1          | IMT2          | H1          | CANCEL3  | L1          | VAC3     | P1          | VIMT4    |

| B2          | SVB1          | E2          | SVA2          | H2          | SVB3     | L2          | DCA3     | P2          | VAC4     |

| В3          | RCVN1         | E3          | RCVN2         | H3          | RCVN3    | L3          | RCVN4    | P3          | DCA4     |

| B4          | IB1           | E4          | XSB2          | H4          | IB3      | L4          | XSB4     | P4          | DCB4     |

| B5          | VDD18_4       | E5          | AVDD12        | H5          | AGND2A   | L5          | AGND3    | P5          | VDD18_1  |

| B6          | DRB           | E6          | VDD33 2       | H6          | IO2_1    | L6          | AGND4    | P6          | LD2      |

| B7          | DXA           | E7          | DGND 6        | H7          | 104_1    | L7          | VDD33_1  | P7          | LD4      |

| B8          | FS            | E8          | IO8_0         | H8          | 105_1    | L8          | RSVD_O   | P8          | LD5      |

| В9          | DOUT          | E9          | AGND8         | H9          | 106_1    | L9          | AGND5    | P9          | LD7      |

| B10         | DGND_5        | E10         | AVDD78        | H10         | SPB      | L10         | AVDD56A  | P10         | VDD18_2  |

| B11         | IB8           | E11         | XSB7          | H11         | IA6      | L11         | XSB5     | P11         | CANCEL5  |

| B12         | VREF8         | E12         | VREF7         | H12         | VREF6    | L12         | VREF5    | P12         | IMT5     |

| B13         | SVA8          | E13         | DCB7          | H13         | DCA6     | L13         | SVB6     | P13         | VIMT5    |

| B14         | IMT8          | E14         | VIMT7         | H14         | VAC6     | L14         | CANCEL6  | P14         | VAC5     |

| C1          | DCB1          | F1          | VIMT2         | J1          | IMT3     | M1          | CANCEL4  |             |          |

| C2          | SVA1          | F2          | DCB2          | J2          | SVA3     | M2          | SVB4     |             |          |

| C3          | RCVP1         | F3          | RCVP2         | J3          | RCVP3    | M3          | RCVP4    |             |          |

| C4          | IA1           | F4          | IB2           | J4          | IA3      | M4          | IB4      |             |          |

| C5          | DGND_1        | F5          | IREF          | J5          | AVDD34   | M5          | AGND4A   |             |          |

| C6          | DEBUG_<br>IO  | F6          | AGND1         | J6          | IO3_1    | M6          | LD1      |             |          |

| C7          | DXB           | F7          | IO1_0         | J7          | IO3_0    | M7          | P1       | 7           |          |

| C8          | <del>CS</del> | F8          | IO7_0         | J8          | 106_0    | M8          | P0       |             |          |

| C9          | INT           | F9          | AGND7         | J9          | AGND6    | M9          | LD8      |             |          |

| C10         | AGND8A        | F10         | XSC           | J10         | SHB      | M10         | AGND5A   | 1           |          |

| C11         | IA8           | F11         | IA7           | J11         | IB6      | M11         | IA5      | 1           |          |

| C12         | RCVP8         | F12         | RCVP7         | J12         | RCVP6    | M12         | RCVP5    | 1           |          |

| C13         | SVB8          | F13         | SVA7          | J13         | DCB6     | M13         | SVA5     | 1           |          |

| C14         | CANCEL8       | F14         | IMT7          | J14         | VIMT6    | M14         | DCB5     |             |          |

F14 IMT7 J14 VIMT6 M14 DCB5

Table 1 - 196-Pin BGA Pin Numbers and Pin Names

# 4.0 Pin Descriptions

| Pin Name                                   | Pin#                                        | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------|---------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND[1:8]                                  | F6, G5, L5,<br>L6, L9, J9,<br>F9, E9        |                  | Analog ground. Separate analog and digital grounds are provided to allow noise isolation,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AGND2A,<br>AGND4A,<br>AGND5A,<br>AGND8A    | H5, M5,<br>M10, C10                         | Ground           | however the grounds must be connected together on the circuit board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AVDD12,<br>AVDD34,<br>AVDD56<br>AVDD78     | E5, J5, K10,<br>E10                         | Comple           | +3.3 VDC analog power supply inputs. For best performance, all of the AVDD and VDD33 power supply pins should be connected together at the device. Four decoupling capacitors should be                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AVDD12A,<br>AVDD34A,<br>AVDD56A<br>AVDD78A | D5, K5, L10,<br>D10                         | Supply           | used. Place a decoupling capacitor near AVDD12, AVDD34, AVDD56, and AVDD78 AVDD12A, AVDD34A, AVDD56A, and AVDD78A do not require their own decoupling capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CANCEL[1:8]                                | A4, D1, H1,<br>M1, P11,<br>L14, G14,<br>C14 | Output           | Metering cancellation output. If metering is used, connect a capacitor from this pin to the respective channel's IMT pin. If metering is not used, let this pin float.  This pin is not used by the MeLT application.                                                                                                                                                                                                                                                                                                                                                                                            |

| <del>CS</del>                              | C8                                          | Input            | MPI interface chip select. A logic low placed on this pin enables serial data transmission into DIN or out of the DOUT port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DCA[1:4]                                   | B1, G2, L2,<br>P3,                          | Output           | DC feed and low-frequency voltage control of the SLIC device's A lead amplifiers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DCA[5:8]                                   | N14, H13,<br>D13, A12                       | Output           | FXS Firmware: DC feed and low-frequency voltage control of the SLIC device's A lead amplifiers.  MeLT Firmware: GPIO for DTAS Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DCB[1:4]                                   | C1, F2, K2,<br>P4,                          | Output           | DC feed and low-frequency voltage control of the SLIC device's B lead amplifiers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DCB[5:8]                                   | M14, J13,<br>E13, A11                       | Output           | FXS Application: DC feed and low-frequency voltage control of the SLIC device's A lead amplifiers.  MeLT Application: GPIO for DTAS Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DCLK                                       | D8                                          | Input            | MPI interface data clock. Provides data control for MPI interface control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DEBUG_CLK                                  | D6                                          | Input            | DEBUG Clock. This node needs to be tied to VDD33 through a 0 $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DEBUG_IO                                   | C6                                          | Input/Out<br>put | DEBUG input output. This node needs to be tied to DGND through a 0 $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DGND_[1:6]                                 | C5, K6, K9,<br>N10, B10,<br>E7              | Ground           | Digital ground. Separate analog and digital grounds are provided to allow noise isolation, however the grounds must be connected together on the circuit board.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DGND_2A                                    | N5<br>A9                                    | Input            | MPI interface control data input. Control data is serially written into the ZL79258 device via the DIN pin with the MSB first. DIN can be tied to DOUT for a single bi-directional interface. The data clock (DCLK) determines the data rate.                                                                                                                                                                                                                                                                                                                                                                    |

| DOUT                                       | В9                                          | Output           | MPI interface control data output. Control data is serially read out of the ZL79258 device via the DOUT pin with the MSB first. DOUT can be tied to DIN for a single bi-directional interface. The data clock (DCLK) determines the data rate. DOUT is high impedance except when data is being transmitted from the ZL79258 device under control of CS.                                                                                                                                                                                                                                                         |

| DRA, DRB                                   | A7, B6                                      | Input            | PCM highway data receive ports. The receive PCM data is input serially through the DRA or DRB ports. Data is always received with the most significant bit first. For compressed signals, 1 byte of data is received every 125 µs at the PCLK rate. In the Linear mode, 2 consecutive bytes of data for each channel are received every 125 µs at the PCLK rate. In Wideband mode, the frame sync stays at 8 kHz, the ZL79258 operates internally at 16 kHz and outputs data twice per frame in evenly spaced timeslots. If an input is not used, tie to DGND.  These pins are not used by the MeLT application. |

| Pin Name  | Pin#                                        | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|---------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DXA, DXB  | B7, C7                                      | Output           | PCM highway data transmit ports. The transmit PCM data is transmitted serially through the DXA or DXB ports. Data is always transmitted most significant bit first. The output is available every 125 µs and the data is shifted out in 8-bit (16-bit in Linear mode) bursts at the PCLK rate. In Wideband mode, the frame sync stays at 8 kHz, the ZL79258 operates internally at 16 kHz and outputs data twice per frame in evenly spaced timeslots. DXA and DXB are high impedance between bursts and while the device is in the inactive mode. If an output is not used, let the pin float. |

|           |                                             |                  | These pins are not used by the MeLT application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FS        | В8                                          | Input            | PCM highway frame sync. PCM operation is selected by the presence of an 8 kHz frame sync signal on this pin in conjunction with the PCM clock on the PCLK pin. This 8 kHz pulse identifies the beginning of a frame. The ZL79258 device references individual timeslots with respect to this input, which must be synchronized to PCLK.                                                                                                                                                                                                                                                         |

| IA[1:8]   | C4, G4, J4,<br>N4, M11,<br>H11, F11,<br>C11 | Input            | Input current is proportional to current in SLIC's A lead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IB[1:8]   | B4, F4, H4,<br>M4, N11,<br>J11, G11,<br>B11 | Input            | Input current is proportional to current in SLIC's B lead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IMT[1:8]  | A3, E1, J1,<br>N1, P12,<br>K14, F14,<br>B14 | Input            | Input current is proportional to the differential current in the SLIC's AD and BD leads. AGND on this node indicates a SLIC thermal overload condition.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ĪNT       | C9                                          | Output           | Interrupt. When a subscriber line requires service, this pin goes to a logic 0 to interrupt a high level processor. Logic drive is selectable between open drain and TTL-compatible outputs.                                                                                                                                                                                                                                                                                                                                                                                                    |

| IO[1:8]_0 | F7, G7, J7,<br>K7, K8, J8,<br>F8, E8        | Input/Out<br>put | General purpose logic input/output and relay driver port. These pins can be programmed as an input or an output. These pins can be programmed as an open drain 50 mA relay driver. Unused pins should either be tied to AGND through a 10 K $\Omega$ resistor or programmed as low outputs.                                                                                                                                                                                                                                                                                                     |

| IO[1:8]_1 | G6, H6, J6,<br>H7, H8, H9,<br>G9, G8        | Input/Out put    | General purpose logic input/output. These pins can be programmed as an input or an output. Unused pins should either be tied to AGND through a 10 K $\Omega$ resistor or programmed as low outputs.                                                                                                                                                                                                                                                                                                                                                                                             |

| IREF      | F5                                          | Input            | External resistor (R <sub>REF</sub> ) connected between this pin and analog ground generates an accurate, on-chip reference current for the A/D's and D/A's on the ZL79258 device.                                                                                                                                                                                                                                                                                                                                                                                                              |

| LD[1:8]   | M6, P6, N6,<br>P7, P8, N9,<br>P9, M9        | Output           | Logic output that controls data transfer into the SLIC device. When LD is Low, the data on outputs P0–P2 is transferred to the respective data latches as directed by the SEL pin. When LD is High, the data is locked in the latches.                                                                                                                                                                                                                                                                                                                                                          |

| PCLK      | A8                                          | Input            | PCM highway clock. A valid PCLK is required for overall device operation. PCLK determines the rate at which PCM data is serially shifted into or out of the PCM ports. The minimum clock frequency for linear/companded data is 1.536 MHz.                                                                                                                                                                                                                                                                                                                                                      |

| P[0:2]    | M8, M7, N7                                  | Output           | P-bus. Controls the operating modes of the SLIC devices connected to the ZL79258 device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RST       | D9                                          | Input            | Hardware reset. This pin should be driven by a logic signal (0V and $\pm 3.3V$ ) with a capacitor between $\overline{RST}$ and DGND ( $C_{RST}$ ) or else an external RC circuit (capacitor between $\overline{RST}$ and DGND, resistor between $\overline{RST}$ and VDD33) should be used to apply a low signal for enough time to guarantee that all supplies are valid before the reset is de-asserted. The minimum $\overline{RST}$ pulse width is 100 $\mu$ s.                                                                                                                             |

| RCVN[1:8] | B3, E3, H3,<br>L3, N12,<br>K12, G12,<br>D12 | Output           | Receive signal output (Inverting). Voice and metering control voltage signals for SLIC amplifiers. This pin is not used by the MELT application.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RCVP[1:8] | C3, F3, J3,<br>M3, M12,<br>J12, F12,        | Output           | Receive signal output (Noninverting). Voice and metering control voltage signals for SLIC amplifiers.  This pin is not used by the MeLT application.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RSVD_O    | C12<br>L8                                   | Reserved         | Reserved. This pin is internally connected, let pin float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.015_0   | LU                                          | I VOSCI VEU      | 10001100. This pirils internally conflected, let pirilioat.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin Name         | Pin #                                       | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|---------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEL              | N8                                          | Output | Logic output that selects data outputs P0–P2 to either control the SLIC device operating modes or the SLIC device switch states.                                                                                                                                                                                                                                                                                                             |

| SHB, SLB,<br>SPB | J10, G10,<br>H10                            | Input  | Battery sense leads. Resistors that sense the high, low, and positive battery voltages connect here. If only one negative battery is used, connect both negative battery resistors to the same supply or leave SLB unconnected. If the positive battery is not used, connect the SPB resistor to AGND or leave the pin unconnected. These pins are current inputs into pins whose voltage is held at VREF, do not short these pins together. |

| SVA[1:8]         | C2, E2, J2,<br>N2, M13,<br>K13, F13,<br>B13 | Input  | Senses the voltages on A lead through external sense resistors.                                                                                                                                                                                                                                                                                                                                                                              |

| SVB[1:8]         | B2, D2, H2,<br>M2, N13,<br>L13, G13,<br>C13 | Input  | Senses the voltages on B lead through external sense resistors.                                                                                                                                                                                                                                                                                                                                                                              |

| TSCA, TSCB       | D7, A6                                      | Output | PCM highway backplane driver enables. TSCA or TSCB are active low when PCM data is output on the DXA or DXB pins, respectively. The outputs are open-drain and are normally inactive (high impedance). Pull-up loads should be connected to VDD33. If output not used, let the pin float. These pins are not used by the MeLT application.                                                                                                   |

| VAC[1:8]         | A1, G1, L1,<br>P2, P14,<br>H14, D14,<br>A13 | Input  | Voice (AC only) signal proportional to the IMT current of the SLIC. This pin is not used by the MeLT application.                                                                                                                                                                                                                                                                                                                            |

| VDD18_[1:4]      | P5, P10,<br>A10, B5                         | Supply | +1.8 VDC digital power supply inputs. Four decoupling capacitors should be used. Place a decoupling capacitor near VDD18_1, VDD18_2, VDD18_3, and VDD18_4. VDD18_4A does not                                                                                                                                                                                                                                                                 |

| VDD18_4A         | A5                                          |        | require its own decoupling capacitor. A bulk decoupling capacitor is also advised.                                                                                                                                                                                                                                                                                                                                                           |

| VDD33_[1:2]      | L7, E6                                      | Supply | +3.3 VDC digital power supply inputs. For best performance, all of the VDD33 and AVDD power supply pins should be connected together at the device. A decoupling capacitor should be used on each pin.                                                                                                                                                                                                                                       |

| VIMT[1:8]        | A2, F1, K1,<br>P1, P13,<br>J14, E14,<br>A14 | Input  | Signal proportional to the IMT current of the SLIC.                                                                                                                                                                                                                                                                                                                                                                                          |

| VREF[1:8]        | D3, G3, K3,<br>N3, L12,<br>H12, E12,<br>B12 | Output | This pin provides a +1.5 V, single-ended reference to the respective SLIC.                                                                                                                                                                                                                                                                                                                                                                   |

| XSB[1:8]         | D4, E4, K4,<br>L4, L11,<br>K11, E11,<br>D11 | Input  | External ringing sense pin. These pins sense the current through a resistor in order to measure the ringing voltage on the line.  This pin is not used by the MeLT application.                                                                                                                                                                                                                                                              |

| XSC              | F10                                         | Input  | External ring generator sense. This pin senses the current through a resistor in order to measure the ring generator voltage.  This pin is not used by the MeLT application.                                                                                                                                                                                                                                                                 |

# 5.0 Absolute Maximum Ratings

Stresses greater than those listed under *Absolute Maximum Ratings* can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods can affect device reliability.

| Storage Temperature                                 | -55°C ≤ T <sub>A</sub> ≤ +125°C                                       |

|-----------------------------------------------------|-----------------------------------------------------------------------|

| Ambient Temperature, under Bias                     | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$ |

| Ambient relative humidity (non condensing)          | 5% to 95%                                                             |

| VDD33 with respect to AGND or DGND                  | -0.4 V to +4.0 V                                                      |

| VDD18 with respect to AGND or DGND                  | -0.4 V to +1.98 V                                                     |

| AVDD with respect to AGND or DGND                   | −0.4 V to +4.0 V                                                      |

| AVDD with respect to VDD33                          | ±0.4 V                                                                |

| IMT, VIMT, VAC, IA, IB with respect to AGND or DGND | -0.4 V to (AVDD + 0.4 V)                                              |

| IO [1:8]_0 current                                  | 75 mA                                                                 |

| AGND                                                | DGND ±0.4 V                                                           |

| Latch up immunity (any pin)                         | ±100 mA                                                               |

| Any other pin with respect to DGND                  | -0.4 V to (VDD33 + 0.4 V)                                             |

| ESD Immunity (Human Body Model)                     | JESD22 Class 1C compliant                                             |

# 5.1 Green Package Assembly

The green package device is assembled with enhanced, environmental compatible lead-free, halogen-free, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes. Refer to IPC/JEDEC J-Std-020 for recommended peak soldering temperature and solder reflow temperature profile.

# 6.0 Operating Ranges

Microsemi guarantees the performance of this device over commercial (0° to 70°C) and industrial (–40° to 85°C) temperature ranges by conducting electrical characterization over each range and by conducting a production test with single insertion coupled to periodic sampling. These characterization and test procedures comply with the Telcordia GR-357-CORE Generic Requirements for Assuring the Reliability of Components Used in Telecommunications Equipment.

## **Environmental Ranges**

| Ambient Temperature       | -40 to +85°C |  |

|---------------------------|--------------|--|

| Ambient Relative Humidity | 15 to 85%    |  |

### **Electrical Ranges**

| Analog Supply AVDD   | +3.3 V ±5%, VDD33 ±50 mV |                                             |

|----------------------|--------------------------|---------------------------------------------|

| Digital Supply VDD33 | +3.3 V ±5%               | Refer to "Reset at Power-Up"                |

| Digital Supply VDD18 | +1.8 V ±5%               | on page 31 for supply and reset sequencing. |

| DGND                 | 0 V                      |                                             |

| AGND                 | DGND ±10 mV              |                                             |

# 7.0 Programming of the SLAC Parameters in the POTS Application

The line circuit parameters are stored in a Device Profile file. The Device Profile files are generated by Microsemi's application support programs WinSLAC and Profile Wizard. The Device Profile file is loaded into the ZL79258 SLAC through the API-II software interface.

The Device Profile file consists of a System-Device Profile and a number of optional parameter profiles. The following optional files pertain to parameters that are programmable in the SLAC:

#### **AC** parameters

- Input impedance Z<sub>D</sub>

- 2-4W Hybrid balance impedance Z<sub>L</sub>

- Test termination impedance Z<sub>T</sub>

- · Transmit Relative Level and frequency response equalization

- · Receive Relative Level and frequency response equalization

- A-law, μ-law, 16-bit linear, or wideband PCM encoding

#### DC parameters

- · Loop current limit value

- · Feed resistance before current limit

- · Metallic voltage at transition between current limit and resistive feed

- · Anti-saturation headroom voltage

- Common-mode offset applied to metallic DC feed voltage

- · Abrupt or smooth reversal

- · Off-hook detection threshold

- GND start threshold

- · DC fault detection threshold

- AC fault detection threshold

#### Ringing parameters

- A lead DC voltage V<sub>DCA</sub> during internal ringing

- B lead DC voltage V<sub>DCB</sub> during internal ringing

- Balanced or unbalanced internal ringing

- Amplitude of internal ringing

- Frequency of internal ringing

- Wave shape of internal ringing

- Enable external ringing

- Ring trip load resistance for external ringing

- Short loop ring trip threshold

- Long loop ring trip threshold

#### Tone and Metering signal parameters

- Frequency

- Amplitude

For a complete description of parameters, consult the WinSLAC Software User's Guide (Document ID 080779) and the Profile Wizard User's Guide (Document ID 127063).

### 8.0 Electrical Characteristics

# **AC/DC Specifications**

Typical values are for TA = 25°C and nominal supply voltage. Minimum and maximum values are over the temperature and supply voltage ranges as shown in "Operating Ranges" on page 20, except as noted. PCLK and FS are present and valid. DSP core power reduction enabled for Supply Power Dissipation specification.

Refer to the *Next Generation Carrier Chipset Hardware Design Guide (Document ID 126583)* for sensitive nodes that have trace capacitance restrictions.

| No. | Item                                                                                                    | Condition                                           | Min.        | Тур.                             | Max.        | Unit | Note |

|-----|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------|----------------------------------|-------------|------|------|

| 1   | Input Low Voltage (V <sub>IL</sub> )  Digital inputs and IO[1:8]_[0:1] programmed as an input           |                                                     | -0.30       | -                                | 0.80        |      | ,    |

| 2   | Input High Voltage (V <sub>IH</sub> ) Digital inputs and IO[1:8]_[0:1] programmed as an input           |                                                     | 2.0         | -                                | VDD33 + 0.3 | V    |      |

| 3   | Input Leakage Current, IO[1:8]_[0:1]  All other digital inputs                                          | 0 to VDD33<br>0 to VDD33                            | -10<br>-120 | 1                                | +10<br>+180 | μΑ   |      |

| 4   | Input hysteresis PCLK, FS, DRA, DRB, DCLK, DIN and IO[1:8]_[0:1] programmed as an input                 |                                                     | 0.15        | -                                | 0.30        | V    | 2    |

| 5   | Output Low Voltage (V <sub>OL</sub> )  DXA, DXB, DOUT, IO[1:8]_[0:1], INT, TSCA, TSCB                   | lol = 10 mA                                         | (-)         | _                                | 0.4         | V    |      |

|     | IO[1:8]_0 when programmed as relay driver                                                               | lol = 50 mA                                         |             |                                  | 0.7         |      |      |

|     | P[0:2], LD, SEL                                                                                         | IoI = 3 mA                                          | _           | _                                | 0.4         |      |      |

| 6   | Output High Voltage (V <sub>OH</sub> ) All digital outputs except INT in open drain mode and TSCA, TSCB | loh = 400 μA                                        | VDD33 – 0.4 | _                                | _           | V    |      |

| 7   | Input Leakage Current IMT                                                                               |                                                     | -1          | _                                | 1           | μΑ   |      |

|     | Full scale voltage levels, input or output DCA, DCB                                                     |                                                     |             | VREF±1.2<br>VREF±0.6<br>VREF±1.2 |             |      |      |

| _   | RCVP, RCVN                                                                                              | Normal gain<br>High gain                            |             |                                  |             |      |      |

| 8   | CANCEL                                                                                                  | Normal gain                                         | _           | VREF±0.6                         | _           | V    |      |

|     | CANCEL                                                                                                  | High gain                                           |             | VREF±1.2                         |             | V    |      |

|     | VIMT                                                                                                    |                                                     |             | See Note                         |             |      | 3    |

|     | VAC                                                                                                     |                                                     |             | See Note                         |             |      | 4    |

| 9   | Output voltage, VREF[1:8]                                                                               | Load current =<br>0 to 0.8 mA,<br>Source or<br>Sink | 1.47        | 1.50                             | 1.53        | ٧    |      |

| 10  | Battery read A/D relative error                                                                         | % of input voltage                                  | -3%         | _                                | +3%         |      | 2, 7 |

|     | Battery read A/D absolute error                                                                         |                                                     | -0.5        |                                  | +0.5        | V    |      |

|     | +3.3 V Supply Power Dissipation, per channel                                                            | Active state                                        | _           | 80                               | 125         |      |      |

| 11  | +1.8 V Supply Power Dissipation, per channel                                                            | . iouvo otato                                       | _           | 36                               | 65          | mW   | 8    |

|     | +3.3 V Supply Power Dissipation, per channel                                                            | Standby state                                       | _           | 42                               | 55          |      | J    |

|     | +1.8 V Supply Power Dissipation, per channel                                                            | 233.100, 31010                                      | _           | 25                               | 35          |      |      |

Table 2 - AC/DC Specifications

# 8.1 Transmission Specifications in the POTS Application

Transmission specifications are tested with the X-filter, R-filter, GX, and GR set to a gain of 1, the Z-filter, B-filter, AISN, and DISN set to a gain of 0, the VDAC gain set to 0 dB, the DRX gain set to 5/8, and the VAC gain set to 15. The receive path 0 dB output level is defined as 0.18472 Vrms per pin on RCVP-RCVN (0.36944 Vrms differential) and the transmit path 0 dB input level is defined as 0.032839 Vrms on the VAC pin. Supplies are as specified in "Operating Ranges" on page 20 and PCLK and FS are present and valid.

| No. | Item                                                     | Condition                                                                         | Min         | Тур | Max         | Unit    | Note |

|-----|----------------------------------------------------------|-----------------------------------------------------------------------------------|-------------|-----|-------------|---------|------|

| 1   | Insertion Loss<br>A-D, D-A                               | Input: 1014Hz, 0 dBm0<br>GR = GX = 0 dB; AISN, R, X, B and Z<br>disabled          | -0.25       | 0   | +0.25       |         |      |

| ·   | A-D + D-A                                                | Temperature = 25°C                                                                | -0.15       | 0   | +0.15       |         |      |

|     | A-D + D-A                                                | Variation over temperature                                                        | -0.1        | 0   | +0.1        | dB      | 7    |

| 2   | Level set error (Error between setting and actual value) | A-D, D-A                                                                          | -0.1        | 0   | 0.1         |         |      |

| 3   | DR to DX gain in full digital loopback mode              | DR Input: 1014 Hz, -10 dBm0<br>GR=GX=0 dB; AISN, R, X, B and Z<br>filters default | -0.3        | 0   | +0.3        |         |      |

|     | Idle Channel Noise,                                      | A-D (DX output)                                                                   | -           | _   | -69         | dBm0p   |      |

|     | Psophometric Weighted (A-law)                            | D-A (RCVN, RCVP output)                                                           | 7           | _   | -78         | автор   | 5    |

| 4   | C Message weighted (μ-law)                               | A-D (DX output)                                                                   | <i>&gt;</i> | _   | +19         | dBrnC0  |      |

| 4   | C Message weighted (µ-law)                               | D-A (RCVN, RCVP output)                                                           | _           | _   | +12         | ubilico |      |

|     | 15 kHz flat (Wideband linear mode)                       | A-A (VAC input any channel, RCVN, RCVP output any other channel, DX tied to DR)   | _           | 16  | _           | dBrn0   | 1    |

| 5   | PSRR Image frequency (VDDxx)<br>A-D                      | Input: 4.8 to 7.8 kHz,<br>200 mVp-p                                               | 37          | _   | _           | dB      | 1    |

| J   | D-A                                                      | Measure at:<br>8000 Hz – Input frequency                                          | 37          | _   | _           | QD      | '    |

| 6   | End-to-end absolute group delay                          | 1014Hz; –10dBm0                                                                   |             | _   | 725         | μS      | 2, 6 |

| Ü   | End to one absolute group delay                          | B = Z = 0; X = R = 1                                                              |             |     | 720         |         |      |

| 7   | Crosstalk TX to RX                                       | 0 dBm0 300 Hz to 3400 Hz                                                          | _           | _   | <b>–</b> 75 |         |      |

| •   | same channel RX to TX                                    | 333112 (0 0700112                                                                 | _           | _   | <b>–</b> 75 | dBm0    | 1    |

| 8   | Crosstalk TX or RX to TX                                 | 0 dBm0 1014 Hz                                                                    | _           | _   | <b>–</b> 75 | UDIII0  | '    |

| J   | other channel TX or RX to RX                             |                                                                                   | _           | _   | <b>-</b> 75 |         |      |

**Table 3 - Transmission Specifications**

#### Notes:

- 1. Not tested or partially tested in production. This parameter is guaranteed by characterization or correlation to other tests.

- 2. Guaranteed by design.

- 3. VIMT has an analog range of VREF ±1.2 V, although only VREF ±1.0 V is used by the A/D input.