## Features

- Up to 1.6M Used Gates and 596 Pads with 3.3V, 3V and 2.5V Libraries

- High Speed 170 ps Gate Delay 2 Input NAND, FO = 2 (nominal)

- System Level Integration Technology Cores on Request

- Memories: SRAM and TPRAM, Gate Level or Embedded, with EDAC

- I/O Interfaces:

- 5V Tolerant/Compliant (S) or 3V (R) Matrix Options

- CMOS, LVTTL, LVDS, PCI, USB, etc.

- Output Currents Programmable from 2 to 24 mA, by Step of 2 mA

- Cold Sparing Buffers (2 µA Max. Leakage Current at 3.6V Worst Case Mil Temp.)

- 250 MHz PLL (on request), 220 MHz LVDS and 800 MHz Max. Toggle Frequency at 3.3V

- Deep Submicron CAD Flow

- ESD better than 2000V

- No Single Event Latch-Up below an LET Threshold of 80 MeV/mg/cm<sup>2</sup>

- SEU Hardened Flip-flops

- Tested Up to a Total Dose of 300 Krad (Si) according to Mil STD 883 Method 1019

- Quality Grades

- QML Q and V with SMD 5962-01B01 and 5962-08B01

- ESCC QML with ESCC 9202 / 076

## Description

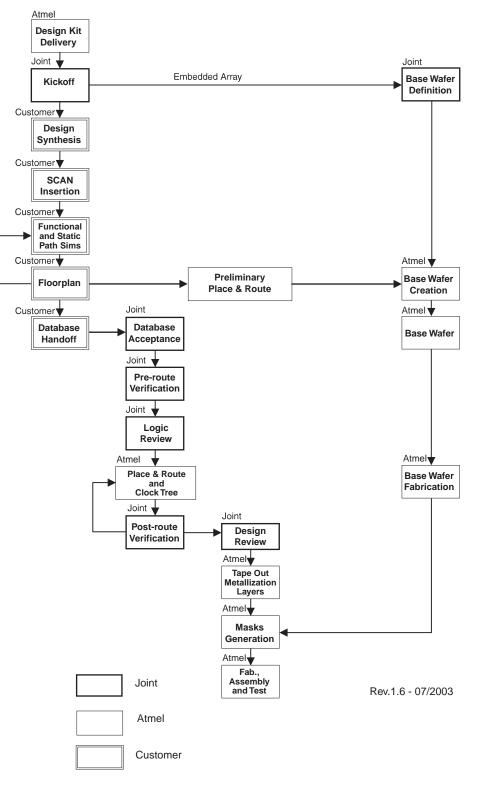

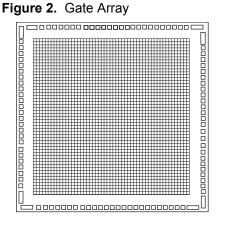

The MH1RT Gate Array and Embedded Array families from Atmel are fabricated on a radiation hardened 0.35 micron CMOS process, with up to 4 levels of metal for interconnect. This family features arrays with up to 1.6 million routable gates and 596 pads. The high density and high pin count capabilities of the MH1RT family, coupled with the ability to embed cores or memories on the same silicon, make the MH1RT series of arrays one of the best choices for System Level Integration.

The MH1RT series is supported by an advanced software environment based on industry standards linking proprietary and commercial tools. Verilog<sup>®</sup>, DFT<sup>®</sup>, Synopsys<sup>®</sup> and Vital are the reference front end tools. The Cadence<sup>®</sup> 'Logic Design Planner' floor planning associated with timing driven layout provides an efficient back end cycle.

The MH1RT series comes as a dual use of the MH1 series, adding:

- through process changes, the latch-up susceptibility better than 80 MeV/mg/cm<sup>2</sup> and the 300 Krad (Si) radiation level as required by most space programs.

- through cells relayout, an SEU built-in protection allowing to SEU harden only where it is necessary with respect to function requirements

With a background of 15 years experience, the MH1RT series comes as the Atmel 7th generation of ASIC series designed for radiation hardened applications.

Rad Hard 1.6M Used Gates 0.35 µm CMOS Sea of Gates/ Embedded Array

## MH1RT

#### Table 1. List of Available MH1RT Matrices

| Device<br>Number | Typical Routable<br>Gates | Max Pad<br>Count | Max<br>I/O Count | Gate<br>Speed <sup>(1)</sup> | Max. Sites Count |

|------------------|---------------------------|------------------|------------------|------------------------------|------------------|

| MH1099E          | 519,000                   | 332              | 324              | 180 ps                       | 920,385          |

| MH1156E          | 764,000                   | 412              | 404              | 180 ps                       | 1,447,975        |

| MH1242E          | 1,198,000                 | 512              | 504              | 180 ps                       | 2,275,377        |

| MH1332E          | 1,634,000                 | 596              | 588              | 180 ps                       | 3,098,804        |

Notes: 1. Nominal 2 Input NAND Gate FO = 2 at 3.3V.

## Design

Design SystemsAtmel supports several major software systems for design with complete macro cell libraries, as<br/>well as utilities for checking the netlist and estimated pre-route delay simulations.

The following design systems are supported:

#### Table 2. Supported design systems

| System                | Available Tools                                                                                                                                                       |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cadence               | NCsim <sup>®</sup> - Verilog Simulator<br>Encounter <sup>™</sup> - Floorplanner<br>RTL compiler <sup>®</sup> - Synthesis (Ambit)                                      |

| Mentor/Model Tech     | Questasim/Modelsim Verilog and VHDL (VITAL) Simulator<br>DFT - Scan insertion and ATPG, BIST                                                                          |

| Synopsys <sup>®</sup> | Design Compiler <sup>™</sup> - Synthesis<br>Primetime <sup>®</sup> - Static Path<br>Formality <sup>®</sup> - Equivalence Checking<br>DFTmax - Scan insertion and ATPG |

## Design Flow and Tools

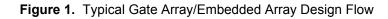

Atmel's design flow for Gate Array/Embedded Array is structured to allow the designer to consolidate the greatest number of system components possible onto the same silicon chip, using available third party design tools. Atmel's cell library reflects silicon performance over extremes of temperature, voltage, and process, and includes the effects of metal loading, inter-level capacitance, and edge rise and fall times. The Design Flow includes clock tree synthesis to minimize skew and latency. RC extraction is performed on final design database and incorporated into the timing analysis.

The Typical Gate Array/Embedded Array Design Flow, shown on page 4, provides a pictorial description of the typical interaction between Atmel's Gate Array/Embedded Array design staff and the customer. Atmel will deliver design kits to support the customer's synthesis, verification, floorplanning, and SCAN insertion activities. Tools such as Synopsys Synthesis, Cadence and Mentor Logic Simulators are used, and many others are available. Should a design include embedded memory or an embedded core, Atmel needs to understand the partition of the Array, and define the location of the memory blocks and/or cores (preliminary place and route) so that an underlayer layout model can be created (Base Wafer).

Following the Logic Review, the design is routed, and post-route RC data is extracted. Following post-route verification and the Design Review, the design is taped out for fabrication.

The purpose of these reviews is to check the conformity of the design to Atmel rules, and acknowledge it in formal documents.

4

# MH1RT

## Pin Definition Requirements

The corner pads are reserved for Power and Ground only. All other pads are fully programmable as Input, Output, Bidirectional, Power or Ground. When implementing a design with 5V compliant buffers, one buffer site must be reserved for the  $V_{DD5}$  pin, which is used to distribute power to the buffers.

Figure 3. Embedded Array

- **I/O Site: Pad and Sub-Sections** The I/O sites can be configured as input, output, 3-state output and bidirectional buffers, each with pullup or pulldown capability, if required, by utilizing their corresponding sub-section. Bidirectionnal buffers are the result of an input and output buffers placed in adjacent sub-sections in the same I/O site. Special buffers may require multiple I/O sites. Oscillators require 2 I/O sites, each power and ground pin utilizes one I/O site.

- PCI Buffers PCI compatible input and output buffers are available for each bias voltage, 3V and 5V.

LVDS Buffers Each LVDS buffer uses 2 I/O sites.

LVDS drivers are specific for each bias voltage and require one external current bias resistor per chip; LVDS receiver is the same for all bias voltages and requires 1 external line matching 100  $_\Omega$  resistor per receiver.

**Cold Sparing** It is the use of twice the same chip, A1 and A2, A1 ON and A2 OFF, with all signal pins/pads connected by pairs, A111 with A211, A101 with A201,...

During this mode operation:

- the chip OFF must survive and operate when turned ON without functional, AC, DC or reliability impact,

- the current pulled by the OFF chip must be limited to a low value: Atmel specification for their dedicated cold sparing buffers is 2 μA worst case by signal pins/pads.

For any other operation mode, refer to maximum ratings.

**Memory Blocks** Memory blocks can be either synthesized on gates (when smaller than 8 bits) or compiled and embedded in the array itself. Various combinations of Through Flow or Bus Watch EDACs, 4, 8, 16 and 32 bit wide, can be used to alleviate the effect of SEU induced errors.

# MH1RT

6

# MH1RT

#### ASIC Design Translation Atmel has successfully translated existing designs from most major ASIC vendors (LSI Logic<sup>®</sup>, Motorola<sup>®</sup>, SMOS<sup>®</sup>, Oki<sup>®</sup>, NEC<sup>®</sup>, Fujitsu<sup>®</sup>, AMI<sup>®</sup> and others) into the gate arrays. These designs have been optimized for speed and gate count and modified to add logic or memory, or replicated for a pin-to-pin compatible, drop-in replacement.

**Design Entry** Design entry is performed by the customer using an Atmel ASIC library. A complete netlist and vector set must then be provided to Atmel. Upon acceptance of this data set, Atmel continues with the standard design flow.

#### **FPGA and PLD Conversions** Atmel has successfully translated existing FPGA/PLD designs from most major vendors (Xilinx<sup>®</sup>, Actel<sup>®</sup>, Altera<sup>®</sup>, AMD<sup>®</sup> and Atmel) into the gate arrays. There are four primary reasons to convert from an FPGA/PLD to a gate array. Conversion of high volume devices for a single or combined design is cost effective. Performance can often be optimized for speed or low power consumption. Several FPGA/PLDs can be combined onto a single chip to minimize cost while reducing on-board space requirements. Finally, in situations where an FPGA/PLD was used for fast cycle time prototyping, a gate array may provide a lower cost answer for long-term volume production.

# **Cell Library** Atmel's MH1RT Series gate arrays make use of an extensive library of macro cell structures, including logic cells, buffers and inverters, multiplexers, decoders, and I/O options. Soft macros are also available.

The MH1RT Series PLL operates at frequencies of up to 250 MHz with minimal phase error and jitter, making it ideal for frequency synthesis of high speed on-chip clocks and chip to chip synchronization.

These cells are well characterized by use of SPICE modeling at the transistor level, with performance verified on manufactured test arrays. Characterization is performed over the rated temperature and voltage ranges to ensure that the simulation accurately predicts the performance of the finished product.

| Cells                                                            | Number of Cells |

|------------------------------------------------------------------|-----------------|

| Logic Cells                                                      | 95              |

| I/O Buffers<br>3V or 2.5V or 3.3V<br>5V Tolerant<br>5V Compliant | 110<br>36<br>70 |

| Specific Cells<br>LVDS, PCI                                      | 11              |

| SEU Hardened Cells                                               | 9               |

| Cold Sparing                                                     | 63              |

## **Electrical Characteristics**

## **Absolute Maximum Ratings**

| Operating Ambient Temperature55°C to +125°C    | *NOTE: |

|------------------------------------------------|--------|

| Storage Temperature65°C to +150°C              |        |

| Maximum Input Voltage VDD +0.5V and VCC + 0.5V |        |

| Maximum 3.3V Operating Voltage 4V (VDD)        |        |

| Maximum 5V Operating Voltage 6V (VCC)          |        |

| ESD level                                      |        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **DC Characteristics**

Applicable over recommended operating temperature and voltage range unless otherwise noted.

| Symbol                           | Parameter                                                                                    | Buffer        | Test Condition                                            | Min.           | Тур  | Max.          | Units |

|----------------------------------|----------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------|----------------|------|---------------|-------|

| T <sub>A</sub>                   | Operating Temperature                                                                        | All           |                                                           | -55            | 25   | 125           | С     |

| V <sub>DD</sub>                  | Supply Voltage                                                                               | All           |                                                           | 2.3            | 2.5  | 2.7           | V     |

| IIL                              | Low-level Input Current<br>Pull-up resistors PRU1 <sup>(1)</sup><br>Pull down resistor PRD1  | CMOS          | V <sub>IN</sub> = V <sub>SS</sub>                         | -1<br>70<br>-5 |      | 1<br>230<br>5 | μA    |

| I <sub>IH</sub>                  | High level Input Current<br>Pull-up resistors PRU1<br>Pull down resistor PRD1 <sup>(2)</sup> | CMOS          | V <sub>IN</sub> = V <sub>DD (Max.)</sub>                  | -1<br>-5<br>70 |      | 1<br>5<br>540 | μA    |

| I <sub>OZ</sub>                  | High impedance state<br>output current                                                       | All           | Vin = Vdd or Vss, Vdd = Vdd<br>(Max.)<br>No pull resistor | -1             | _    | 1             | μA    |

|                                  |                                                                                              | CMOS          |                                                           |                |      | 0.3Vdd        |       |

|                                  |                                                                                              | PCI           |                                                           |                |      | 0.325Vdd      | V     |

| V <sub>IL</sub>                  | Low level Input voltage                                                                      | Schmitt level |                                                           | 0.78           |      | 1.25          |       |

|                                  |                                                                                              | CMOS          |                                                           | 0.7 Vdd        |      |               |       |

|                                  |                                                                                              | PCI           |                                                           | 0.475Vdd       |      |               | V     |

| V <sub>IH</sub>                  | High level Input voltage                                                                     | Schmitt level |                                                           | 1.06           |      | 1.61          |       |

| Delta V                          | CMOS Hysterisis                                                                              |               |                                                           | 0.25           | 0.34 |               | V     |

| I <sub>ICS</sub>                 | Cold sparing leakage input current                                                           | PICZ          | Vin = 0 to VDDmax                                         | -2             |      | 2             | μA    |

| I <sub>ocs</sub>                 | Cold sparing leakage output current                                                          | POxxZ         | Vout = 0 to VDDmax                                        | -2             |      | 2             | μA    |

| V <sub>CSTH</sub> <sup>(3)</sup> | Supply threshold of cold sparing buffers                                                     | POxxZ         | locs = 100 μA                                             |                | 0.5  |               | V     |

# MH1RT

8

#### Table 3. 2.5V DC Characteristics (Continued)

| Symbol              | Parameter                                    | Buffer       | Test Condition                                | Min. | Тур  | Max.    | Units  |

|---------------------|----------------------------------------------|--------------|-----------------------------------------------|------|------|---------|--------|

| V <sub>OL</sub>     | Low-level Output Voltage (4)                 | PO11         | I <sub>OL</sub> = 0.8 mA, Vdd = Vdd (Min.)    |      |      | 0.4     | V      |

| V <sub>OH</sub>     | High level output voltage <sup>(5)</sup>     | PO11         | loh = -0.6 mA, Vdd = Vdd (Min.)               | 2    |      |         | V      |

| I <sub>OS (6)</sub> | Output short circuit current<br>losn<br>losp | PO11<br>PO11 | Vdd = Vdd (Max.),<br>Vout = Vdd<br>Vouy = Vss |      |      | 15<br>8 | mA     |

| I <sub>CCSB</sub>   | Leakage current per cell                     |              | Vdd = Vdd (Max.)                              |      | 0.27 | 4       | nA     |

| I <sub>CCOP</sub>   | Dynamic current per gate                     |              | Vdd = Vdd (Max.)                              |      |      | 0.32    | µW/MHz |

1. For standard pull-ups: PRU (#), # = {1-31} index for Ron: Ron = # x RO where RO =  $19 \text{ k}\Omega \text{ typ}$ ,  $30 \text{ k}\Omega \text{ Max.}$ ,  $12 \text{ k}\Omega \text{ Min.}$

2. For standard pull-downs: PRD (#), # = {1-31} index for Ron: Ron = # x RO where RO =  $11 \text{ k}\Omega \text{ typ}$ ,  $30 \text{ k}\Omega \text{ Max.}$ ,  $5 \text{ k}\Omega \text{ Min.}$

3. Guaranteed not tested

4. For output buffers PO (1-C) (1-C):

1-C: hex value: convert hex to decimal x IO = p and n-channel output drive

IO = 1.6 mA for standard buffers (including cold sparing) measured at Vol = 0.4V

5. For output buffers PO (1-C) (1-C):

1-C: hex value: convert hex to decimal x IO = p and n-channel output drive

IO = -1.6 mA for standard buffers (including cold sparing) measured at Voh = 2.0V

6. Supplied as a design limit but not guaranteed or tested. No more than one output may be shorted at a time for a maximum duration of 10 seconds.

#### Table 4. 3V DC Characteristics

| Symbol          | Parameter                                                        | Buffer        | Test Condition                                            | Min.                 | Тур  | Max.                 | Units |

|-----------------|------------------------------------------------------------------|---------------|-----------------------------------------------------------|----------------------|------|----------------------|-------|

| T <sub>A</sub>  | Operating Temperature                                            | All           |                                                           | -55                  | 25   | 125                  | С     |

| V <sub>DD</sub> | Supply Voltage                                                   | All           |                                                           | 2.7                  | 3.0  | 3.3                  | V     |

|                 | Low-level Input Current                                          |               |                                                           | -1<br>108            |      | 1<br>330             |       |

| I <sub>IL</sub> | Pull-up resistors PRU1 <sup>(1)</sup><br>Pull down resistor PRD1 | CMOS          | V <sub>IN</sub> = V <sub>SS</sub>                         | -5                   |      | 5                    | μA    |

|                 | High level Input Current<br>Pull-up resistors PRU1               |               |                                                           | -1<br>-5             |      | 1<br>5               | μA    |

| I <sub>IH</sub> | Pull down resistor PRD1 <sup>(2)</sup>                           | CMOS          | $V_{IN} = V_{DD(Max.)}$                                   | 108                  |      | 825                  |       |

| I <sub>OZ</sub> | High impedance state<br>output current                           | All           | VIN = VDD OR VSS, VDD =<br>VDD (Max.)<br>No pull resistor | -1                   |      | 1                    | μA    |

| -               |                                                                  | CMOS          |                                                           |                      |      | 0.8                  |       |

| V <sub>IL</sub> |                                                                  | PCI           |                                                           |                      |      | 0.325V <sub>DD</sub> | V     |

|                 | Low level Input voltage                                          | Schmitt level |                                                           | 0.90                 |      | 1.42                 |       |

|                 |                                                                  | CMOS          |                                                           | 2                    |      |                      |       |

|                 |                                                                  | PCI           |                                                           | 0.475V <sub>DD</sub> |      |                      | V     |

| V <sub>IH</sub> | High level Input voltage                                         | Schmitt level |                                                           | 1.25                 |      | 1.93                 |       |

| Delta V         | CMOS Hysterisis                                                  |               |                                                           | 0.31                 | 0.42 |                      | V     |

#### Table 4. 3V DC Characteristics (Continued)

| Symbol                           | Parameter                                    | Buffer       | Test Condition                               | Min. | Тур | Max.     | Units  |

|----------------------------------|----------------------------------------------|--------------|----------------------------------------------|------|-----|----------|--------|

| I <sub>ICS</sub>                 | Cold sparing leakage input current           | PICZ         | VIN = 0 to VDDmax                            | -2   | _   | -2       | μA     |

| I <sub>ocs</sub>                 | Cold sparing leakage<br>output current       | POxxZ        | Vout = 0 to VDDmax                           | -2   | _   | -2       | μA     |

| V <sub>CSTH</sub> <sup>(3)</sup> | Supply threshold of cold sparing buffers     | POxxZ        | locs = 100 µA                                | _    | 0.5 | _        | V      |

| V <sub>OL</sub>                  | Low-level Output Voltage                     | PO11         | I <sub>OL</sub> = 1 mA, Vdd = Vdd(Min.)      | -    | -   | 0.4      | V      |

| V <sub>OH</sub>                  | High level output voltage <sup>(5)</sup>     | PO11         | loh = -0.8 mA, Vdd = Vdd(Min.)               | 2.4  | -   | -        | V      |

| I <sub>OS (6)</sub>              | Output short circuit current<br>losn<br>losp | PO11<br>PO11 | Vdd = Vdd(Max.),<br>Vout = Vdd<br>Vouy = Vss | -    | _   | 21<br>12 | mA     |

| I <sub>CCSB</sub>                | Leakage current per cell                     | -            | Vdd = Vdd(Max.)                              | -    | 0.6 | 5        | nA     |

| I <sub>CCOP</sub>                | Dynamic current per gate                     | -            | Vdd = Vdd(Max.)                              | -    | -   | 0.54     | µW/MHz |

1. For standard pull-ups: PRU (#), # = {1-31} index for Ron: Ron = # x RO where RO =  $15 k\Omega typ$ ,  $25 k\Omega Max$ .,  $10 k\Omega Min$ .

2. For standard pull-downs: PRD (#),  $# = \{1-31\}$  index for Ron: Ron = # x RO where RO =  $9 \text{ k}\Omega \text{ typ}$ , 25 k $\Omega \text{ Max.}$ , 4 k $\Omega \text{ Min.}$

3. Guaranteed not tested.

4. For output buffers PO (1-C) (1-C):

1-C: hex value: convert hex to decimal x IO = p and n-channel output drive

IO = -1.8 mA for standard buffers (including cold sparing) measured at Vol = 0.4V

5. For output buffers PO (1-C) (1-C):1-C:

hex value: convert hex to decimal x IO = p and n-channel output drive

IO = -1.8 mA for standard buffers (including cold sparing) measured at Voh = 2.4V

6. Supplied as a design limit but not guaranteed or tested. No more than one output may be shorted at a time for a maximum duration of 10 seconds.

| Symbol          | Parameter                                                                                    | Buffer        | Test Condition                                           | Min.            | Тур | Max.          | Units |

|-----------------|----------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------|-----------------|-----|---------------|-------|

| T <sub>A</sub>  | Operating Temperature                                                                        | All           |                                                          | -55             | 25  | 125           | С     |

| V <sub>DD</sub> | Supply Voltage                                                                               | All           |                                                          | 3               | 3.3 | 3.6           | V     |

| I               | Low-level Input Current<br>Pull-up resistors PRU1 <sup>(1)</sup><br>Pull down resistor PRD1  | CMOS          | V <sub>IN</sub> = V <sub>SS</sub>                        | -1<br>120<br>-5 |     | 1<br>400<br>5 | μΑ    |

| I <sub>IH</sub> | High level Input Current<br>Pull-up resistors PRU1<br>Pull down resistor PRD1 <sup>(2)</sup> | CMOS          | V <sub>IN</sub> = V <sub>DD(Max.)</sub>                  | -1<br>-5<br>150 |     | 1<br>5<br>900 | μΑ    |

| loz             | High impedance state<br>output current                                                       | All           | Vin = Vdd or Vss, Vdd =<br>Vdd(Max.)<br>No pull resistor | -1              |     | 1             | μA    |

|                 |                                                                                              | CMOS          |                                                          |                 |     | 0.8           |       |

|                 |                                                                                              | PCI           |                                                          |                 |     | 0.325Vdd      | V     |

| V <sub>IL</sub> | Low level Input voltage                                                                      | Schmitt level |                                                          | 0.99            |     | 1.51          |       |

Table 5.

3.3V DC Characteristics

Table 5. 3.3V DC Characteristics (Continued)

| Symbol                           | Parameter                                | Buffer        | Test Condition                          | Min.     | Тур  | Max. | Units  |

|----------------------------------|------------------------------------------|---------------|-----------------------------------------|----------|------|------|--------|

|                                  |                                          | CMOS          |                                         | 2        |      |      |        |

|                                  |                                          | PCI           |                                         | 0.475Vdd |      |      | V      |

| V <sub>IH</sub>                  | High level Input voltage                 | Schmitt level |                                         | 1.40     |      | 2.08 |        |

| Delta V                          | CMOS Hysterisis                          |               |                                         | 0.37     | 0.48 |      | V      |

| I <sub>ICS</sub>                 | Cold sparing leakage input current       | PICZ          | Vdd = Vss = 0V<br>Vin = 0 to VDD Max    | -2       |      | -2   | μΑ     |

| I <sub>ocs</sub>                 | Cold sparing leakage output current      | POxxZ         | Vdd = Vss = 0V<br>Vin = 0 to VDD Max    | -2       |      | -2   | μΑ     |

| V <sub>CSTH</sub> <sup>(3)</sup> | Supply threshold of cold sparing buffers | POxxZ         | locs = 100 μA                           |          | 0.5  |      | V      |

| V <sub>OL</sub>                  | Low-level Output Voltage                 | PO11          | I <sub>OL</sub> = 2 mA, Vdd = Vdd(Min.) |          |      | 0.4  | V      |

| V <sub>OH</sub>                  | High level output voltage <sup>(5)</sup> | PO11          | loh = -1.8 mA, Vdd = Vdd(Min.)          | 2.4      |      |      | V      |

|                                  | Output short circuit current losn        | PO11          | Vdd = Vdd(Max.),<br>Vout = Vdd          |          |      | 23   | mA     |

| I <sub>OS (6)</sub>              | losp                                     | PO11          | Vouy = Vss                              |          |      | 13   |        |

| I <sub>CCSB</sub>                | Leakage current per cell                 |               | Vdd = Vdd(Max.)                         |          | 0.7  | 5    | nA     |

| I <sub>CCOP</sub>                | Dynamic current per gate                 |               | Vdd = Vdd(Max.)                         |          |      | 0.69 | µW/MHz |

1. For standard pull-ups: PRU(#), # = {1-31} index for Ron: Ron = # x RO where RO = 14 k $\Omega$  typ, 25 k $\Omega$  Max., 9 k $\Omega$  Min.

2. For standard pull-downs:PRD(#), # = {1-31} index for Ron: Ron = # x RO where RO =  $8k\Omega \text{ typ}$ , 20  $k\Omega \text{ Max.}$ , 4  $k\Omega \text{ Min.}$

3. Guaranteed not tested.

5.

4. For output buffers PO (1-C) (1-C):

1-C: hex value: convert hex to  $k\Omega \times IO = p$  and n-channel output drive

IO = -2.0 mA for standard buffers (including cold sparing) measured at Vol = 0.4V

For output buffers PO (1-C) (1-C):

1-C: hex value: convert hex to  $k\Omega \times IO = p$  and n-channel output drive

IO = -2.0 mA for standard buffers (including cold sparing) measured at Voh = 2.4V

6. Supplied as a design limit but not guaranteed or tested. No more than one output may be shorted at a time for a maximum duration of 10 seconds.

#### Table 6.5V DC Characteristics

| Symbol          | Parameter                                                                                   | Buffer       | Test Condition                    | Min.            | Тур | Max.          | Units |

|-----------------|---------------------------------------------------------------------------------------------|--------------|-----------------------------------|-----------------|-----|---------------|-------|

| T <sub>A</sub>  | Operating Temperature                                                                       | All          |                                   | -55             | 25  | 125           | С     |

| V <sub>dd</sub> | Supply Voltage                                                                              | 5V Tolerant  |                                   | 3.0             | 3.3 | 3.6           | V     |

| V <sub>cc</sub> | Supply Voltage                                                                              | 5V Compliant |                                   | 4.5             | 5   | 5.5           | V     |

| I <sub>IL</sub> | Low-level Input Current<br>Pull-up resistors PRU1 <sup>(1)</sup><br>Pull down resistor PRD1 | CMOS         | V <sub>IN</sub> = V <sub>SS</sub> | -1<br>180<br>-5 |     | 1<br>690<br>5 | μA    |

#### Table 6. 5V DC Characteristics (Continued)

| Symbol                           | Parameter                                | Buffer        | Test Condition              | Min.     | Тур  | Max.     | Units    |

|----------------------------------|------------------------------------------|---------------|-----------------------------|----------|------|----------|----------|

|                                  | High level Input Current                 |               |                             | -1       |      | 1        |          |

|                                  | Pull-up resistors PRU1                   |               |                             | -5       |      | 5        | μA       |

| I <sub>IH</sub>                  | Pull down resistor PRD1 <sup>(2)</sup>   | CMOS          | $V_{IN} = V_{DD(Max.)}$     | 30       |      | 400      |          |

|                                  | High impedance state                     |               | Vin = Vdd orVss,Vdd=Vdd(max | -1       |      | 1        |          |

| loz                              | output current                           | All           | No pull resistor            | -1       |      | I        | μA       |

|                                  |                                          | PICV, PICV5   |                             |          |      | 0.8      |          |

|                                  |                                          | PCI           |                             |          |      | 0.325Vdd | V        |

| Vil                              | Low level Input voltage                  | Schmitt level |                             | 0.99     |      | 1.51     |          |

|                                  |                                          | PICV, PICV5   |                             | 2        |      |          |          |

|                                  |                                          | PCI           |                             | 0.475Vdd |      |          | V        |

| V <sub>IH</sub>                  | High level Input voltage                 | Schmitt level |                             | 1.40     |      | 2.08     |          |

| Delta V                          | CMOS Hysterisis                          |               |                             | 0.37     | 0.48 |          | V        |

|                                  | Cold sparing leakage input               |               |                             | -2       |      | -2       | μA       |

| IICS                             | current                                  | PICZ          | Vin = 0 to VDDmax           | _        |      | _        | <b>P</b> |

| 1                                | Cold sparing leakage                     | POxxZ         |                             | -2       |      | -2       | μA       |

| l <sub>ocs</sub>                 | output current                           | PUXXZ         | Vout = 0 to VDDmax          |          |      |          |          |

| V <sub>CSTH</sub> <sup>(3)</sup> | Supply threshold of cold sparing buffers | POxxZ         | locs = 100 μA               |          | 0.6  |          | V        |

|                                  | Low Voltage/2.5V range                   | PO11V         | lol = 0.5 mA                |          |      |          |          |

|                                  | Low Voltage/3.0V range                   | PO11V         | lol = 0.6 mA                |          |      |          |          |

|                                  | Low Voltage/3.3V range                   | PO11V         | lol = 1.2 mA                |          |      | 0.4      | V        |

|                                  | Low Voltage/2.5V range                   | PO11V5        | lol = 1.1 mA                |          |      | 0.4      | v        |

|                                  | Low Voltage/3.0V range                   | PO11V5        | lol = 1.3 mA                |          |      |          |          |

| V <sub>OL</sub> <sup>(4)</sup>   | Low Voltage/3.3V range                   | PO11V5        | lol = 1.5 mA                |          |      |          |          |

|                                  | Low Voltage/2.5V range                   | PO11V         | loh = 0.5 mA                | 2        |      |          |          |

|                                  | Low Voltage/3.0V range                   | PO11V         | loh = 0.6 mA                | 2.4      |      |          |          |

|                                  | Low Voltage/3.3V range                   | PO11V         | loh = 1.2 mA                | 2.4      |      |          | V        |

|                                  | Low Voltage/2.5V range                   | PO11V5        | loh = 1.1 mA                | 2.4      |      |          | v        |

|                                  | Low Voltage/3.0V range                   | PO11V5        | loh = 1.3 mA                | 2.4      |      |          |          |

| V <sub>OH</sub> <sup>(5)</sup>   | Low Voltage/3.3V range                   | PO11V5        | loh = 1.5 mA                | 2.4      |      |          |          |

|                                  | Output short circuit current             |               | Vdd = Vdd(Max.),            |          |      |          |          |

|                                  | losn                                     | PO11V         | Vout = Vdd                  |          |      | 28       | mA       |

| I <sub>OS (6)</sub>              | losp                                     | PO11V         | Vouy = Vss                  |          |      | 17       |          |

1. For 5V tolerant/compliant pull-ups: PRU(#), # = {1-31} index for Ron: Ron = # x RO where RO = 14 kΩ typ, 25 kΩ Max., 8 kΩ Min.

2. For 5V tolerant/compliant pull-downs: PRD(#), # = {1-31} index for Ron: Ron = # x RO where:

RO =  $19 \text{ k}\Omega \text{ typ}$ ,  $45 \text{ k}\Omega \text{ Max.}$ ,  $9 \text{ k}\Omega \text{ Min.}$  in 3.3 V range,

RO = 23 k $\Omega$  typ, 55 k $\Omega$  Max., 11 k $\Omega$  Min. in 3V range,

$RO = 36 k\Omega typ$ ,  $80 k\Omega Max.$ ,  $17 k\Omega Min.$  in 2.5V range,

3. Guaranteed not tested.

12 MH1RT

4. Tolerant Buffers (including cold spearing):

IO = -1.0, 1.3, 1.4 mA measured at VOL = 0.4, 0.4, 0.4V in 2.5, 3.0, 3.3V range respectively.

Compliant Buffers (VCC = 4.5V)

IO = -1.1, 1.4, 1.6 mA measured at VOL = 0.4, 0.4, 0.4 V in 2.5, 3.0, 3.3V range respectively.

Tolerant Buffers (including cold spearing):

IO = -1.0, -1.3, -1.4 mA measured at VOH = 2.0, 2.4, 2.4V in 2.5, 3.0, 3.3V range respectively. Compliant Buffers (VCC = 4.5V)

IO = -1.1, -1.4, -1.6 mA measured at VOH = 2.0, 2.4, 2.4 V in 2.5, 3.0, 3.3V range respectively.

6. Supplied as a design limit but not guaranteed or tested. No more than one output may be shorted at a time for a maximum duration of 10 seconds.

#### LVDS Driver DC and AC Characteristics

5.

Applicable over recommended operating temperature and voltage range unless otherwise noted.

| Table 7 | . 2.5V | LVDS | Driver | DC/AC | Charac | teris | sti | CS |  |

|---------|--------|------|--------|-------|--------|-------|-----|----|--|

|         |        |      |        |       |        |       |     |    |  |

|         |        | _    |        |       |        | _     |     | -  |  |

| Symbol            | Parameter                           | Test Condition                   | Min. | Max. | Units | Comments               |

|-------------------|-------------------------------------|----------------------------------|------|------|-------|------------------------|

| T <sub>A</sub>    | Operating Temperature               | -                                | -55  | 125  | °C    | -                      |

| V <sub>DD</sub>   | Supply Voltage                      | Core                             | 2.3  | 2.7  | V     | -                      |

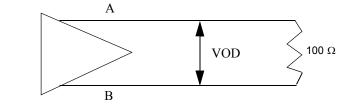

| VOD               | Output differential voltage         | Rload = $100\Omega$              | 247  | 454  | mV    | see Figure 4           |

| VOS               | Output offset voltage               | Rload = $100\Omega$              | 622  | 1375 | mV    | see Figure 4           |

| Delta VOD <br>(1) | Change in  VOD                      | Rload = 100Ω                     | 0    | 50   | mV    | see Figure 4           |

| Delta VOS         | Change in VOS: Steady-state         | Rload = $100\Omega$              | 0    | 50   | mV    | -                      |

| (1)               | Change in VOS: Dynamic state        |                                  | 0    | 100  | mV    | _                      |

| ISA, ISB          | Output current                      | Drivers shorted to ground or VDD | 1.0  | 6.3  | mA    | -                      |

| ISAB              | Output current                      | Drivers shorted together         | 2.4  | 4.8  | mA    | -                      |

| Rbias             | Bias resistor                       | -                                | 9.8  | 10.2 | KΩ    | 1 per chip             |

| Ibias             | Bias static current                 | -                                | 5.8  | 11.7 | mA    |                        |

| F Max             | Maximum operating frequency         | VDD = 2.5V ± 0.2V                | -    | 180  | MHz   | Consumption<br>14.8 mA |

| Clock             | Clock signal duty cycle             | Max. frequency                   | 45   | 55   | %     | -                      |

| Tfall             | Fall time 80-20%                    | Rload = $100\Omega$              | 669  | 1178 | ps    | see Figure 4           |

| Trise             | Rise time 20-80%                    | Rload = $100\Omega$              | 670  | 1167 | ps    | see Figure 4           |

| Тр                | Propagation delay                   | Rload = $100\Omega$              | 1270 | 2660 | ps    | see Figure 4           |

| Tsk1              | Duty cycle skew                     | Rload = $100\Omega$              | 0    | 110  | ps    | -                      |

| Tsk2              | Channel to channel skew (same edge) | Rload = 100Ω                     | 0    | 50   | ps    | -                      |

(1) Parameter guaranteed by design, not tested

| Symbol            | Parameter                           | Test Condition                   | Min. | Max. | Units | Comments               |

|-------------------|-------------------------------------|----------------------------------|------|------|-------|------------------------|

| T <sub>A</sub>    | Operating Temperature               | -                                | -55  | 125  | ۰C    | -                      |

| V <sub>DD</sub>   | Supply Voltage                      | Core                             | 2.7  | 3.3  | V     | -                      |

| VOD               | Output differential voltage         | Rload = $100\Omega$              | 247  | 454  | mV    | see Figure 4           |

| VOS               | Output offset voltage               | Rload = $100\Omega$              | 622  | 1375 | mV    | see Figure 4           |

| Delta VOD <br>(1) | Change in  VOD                      | Rload = 100Ω                     | 0    | 50   | mV    | -                      |

| Delta VOS         | Change in VOS: Steady-state         | Rload = 100Ω                     | 0    | 50   | mV    | _                      |

| (1)               | Change in VOS: Dynamic state        | *                                | 0    | 150  | mV    | -                      |

| ISA, ISB          | Output current                      | Drivers shorted to ground or VDD | 1.0  | 6.3  | mA    | -                      |

| ISAB              | Output current                      | Drivers shorted together         | 2.6  | 5    | mA    | -                      |

| Rbias             | Bias resistor                       | -                                | 12.8 | 13.2 | ΚΩ    | 1 per chip             |

| Ibias             | Bias static current                 | -                                | 6.5  | 13.8 | mA    | -                      |

| F Max.            | Maximum operating frequency         | VDD = 3V ± 0.3V                  | -    | 200  | MHz   | Consumption<br>18.6 mA |

| Clock             | Clock signal duty cycle             | Max. frequency                   | 45   | 55   | %     | -                      |

| Tfall             | Fall time 80-20%                    | Rload = 100Ω                     | 512  | 968  | ps    | see Figure 4           |

| Trise             | Rise time 20-80%                    | Rload = $100\Omega$              | 512  | 970  | ps    | see Figure 4           |

| Тр                | Propagation delay                   | Rload = $100\Omega$              | 1150 | 2300 | ps    | see Figure 4           |

| Tsk1              | Duty cycle skew                     | Rload = $100\Omega$              | 0    | 70   | ps    | _                      |

| Tsk2              | Channel to channel skew (same edge) | Rload = 100Ω                     | 0    | 50   | ps    | -                      |

#### Table 8. 3V LVDS Driver DC/ AC Characteristics

(1) Parameter guaranteed by design, not tested

Table 9. 3.3V LVDS Driver DC/ AC Characteristics

| Symbol            | Parameter                   | Test Condition      | Min. | Max. | Units | Comments     |

|-------------------|-----------------------------|---------------------|------|------|-------|--------------|

| T <sub>A</sub>    | Operating Temperature       | -                   | -55  | 125  | °C    | -            |

| V <sub>DD</sub>   | Supply Voltage              | -                   | 3    | 3.6  | V     | -            |

| VOD               | Output differential voltage | Rload = $100\Omega$ | 247  | 454  | mV    | see Figure 4 |

| VOS               | Output offset voltage       | Rload = $100\Omega$ | 622  | 1375 | mV    | see Figure 4 |

| Delta VOD <br>(1) | Change in  VOD              | Rload = 100Ω        | 0    | 50   | mV    | -            |

| Symbol                                      | Parameter                           | Test Condition                   | Min. | Max. | Units | Comments               |

|---------------------------------------------|-------------------------------------|----------------------------------|------|------|-------|------------------------|

| Delta VOS                                   | Change in VOS: Steady-state         | Rload = 100Ω                     | 0    | 50   | mV    | -                      |

| (1)                                         | Change in VOS: Dynamic state        |                                  | 0    | 200  | mV    | _                      |

| Delta VOD                                   | Change in  VOD  between "0" and "1" | Rload = 100Ω                     | 0    | 50   | mV    | _                      |

| Delta VOS                                   | Change in  VOS  between "0" and "1" | Rload = 100Ω                     | 0    | 200  | mV    | _                      |

| ISA, ISB                                    | Output current                      | Drivers shorted to ground or VDD | 1.0  | 6.2  | mA    | -                      |

| ISAB                                        | Output current                      | Drivers shorted together         | 2.6  | 4.8  | mA    | _                      |

| Rbias                                       | Bias resistor                       | -                                | 16.3 | 16.7 | kΩ    | 1 per chip             |

| Ibias                                       | Bias static current                 | -                                | 7    | 14.6 | mA    | _                      |

| F Max.                                      | Maximum operating frequency         | VDD = 3.3V ± 0.3V                | _    | 220  | MHz   | Consumption<br>20.9 mA |

| Clock                                       | Clock signal duty cycle             | Max. frequency                   | 45   | 55   | %     | _                      |

| Tfall                                       | Fall time 80-20%                    | Rload = $100\Omega$              | 445  | 838  | ps    | see Figure 4           |

| Trise                                       | Rise time 20-80%                    | Rload = $100\Omega$              | 445  | 841  | ps    | see Figure 4           |

| Тр                                          | Propagation delay                   | Rload = $100\Omega$              | 1120 | 2120 | ps    | see Figure 4           |

| Tsk1                                        | Duty cycle skew                     | Rload = $100\Omega$              | 0    | 80   | ps    | -                      |

| Tsk2 Channel to channel skew<br>(same edge) |                                     | Rload = 100Ω                     | 0    | 50   | ps    | _                      |

| Table 9. | 3.3V LVDS Driver DC/ AC Characteristics |

|----------|-----------------------------------------|

|----------|-----------------------------------------|

Figure 4. Test Termination Measurements

$$VOS = \frac{(VA + VB)}{2}$$

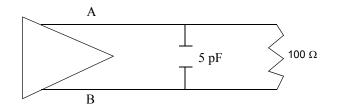

Figure 5. Rise and Fall Measurements

#### Table 10. LVDS Receiver DC/ AC Characteristics

| Symbol          | Parameter                  | Test Condition                      | Min. | Max. | Units | Comments |

|-----------------|----------------------------|-------------------------------------|------|------|-------|----------|

| T <sub>A</sub>  | Operating Temperature      | -                                   | -55  | 125  | ٠C    | _        |

| V <sub>DD</sub> | Supply Voltage             | -                                   | 2.3  | 3.6  | V     | _        |

| Vi              | Input voltage range        | -                                   | 0    | 2400 | mV    | _        |

| Vidth           | Input differential voltage | -                                   | -100 | +100 | mV    | -        |

|                 |                            | Cout = 50 pF, VDD = 2.5V ± 0.2V     | 0.9  | 3.5  |       |          |

|                 |                            | Cout = 50 pF, VDD = $3.0V \pm 0.3V$ | 0.7  | 2.7  | ns    | -        |

| Тр              | Propagation delay          | Cout = 50 pF, VDD = $3.3V \pm 0.3V$ | 0.7  | 2.4  |       |          |

| Tskew           | Duty cycle distortion      | Cout = 50 pF                        | -    | 500  | ps    | _        |

#### Table 11. I/O Buffers DC Characteristics

| Symbol           | Parameter Test Condition         |    | Typical | Units |

|------------------|----------------------------------|----|---------|-------|

| C <sub>IN</sub>  | Capacitance, Input Buffer (die)  | 3V | 2.4     | pF    |

| C <sub>OUT</sub> | Capacitance, Output Buffer (die) | 3V | 5.6     | pF    |

| C <sub>I/O</sub> | Capacitance, Bi-Directional      | 3V | 6.6     | pF    |

## Testability Techniques

For complex designs, involving blocks of memory and/or cores, careful attention must be given to design-for-test techniques. The sheer size of complex designs and the number of functional vectors that would need to be created to exercise them fully, strongly suggests the use of more efficient techniques. Combinations of SCAN paths, multiplexed access to memory and/or core blocks, and built-in-self-test logic must be employed, in addition to functional test patterns, to provide both the user and Atmel the ability to test the finished product.

An example of a highly complex design could include a PLL for clock management or synthesis, a microcontroller or DSP engine or both, SRAM to support the microcontroller or DSP engine, and glue logic to support the interconnectivity of each of these blocks. The design of each of these blocks must take into consideration the fact that the manufactured device will be tested on a high performance digital tester. Combinations of parametric, functional, and structural tests, defined for digital testers, should be employed to create a suite of manufacturing tests.

The type of block dictates the type of testability technique to be employed. The PLL will, by construction, provide access to key nodes so that functional and/or parametric testing can be performed. Since a digital tester must control all the clocks during the testing of a Gate Array/Embedded Array, provision must be made for the VCO to be bypassed. Atmel's PLLs include a multiplexing capability for just this purpose. The addition of a few pins will allow other portions of the PLL to be isolated for test, without impinging upon the normal functionality.

In a similar vein, access to microcontroller, DSP, and SRAM blocks must be provided so that controllability and observability of the inputs and outputs to the blocks are achieved with the minimum amount of preconditioning. SRAM blocks need to provide access to both address and data ports so that comprehensive memory tests can be performed. Multiplexing I/O pins provides a method for providing this accessibility.

The glue logic can be designed using full SCAN techniques to enhance its testability.

It should be noted that, in almost all of these cases, the purpose of the testability technique is to provide Atmel a means to assess the structural integrity of a Gate Array/Embedded Array, i.e., sort devices with manufacturing-induced defects. All of the techniques described above should be considered supplemental to a set of patterns which exercise the functionality of the design in its anticipated operating modes.

## Advanced Packaging

The MH1RT Series are offered in ceramic packages: multi-layer quad flat packs (MQFP), multi - layer column grid array (MCGA) and multi-layer land grid array (MLGA). Packages lid may be connected to ground or not.

#### Table 12. Packaging Options

| Package Type <sup>(1,2)</sup> | Pin Count                |

|-------------------------------|--------------------------|

| MQFP                          | 132,196, 256 and 352     |

| MCGA and MLGA                 | 349, 472 (1.27 mm pitch) |

Notes: 1. Contact Atmel local design centers to check the availability of the matrix/package combination. 2. Four decks packages.

| Document<br>Revision<br>History |          |                                                                           |

|---------------------------------|----------|---------------------------------------------------------------------------|

| 4110K - 11/07                   | 1.       | Added missing ESD information. See pages 1 & 8.                           |

| 4110L - 11/10                   | 1.<br>2. | Add LGA package option<br>Correction of LVDS transmitter tables (VOL/VOH) |

# 18 MH1RT

#### Headquarters

*Atmel Corporation* 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com *Technical Support* Enter Product Line E-mail Sales Contact www.atmel.com/contacts

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2007 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.